电熔丝单元阵列的版图布局方法与流程

1.本发明涉及集成电路版图技术,特别涉及电熔丝单元阵列的版图布局方法。

背景技术:

2.电熔丝(efuse)基于电迁移(em)原理,通过熔断熔丝的原理,实现具备高可靠性的片上编程功能。随着市场对芯片面积的要求越来越高,电熔丝(efuse)作为芯片内部用于参数设置的专用模块(ip),整体面积已经成为主要设计指标之一。而在电熔丝(efuse)模块内部,由电熔丝(efuse)单元构成的阵列占据整个模块面积的一半以上,因此减小电熔丝(efuse)单元阵列面积是提高电熔丝(efuse)模块竞争力的的主要手段之一。

3.在电熔丝(efuse)版图设计时,电熔丝(efuse)单元组成的阵列占整体面积的一半以上。电熔丝(efuse)单元由熔丝和选择管构成。常规设计中,阵列面积是由独立电熔丝(efuse)单元面积拼接而成,也就是单个电熔丝(efuse)单元面积与单元数的乘积。

4.参阅图1a所示,现有技术的电熔丝的存储区域是由电熔丝单元阵列构成,如图1所示,其中,阵列中的存储单元既有以独立电熔丝单元的组合形式出现,这种布置方式是为了方便版图设计以及不同容量的组合。

5.参阅图1b所示,现有技术的一种电熔丝布局的版图中,存在一个电熔丝单元01。电熔丝阵列的总面积=单个电熔丝单元版图面积x行数x列数。参阅1c所示,采用由2个独立的电熔丝单元01直接拼接而来的单元对为基本单位形式,可以共用和节省外围的走线。图1d展示了图1c中的两个独立的电熔丝单元01的其中一个电熔丝、晶体管通路示意图,为图1b中实线框中的展示,采用带箭头的线表示了通路的情况。参阅图1e所示,以28nm工艺平台的电熔丝单元为例,其nmos管与电熔丝面积为14.4μm2,两个单元组合面积是28.8μm2。

6.现有技术存在的问题在于:从版图面积和效率上,上述两种方式并不是最优化的。

技术实现要素:

7.本发明需要解决的技术问题是:如何进一步减小版图面积,提高版图面积利用效率。

8.为了解决以上技术问题,本发明提供一种电熔丝单元阵列的版图布局方法,其目的在于改进电熔丝单元阵列的版图方法,减小电熔丝模块的面积。

9.为了达到上述目的,本发明提供了一种电熔丝单元阵列的版图布局方法,包含:电熔丝单元对结构,其包含,二个电熔丝晶体管单元;第一电熔丝晶体管单元包含:第一晶体管和第一电熔丝单元;第二电熔丝晶体管单元包含:第二晶体管和第二电熔丝单元;第一电熔丝单元跨接在第一晶体管和第二晶体管上;第二电熔丝单元跨接在第二晶体管和第一晶体管上。

10.优选地,第一电熔丝单元包含第一阳极垫、第一熔丝、第一阴极垫,第一熔丝两端连接第一阳极垫和第一阴极垫;

第二电熔丝单元包含第二阳极垫、第二熔丝、第二阴极垫,第二熔丝两端连接第二阳极垫和第二阴极垫;第一阳极垫-第一熔丝-第一阴极垫平行于第二阴极垫-第二熔丝-第二阳极垫沿第一方向布置,在垂直于第一方向的第二方向上,第一阳极垫对准第二阴极垫,第一阴极垫对准第二阳极垫。

11.优选地,第一阳极垫位于第二晶体管处,第一阴极垫位于第一晶体管处;第二阳极垫位于第一晶体管处,第二阴极垫位于第二晶体管处;第一晶体管和第二晶体管交叉对称布置。

12.优选地,第一晶体管和第二晶体管为mos管。

13.优选地,第一晶体管和第二晶体管为nmos管。

14.优选地,第一阳极垫、第一阴极垫成板状,第一熔丝成条状,第一阳极垫、第一阴极垫的宽度远大于第一熔丝的宽度;第二阳极垫、第二阴极垫成板状,第二熔丝成条状,第二阳极垫、第二阴极垫的宽度远大于第二熔丝的宽度。

15.优选地,第一阳极垫、第二阳极垫采用第三金属层形成;第一熔丝、第二熔丝采用第二金属层形成;第一阴极垫、第二阴极垫采用第二金属层形成;第一阳极垫通过第一连通孔从第三金属层连接到第一熔丝的第二金属层;第二阳极垫通过第二连通孔从第三金属层连接到第二熔丝的第二金属层。

16.优选地,第二金属层沿着第一方向布置,第三金属层沿着第二方向布置;第一位线、第二位线分别通过第三金属层形成;字线通过第二金属层形成。

17.优选地,形成的等效电路,包含:位于第三金属层的第一位线与位于第三金属层的第一阳极垫相连,通过第一连通孔与位于第二金属层的第一熔丝相连,再连接到位于第二金属层的第一阴极垫;位于第三金属层的第二位线与位于第三金属层的第二阳极垫相连,通过第二连通孔与位于第二金属层的第二熔丝相连,再连接到位于第二金属层的第二阴极垫;第一阳极垫位于第一晶体管处,第一阴极垫位于第二晶体管处;第二阳极垫位于第二晶体管处,第二阴极垫位于第一晶体管处;第一晶体管和第二晶体管交叉对称布置;第一晶体管、第二晶体管的源极、漏极、栅极都采用第二金属层形成连接;形成的等效电路,还包含:第一晶体管的源极或漏极连接第一阴极垫,第一晶体管的漏极或源极接地,第一晶体管的栅极连接字线;第二晶体管的源极或漏极连接第二阴极垫,第二晶体管的漏极或源极接地,第二晶体管的栅极连接字线。

18.优选地,将本方法提供的电熔丝单元对结构阵列,形成了整体集成电路。

19.与现有技术相比,本发明提供了一种电熔丝单元阵列的版图布局方法,包含:电熔

丝单元对结构,其包含,二个电熔丝单元;第一电熔丝单元中包含第一晶体管和第一电熔丝单元;第二电熔丝单元中包含第二晶体管和第二电熔丝单元;第一电熔丝单元跨接在第一晶体管和第二晶体管上;第二电熔丝单元跨接在第二晶体管和第一晶体管上。据此,本发明能够达到的技术效果在于,能够在各项性能不变的情况下比现有技术的版图面积减小。

附图说明

20.图1a展示了现有技术的电熔丝布置一实施例的集成电路布局图。

21.图1b展示了现有技术的电熔丝布置又一实施例的集成电路布局图。

22.图1c展示了图1b中集成电路布局所采用的两个电熔丝单元作为基本单元。

23.图1d展示了图1b中的两个电熔丝单元中的一个电熔丝、晶体管通路示意图。

24.图1e展示了图1b中的电熔丝单元在28nm技术节点工艺平台的一个电熔丝和一个晶体管的所占版图面积示意图。

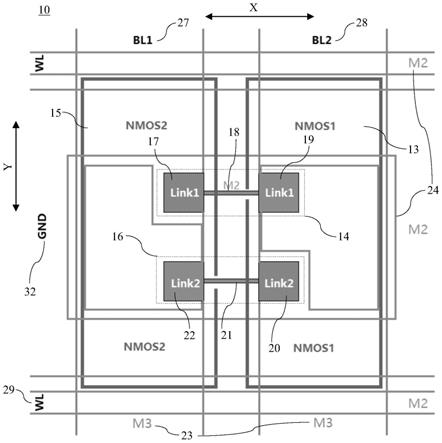

25.图2a示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构中一对电熔丝的布置示意图。

26.图2b示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构的布置的等效电路图。

27.图3a示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构的布置示意图。

28.图3b示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构的布置的等效电路图。

29.图3c示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构中的一个电熔丝、晶体管通路示意图。

30.图3d示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构中的一个电熔丝、晶体管通路的等效电路示意图。

31.附图标记说明。

32.现有技术:01

ꢀꢀꢀꢀ

电熔丝单元;本发明:10

ꢀꢀꢀꢀ

电熔丝单元对结构11

ꢀꢀꢀꢀ

第一电熔丝晶体管单元12

ꢀꢀꢀꢀ

第二电熔丝晶体管单元13

ꢀꢀꢀꢀ

第一晶体管14

ꢀꢀꢀꢀ

第一电熔丝单元15

ꢀꢀꢀꢀ

第二晶体管16

ꢀꢀꢀꢀ

第二电熔丝单元17

ꢀꢀꢀꢀ

第一阳极垫18

ꢀꢀꢀꢀ

第一熔丝19

ꢀꢀꢀꢀ

第一阴极垫20

ꢀꢀꢀꢀ

第二阳极垫

21

ꢀꢀꢀꢀ

第二熔丝22

ꢀꢀꢀꢀ

第二阴极垫23

ꢀꢀꢀꢀ

第三金属层24

ꢀꢀꢀꢀ

第二金属层25

ꢀꢀꢀꢀ

第一连通孔26

ꢀꢀꢀꢀ

第二连通孔27

ꢀꢀꢀꢀ

第一位线28

ꢀꢀꢀꢀ

第二位线29

ꢀꢀꢀꢀ

字线30

ꢀꢀꢀꢀ

第一晶体管的源极或漏极31

ꢀꢀꢀꢀ

第一晶体管的漏极或源极32

ꢀꢀꢀꢀ

地33

ꢀꢀꢀꢀ

第一晶体管的栅极34

ꢀꢀꢀꢀ

第二晶体管的源极或漏极35

ꢀꢀꢀꢀ

第二晶体管的漏极或源极36

ꢀꢀꢀꢀ

第二晶体管的栅极。

具体实施方式

33.以下结合附图对本发明的具体实施方式进行详细说明。

34.参阅图2a和3a所示,本发明提供的一种电熔丝单元阵列的版图布局方法,包含:电熔丝单元对结构10。电熔丝单元对结构10包含:二个电熔丝晶体管单元11、12。第一电熔丝晶体管单元11包含:第一晶体管13和第一电熔丝单元14。第二电熔丝晶体管单元12包含:第二晶体管15和第二电熔丝单元16。第一电熔丝单元14跨接在第一晶体管13和第二晶体管15上。第二电熔丝单元16跨接在第二晶体管15和第一晶体管13上。

35.第一电熔丝单元14(link1)包含:第一阳极垫17(pad垫)、第一熔丝18、第一阴极垫19(pad垫),第一熔丝18两端连接第一阳极垫17和第一阴极垫19。

36.第二电熔丝单元16(link2)包含第二阳极垫20(pad垫)、第二熔丝21、第二阴极垫22(pad垫),第二熔丝21两端连接第二阳极垫20和第二阴极垫22。

37.第一阳极垫17-第一熔丝18-第一阴极垫19平行于第二阴极垫22-第二熔丝21-第二阳极垫20沿第一方向x布置。第一方向x也是第一熔丝18、第二熔丝21的长度方向。

38.在垂直于第一方向x的第二方向y上,第一阳极垫17对准第二阴极垫22,第一阴极垫19对准第二阳极垫20。

39.第一阳极垫17位于第二晶体管15处,第一阴极垫19位于第一晶体管13处。

40.第二阳极垫20位于第一晶体管13处,第二阴极垫22位于第二晶体管15处。

41.第一晶体管13和第二晶体管15交叉对称布置。

42.第一晶体管13和第二晶体管15为mos管。

43.第一晶体管13和第二晶体管15为nmos管(分别为nmos1、nmos2)。nmos管作为选择管。

44.第一阳极垫17、第一阴极垫19成板状,第一熔丝18成条状,第一阳极垫17、第一阴

极垫19的宽度远大于第一熔丝18的宽度。

45.第二阳极垫20、第二阴极垫22成板状,第二熔丝21成条状,第二阳极垫20、第二阴极垫22的宽度远大于第二熔丝21的宽度。据此,在金属层厚度相同情况下,电熔丝的单位长度的截面积更小, 单位长度的电阻更大,用以熔断。

46.第一阳极垫17、第二阳极垫20采用第三金属层23(m3)形成。

47.第一熔丝18、第二熔丝21采用第二金属层24(m2)形成。

48.第一阴极垫19、第二阴极垫22采用第二金属层24(m2)形成。

49.第一阳极垫17通过第一连通孔25(via)从第三金属层23连接到第一熔丝18的第二金属层24。

50.第二阳极垫20通过第二连通孔26(via)从第三金属层23连接到第二熔丝18的第二金属层24。

51.第二金属层24沿着第一方向x布置。第三金属层23沿着第二方向y布置。

52.第一位线27(bl1)、第二位线28(bl2)分别通过第三金属层23形成。

53.字线29(wl)通过第二金属层24形成。

54.参阅图2b所示,形成的等效电路,包含,如下所述。

55.位于第三金属层的第一位线27与位于第三金属层的第一阳极垫17相连,通过第一连通孔25与位于第二金属层的第一熔丝18相连,再连接到位于第二金属层的第一阴极垫19。

56.位于第三金属层的第二位线28与位于第三金属层的第二阳极垫20相连,通过第二连通孔26与位于第二金属层的第二熔丝21相连,再连接到位于第二金属层的第二阴极垫22。

57.第一阳极垫17位于第二晶体管15处,第一阴极垫19位于第一晶体管13处。

58.第二阳极垫20位于第一晶体管13处,第二阴极垫22位于第二晶体管15处。

59.第一晶体管13和第二晶体管15交叉对称布置。

60.第一晶体管13、第二晶体管15的源极、漏极、栅极都采用第二金属层24形成连接。

61.参阅图3b所示,形成的等效电路,还包含,如下所述。

62.第一晶体管的源极或漏极30连接第一阴极垫19,第一晶体管的漏极或源极31接地32(gnd),第一晶体管的栅极33连接字线29。

63.第二晶体管的源极或漏极34连接第二阴极垫22,第二晶体管的漏极或源极35接地32(gnd),第二晶体管的栅极36连接字线29。

64.将本方法提供的电熔丝单元对结构阵列,形成了整体集成电路。

65.电熔丝单元阵列的版图布局方法可以应用于存储器(memory),已通过技术鉴定车(tqv,technology qualification vehicle)测试验证,是一种较优化的模块(ip)。

66.图3c示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构中的一个电熔丝、晶体管通路示意图。图3d示出了本发明提供的电熔丝单元阵列的版图布局方法中提供的电熔丝单元对结构中的一个电熔丝、晶体管通路的等效电路示意图。图3c和图3d带箭头的线表示了通路的情况,经过的是第一熔丝单元14和第一晶体管13,依次经过第一位线27、第一阳极垫17、第一熔丝18、第一阴极垫19、第一晶体管13、第二金属层24处形成的地、字线29等。

67.以上即为本发明所提供的电熔丝单元阵列的版图布局方法的具体实施例。据此,本发明能够达到的技术效果在于,与图1e所示的现有技术的第二实施例的电子电熔丝单元阵列的布置相比,从晶体管和电熔丝单元独立布置,改为交互布置,从而使得在28nm工艺平台中,本发明的图3a所示的电熔丝单元对结构,在同样实现存储2个比特(位,bit)信息的能力(对应于现有技术图1e中两个图示面积区域),实际版图面积减小25%。

68.上述具体实施例和附图说明仅为例示性说明本发明的技术方案及其技术效果,而非用于限制本发明。任何熟于此项技术的本领域技术人员均可在不违背本发明的技术原理及精神的情况下,在权利要求保护的范围内对上述实施例进行修改或变化,均属于本发明的权利保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1