硬件计算模拟方法、系统及计算机可读存储介质与流程

1.本发明涉及深度学习技术领域,尤其涉及一种硬件计算模拟方法、系统及计算机可读存储介质。

背景技术:

2.随着深度学习和ai芯片的迅速发展,深度学习系统通常比较复杂,而且各种框架和硬件设备都存在独特的体系结构,这使得深度学习的开发环境部署、测试以及迭代改进准确性和性能调优等方面的工作变得繁琐耗时,为了优化上述流程,引入了深度学习推理框架。

3.目前常见的推理框架主要有mnn/ncnn/tnn等开源深度学习推理框架,这类开源深度学习推理框架可以支持市面上常见的硬件设备,对于一些具有独特设计和优化的硬件设备,使用开源深度学习推理框架可能会产生算子不支持、精度损失等推理框架不适配的问题,无法完全模拟硬件设备的性能和优势。

4.上述内容仅用于辅助理解本发明的技术方案,并不代表承认上述内容是现有技术。

技术实现要素:

5.本发明的主要目的在于提供一种硬件计算模拟方法、系统及计算机可读存储介质,旨在解决对于一些具有独特设计和优化的硬件设备,使用开源深度学习硬件计算模拟系统可能会产生算子不支持、精度损失等硬件计算模拟系统不适配的问题,旨在提高模拟硬件设备计算的适配度和精准度。

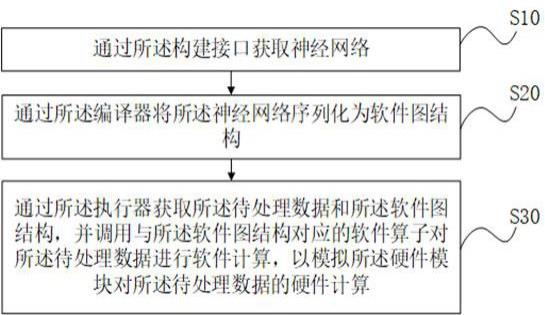

6.为实现上述目的,本发明提供一种硬件计算模拟方法,应用于硬件计算模拟系统,所述硬件计算模拟系统包括构建接口、编译器和执行器,所述构建接口与所述编译器连接,所述编译器与所述执行器连接,所述执行器用于调用软件算子或者硬件模块对待处理数据进行计算,所述硬件计算模拟方法包括:通过所述构建接口获取神经网络;通过所述编译器将所述神经网络序列化为软件图结构;通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算。

7.可选地,所述编译器包括硬件编译单元,所述通过所述编译器将所述神经网络序列化为软件图结构的步骤之后,还包括:通过所述硬件编译单元将所述软件图结构序列化为硬件图结构;通过所述执行器获取所述待处理数据和所述硬件图结构,并调用所述硬件模块对所述待处理数据进行所述硬件计算。

8.可选地,所述通过所述硬件编译单元将所述软件图结构序列化为硬件图结构的步

骤包括:若所述硬件图结构对应的算子中含有软件算子,则在所述硬件图结构中增加相应的数据拷贝算子。

9.可选地,所述若所述硬件图结构对应的算子中含有软件算子,则在所述硬件图结构中增加相应的数据拷贝算子的步骤包括:在所述硬件图结构对应的算子中的软件算子前增加第一数据拷贝算子,以将所述待处理数据从所述硬件模块中拷贝到所述软件算子所在的内存中,并调用相应的软件算子对所述待处理数据进行软件计算。

10.可选地,所述若所述硬件图结构对应的算子中含有软件算子,则在所述硬件图结构中增加相应的数据拷贝算子的步骤包括:在所述硬件图结构对应的算子中的软件算子后增加第二数据拷贝算子,以将所述待处理数据从所述硬件模块中拷贝到所述软件算子所在的内存中,并调用所述硬件模块对所述待处理数据进行软件计算。

11.可选地,所述通过所述编译器将所述神经网络序列化为软件图结构的步骤包括:获取所述神经网络的组件与所述软件算子之间的预设关系;根据所述预设关系将所述神经网络序列化为所述软件图结构。

12.可选地,所述通过所述构建接口获取神经网络的步骤之前,还包括:当接收到上层编译器的调用指令时,接受所述上层编译器的调用;通过所述构建接口获取所述上层编译器构建的神经网络。

13.此外,为实现上述目的,本发明还提供一种硬件计算模拟系统,所述硬件计算模拟系统包括:构建模块,用于通过构建接口获取神经网络;编译模块,用于通过编译器将所述神经网络序列化为软件图结构;执行模块,用于通过执行器获取待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟硬件模块对所述待处理数据的硬件计算。

14.此外,为实现上述目的,本发明还提供一种硬件计算模拟系统,所述硬件计算模拟系统包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的硬件计算模拟程序,所述硬件计算模拟程序被所述处理器执行时实现如上述的硬件计算模拟方法的步骤。

15.此外,为实现上述目的,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有硬件计算模拟程序,所述硬件计算模拟程序被处理器执行时实现如上述的硬件计算模拟方法的步骤。

16.本发明实施例提出的一种硬件计算模拟方法、系统及计算机可读存储介质,所述硬件计算模拟方法应用于硬件计算模拟系统,首先通过所述构建接口获取神经网络;通过所述编译器将所述神经网络序列化为软件图结构;通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算。通过将神经网络序列化为软件算子组成的软件图结构,在调用相应的软件算子来模拟硬件模块的硬件计算,与传统的硬件

计算模拟方法相比,本发明实施例提出的硬件计算模拟方法支持具有独特设计和优化的硬件设备,解决传统的推理框架在模拟硬件设备计算过程时算子不支持、精度损失等问题,提高了模拟硬件设备计算时的适配度和准确性。

附图说明

17.图1是本发明实施例方案涉及的硬件运行环境的终端结构示意图;图2为本发明硬件计算模拟方法的一实施例的流程示意图;图3为本发明硬件计算模拟方法的另一实施例的流程示意图;图4为本发明硬件计算模拟方法涉及的神经网络基本组件示意图;图5为本发明硬件计算模拟方法涉及的软件图结构基本组件示意图;图6为本发明硬件计算模拟方法涉及的硬件图结构基本组件示意图;图7为本发明硬件计算模拟方法涉及的软件算子计算流程示意图;图8为本发明实施例涉及的硬件计算模拟系统的模块化示意图。

18.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

19.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

20.由于在相关技术中,mnn/ncnn/tnn等开源深度学习推理框架,可支持市面上常见的硬件设备,但是对于一些具有独特设计和优化的硬件设备,使用开源深度学习推理框架可能会产生算子不支持、精度损失等推理框架不适配的问题,无法完全模拟硬件设备的性能特点和优势,无法为在硬件设备的设计阶段提供准确的测试支持。

21.为了提高模拟硬件设备计算的适配性和准确性,本发明实施例提出了一种硬件计算模拟方法、系统及计算机可读存储介质,其中,所述方法的主要步骤包括:通过所述构建接口获取神经网络;通过所述编译器将所述神经网络序列化为软件图结构;通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算。

22.这样通过将神经网络序列化为软件图结构,并调用软件图结构对应的软件算子对待处理数据进行软件计算,实现了对硬件设备计算过程的模拟,提高了模拟的适配性和准确性。

23.以下结合附图对本发明权利要求要求保护的内容进行详细说明。

24.如图1所示,图1是本发明实施例方案涉及的硬件运行环境的终端结构示意图。

25.本发明实施例终端上可以运行硬件计算模拟系统。

26.如图1所示,该终端可以包括:处理器1001,例如cpu,存储器1003,通信总线1002。其中,通信总线1002用于实现这些组件之间的连接通信。存储器1003可以是高速ram存储器,也可以是稳定的存储器(non-volatile memory),例如磁盘存储器。存储器1003可选的还可以是独立于前述处理器1001的存储装置。

27.本领域技术人员可以理解,图1中示出的终端结构并不构成对终端的限定,可以包

括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

28.如图1所示,作为一种计算机存储介质的存储器1003中可以包括操作系统以及硬件计算模拟程序。

29.在图1所示的终端中,处理器1001可以用于调用存储器1003中存储的硬件计算模拟程序,并执行以下操作:通过所述构建接口获取神经网络;通过所述编译器将所述神经网络序列化为软件图结构;通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算。

30.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:通过所述硬件编译单元将所述软件图结构序列化为硬件图结构;通过所述执行器获取所述待处理数据和所述硬件图结构,并调用所述硬件模块对所述待处理数据进行所述硬件计算。

31.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:若所述硬件图结构对应的算子中含有软件算子,则在所述硬件图结构中增加相应的数据拷贝算子。

32.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:在所述硬件图结构对应的算子中的软件算子前增加第一数据拷贝算子,以将所述待处理数据从所述硬件模块中拷贝到所述软件算子所在的内存中,并调用相应的软件算子对所述待处理数据进行软件计算。

33.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:在所述硬件图结构对应的算子中的软件算子后增加第二数据拷贝算子,以将所述待处理数据从所述硬件模块中拷贝到所述软件算子所在的内存中,并调用所述硬件模块对所述待处理数据进行软件计算。

34.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:获取所述神经网络的组件与所述软件算子之间的预设关系;根据所述预设关系将所述神经网络序列化为所述软件图结构。

35.进一步地,处理器1001可以调用存储器1003中存储的硬件计算模拟程序,还执行以下操作:当接收到上层编译器的调用指令时,接受所述上层编译器的调用;通过所述构建接口获取所述上层编译器构建的神经网络。

36.随着深度学习和ai芯片的迅速发展,深度学习系统通常比较复杂,而且各种深度学习框架和硬件设备都存在独特的体系结构,这使得深度学习的开发环境部署、测试以及

迭代改进准确性和性能调优等方面的工作变得繁琐耗时,为了模拟深度学习的计算流程,引入了深度学习推理框架。

37.目前常见的深度学习推理框架有很多,主要分为两类。一类是硬件厂商针对自己特定硬件开发的推理框架,例如:英特尔的openvino,英伟达的tensorrt,谷歌的mediapipe等。其中,openvino和tensorrt可以支持tensorflow、pytorch、mxnet、caffe等主流深度学习框架的模型格式,而mediapipe仅支持tensorflow深度学习框架的模型格式,openvino、tensorrt和mediapipe这一类框架虽然性能较好,但支持的硬件平台单一,多是支持自研硬件平台。另一类是mnn/ncnn/tnn等开源深度学习推理框架,可支持tensorflow、pytorch、mxnet、caffe等多种训练框架,但这类开源深度学习推理框架都自定义了一套模型格式,不可避免的要是用各框架提供的转换器,并且对于一些具有独特设计和优化的硬件设备,或者是一些自研算子,使用开源框架可能会导致算子不支持,精度损失等问题,无法发挥自研硬件平台的全部性能特点和优势,不能完全为硬件设备提供准确的运行测试。

38.由此可见,在相关硬件计算模拟方法中,存在上述缺陷。本发明实施例为解决上述缺陷,提出一种应用于硬件计算模拟系统的硬件计算模拟方法,旨在解决对于一些具有独特设计和优化的硬件设备,使用开源深度学习推理框架可能会产生算子不支持、精度损失等推理框架不适配的问题,提高了模拟硬件设备计算时的适配度和精准度。

39.以下,通过具体示例性方案对本发明权利要求要求保护的内容,进行解释说明,以便本领域技术人员更好地理解本发明权利要求的保护范围。可以理解的是,以下示例性方案不对本发明的保护范围进行限定,仅用于解释本发明。

40.示例性地,参照图2,在本发明硬件计算模拟方法的一实施例中,所述硬件计算模拟方法包括以下步骤:s10、通过所述构建接口获取神经网络;本实施例中,执行硬件计算模拟方法的主体是硬件计算模拟系统,硬件计算模拟系统可以调度算子进行计算推理,硬件计算模拟系统包括构建接口、编译器和执行器,构建接口与编译器连接,编译器与执行器连接,所述执行器用于调用软件算子或者硬件模块对待处理数据进行计算,硬件模块包括硬件设备,可以是caisa芯片,caisa芯片是一款面向边缘和云端推理的人工智能芯片,caisa芯片可支持所有常用ai算子,通过数据流网络中算子的不同配置和组合,caisa芯片可支持绝大多数的cnn算法(convolutional neural networks 卷积神经网络)。构建接口是硬件计算模拟系统中较为上层的抽象接口,用于获取神经网络,神经网络是一种进行分布式并行信息处理的算法数学模型,通过调整内部大量节点之间相互连接的关系,从而达到处理信息的目的,通过构建窗口获取神经网络,如图4所示,图4是卷积神经网络mobilenet的基本组件,mobilenet是移动端或者嵌入式常用的卷积神经网络,是一种小巧而高效的cnn模型,其中,3

×

3depthwise conv(3

×

3深度卷积),bn(归一化),relu(激活函数),1

×

1 conv(1

×

1 卷积)为对待处理数据的计算流程。

41.可选地,构建接口可以接收上层编译器的调用,在构建接口获取神经网络的步骤之前,构建接口如果接收到上层编译器的调用指令,会接受上层编译器的调用,上层编译器可以是rainbuilder编译器,rainbuilder编译器是一个通用的端到端自动编译工具,rainbuilder编译器可以通过硬件计算模拟系统的构建接口构建神经网络,实现了rainbuilder编译器和硬件计算的解耦,降低了构建神经网络的难度,易于维护。

42.s20、通过所述编译器将所述神经网络序列化为软件图结构;本实施例中,硬件计算模拟系统的编译器与构建接口相连,位于构建接口的下层,当构建接口获取到神经网络后,将神经网络的组件序列化为软件图结构,软件图结构时纯软件算子的排布。

43.可选地,通过编译器将神经网络序列化为软件图结构的步骤包括:获取所述神经网络组件与所述软件算子之间的预设关系;根据所述预设关系将所述神经网络序列化为所述软件图结构。

44.神经网络组件与软件算子之间有对应的映射关系,可以预先设置映射关系,编译器在加载神经网络时,解析神经网络的组件,根据预设关系对应地确认神经网络对应的软件算子,并按照顺序将其排列为软件图结构。

45.参照图4和图5,图4是卷积神经网络mobilenet的基本组件,以单批次处理(single batch)为例,当硬件计算模拟系统的构建接口获取到神经网络mobilenet后,硬件计算模拟系统的编译器将神经网络mobilenet的基本组件表示为如图5所示的mobilenet软件图结构sw_graph,其中,op_m_gconv(深度二维卷积算子)、op_m_conv(二维卷积算子)为软件图结构对待处理数据的计算流程。

46.s30、通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算。

47.本实施例中,硬件计算模拟系统的执行器与编译器相连,位于编译器的下层,当编译器将神经网络序列化为软件图结构之后,获取待处理数据和软件图结构,根据软件图结构上的软件算子调用相应的软件算子对待处理数据进行计算,待处理数据可以是需要进行特征提取的图像,软件算子是可以模拟硬件模块的仿真算子,它的计算过程在cpu上完成,执行器可以调用cpu上的软件算子,软件算子部署简单,适合演示效果,执行器还可以调用硬件模块,硬件模块对待处理数据的计算迅速,适合实际运行生产场景。

48.当软件算子对待处理数据的进行计算时,计算过程和硬件模块对待处理数据的计算过程相同,可以通过软件计算模拟硬件模块,执行器调用的硬件模块可以是caisa芯片,通过本发明实施例提供的硬件计算模拟系统的执行器统一调度和优化,能够充分发挥caisa芯片数据流架构的计算性能优势,同时支持int8/int16量化精度模式。通过模拟硬件行为的算子计算能够在芯片设计阶段提供准确性验证的参考,能够与caisa芯片计算结果相互验证,进一步提高了验证和调试的效率。

49.在本实施例公开的技术方案中,先通过所述构建接口获取神经网络;通过所述编译器将所述神经网络序列化为软件图结构;通过所述执行器获取所述待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟所述硬件模块对所述待处理数据的硬件计算,通过将神经网络组件序列化为软件图结构,并根据软件图结构调用相应的软件算子对待处理数据进行软件计算,软件计算具有演示效果,可以模拟硬件对待处理数据的硬件计算,软件计算能够在芯片设计阶段提供准确性验证的参考,能够与caisa芯片计算结果相互验证,进一步提高了验证和调试的效率,本发明实施例提出的硬件计算模拟方法,不仅可以模拟硬件模块的硬件计算,而且对于一些具有独特设计和优化的硬件设备,或者是一些自研算子也能适配,可以充分发挥硬件模块

的性能和优势,为硬件模块的计算提供准确的运行测试,免去复杂的硬件环境安装和部署,提高了模拟硬件设备计算时的适配度和精准度。

50.可选地,参照图3,基于上述任一实施例,在本发明硬件计算模拟方法的另一实施例中,所述硬件计算模拟方法包括:s40、通过所述硬件编译单元将所述软件图结构序列化为硬件图结构;本实施例中,步骤s40在步骤s20之后进行,编译器不仅可以将神经网络序列化为软件图结构,编译器中还包括硬件编译单元,可以将软件图结构序列化为硬件图结构,硬件图结构会根据硬件特征和具体算子的特点进行拆分和融合等优化,使计算速度达到更快。

51.可选地,若所述硬件图结构对应的算子中含有软件算子,则在所述硬件图结构中增加相应的数据拷贝算子。

52.本实施例中的硬件计算模拟方法支持用户自定义软件算子,如果在硬件算子前后存在软件算子的情况下,需要相应地增加数据拷贝算子op_data_cpy,对待处理数据进行拷贝,具体地,将待处理数据从ddr(双倍速率同步动态随机存储器)拷贝到内存中,或者将待处理数据从内存中拷贝到ddr中。

53.具体地,在所述硬件图结构对应的算子中的软件算子前增加数据拷贝算子,以将所述待计算数据从所述硬件模块拷贝到所述软件算子所在的内存中,以使所述待计算数据可以进行软件计算。或者在所述硬件图结构对应的算子中的软件算子后增加数据拷贝算子,以将所述待计算数据从所述软件算子所在的内存拷贝到所述硬件模块中,以使所述待计算数据可以进行硬件计算。

54.可以理解的是,硬件模块中包括存储器,用于存储硬件计算需要用到的算子,可以是ddr,而软件算子则存储在cpu对应的内存中,在硬件图结构中可能会存在有软件算子,在硬件模块的存储器中不会存储有软件算子,则无法根据硬件图结构在硬件模块上完成硬件算子,所以在硬件图结构中的软件算子前增加数据拷贝算子,可以将待处理数据从ddr拷贝到内存中,调用对应软件算子,在cpu上完成硬件图结构中软件算子的计算,如果软件算子后还有需要在硬件模块上进行的计算,则在硬件图结构中的软件算子后增加数据拷贝算子,将待处理数据从内存拷贝到ddr中,继续在硬件模块中对待处理数据进行硬件计算。

55.参照图5和图6,图5是神经网络mobilenet软件图结构sw_graph,图6是神经网络mobilenet软件图结构sw_graph经过编译器中的硬件编译模块序列化后的硬件图结构hw_graph,在图6中,op_m_gconv_hw(深度二维卷积算子)、op_m_gconv_hw(二维卷积算子)为硬件图结构对待处理数据的计算流程。虚线矩形框表示该算子可能存在,而该虚线矩形框中的算子则是数据拷贝算子op_data_cpy,如果硬件图结构中有软件算子,数据拷贝算子即存在,具体地需要根据软件算子前后有无需要在硬件模块中进行的算子决定。

56.s50、通过所述执行器获取所述待处理数据和所述硬件图结构,并调用所述硬件模块对所述待处理数据进行所述硬件计算。

57.本实施例中,硬件计算模拟系统中编译器的硬件编译单元将神经网络的软件图结构转化为硬件图结构之后,执行器获取待处理数据和硬件图结构,待处理数据可以是需要进行特征提取的图像,执行器会调用的硬件模块对待处理数据进行计算,在硬件模块中进行的硬件计算相较于软件计算来说,计算速度更快,性能更强,适用于实际生产,硬件模块位于执行器的下层,硬件模块可以是caisa芯片。

58.本实施例基于一实施例提出,步骤s50可与步骤s30同时进行,也可在步骤s30之前进行,也可在步骤s30之后进行,本实施例对此不做限定。

59.可以理解的是,步骤s30中提到软件计算其实在模拟本实施例中的硬件计算,软件算子可以在cpu上运行,将硬件模块上的预期效果和计算流程展现出来,软件计算的结果可以和硬件计算的计算结果相互印证,简化了硬件模块的开发环境部署、测试以及迭代改进准确性和性能调优等方面的工作,为用于深度学习的硬件设备在设计阶段提供准确的测试支撑。

60.为便于理解,以下通过具体应用场景说明本方案,请参照图4、图5、图6、图7。

61.图4是卷积神经网络mobilenet的基本组件,以单批次处理(single batch)为例,当硬件计算模拟系统的构图接口获取到神经网络mobilenet后,通过硬件计算模拟系统的编译器将神经网络mobilenet的基本组件表示为如图5所示的mobilenet软件图结构sw_graph。图6是神经网络mobilenet软件图结构sw_graph经过编译器中的硬件编译模块序列化后的硬件图结构hw_graph,在图6中,虚线矩形框表示该算子可能存在,而该虚线矩形框中的算子则是数据拷贝算子op_data_cpy,如果硬件图结构中有软件算子,数据拷贝算子即存在,而具体位置则需要根据软件算子前后有无需要在硬件模块中进行的算子决定。

62.硬件计算模拟系统将sw_graph转换为hw_graph后,执行器将会根据这两个图结构执行相应的算子进行计算,sw_graph软件图结构将用来在cpu中执行模拟硬件计算行为的算子,hw_graph硬件图结构则会通过执行器调度caisa芯片硬件模块对数据进行计算。

63.sw_graph软件图结构将会通过执行器调用模拟硬件计算行为的软件算子,这里以图5中的软件算子m_conv的int8/int16量化过程举例说明。

64.m_conv对应的卷积公式是:f(x)表示卷积的输出,x为卷积层输入,w为卷积层的权重矩阵,b为偏置单元。kh和kw代表卷积核的高和宽,c为输入的通道数。

65.m_conv对应的量化公式为:r表示实数,q为量化后的数值,s为实数取值范围到量化域的比例缩放因子,z为零点,为r=0时q的值,用以保证r可以取到0。

66.根据上述两个公式可以推导出量化后的卷积结果公式:根据上述两个公式可以推导出量化后的卷积结果公式:

ro,ri,rw表示实数域的输出,输入和权重矩阵;qo,qi和qw表示量化域的输出,输入和权重矩阵;zo,zi和zw表示输出、输入和权重矩阵的零点;so,si和sw表示输出、输入和权重矩阵的比例缩放因子。

67.在硬件模块caisa芯片中的具体计算流程如图7所示,在硬件计算模拟系统中,即调用软件算子计算流程也是如图7所示模拟硬件的计算行为。

68.其中,上述公式通过krnl模块及actv模块实现,其中在krnl模块中完成中括号的计算:公式(7)中的常量部分可以转移到actv模块作为新的bias(偏置)进行计算,则公式(7)可以表示为:通过本实施例中提供的硬件模拟方法可以完全模拟caisa硬件的计算流程和行为,同时可得到各个模块的中间结果,为硬件验证和调试提供了依据。

69.本实施例提出的技术方案中,通过所述硬件编译单元将所述软件图结构序列化为硬件图结构;通过所述执行器获取所述待处理数据和所述硬件图结构,并调用所述硬件模块对所述待处理数据进行所述硬件计算。一方面通过调用硬件模块完成了数据处理,提高了数据处理的速度,另一方面,硬件计算结果可以和软件计算结果互相验证,且硬件计算的流程可以通过软件计算展现出来,互相提供准确的测试支撑,也提高了模拟硬件设备计算时的适配度和精准度。

70.此外,本发明实施例还提出一种硬件计算模拟系统,所述硬件计算模拟系统包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的硬件计算模拟方法程序,所述硬件计算模拟方法程序被所述处理器执行时实现如上各个实施例所述的硬件计算模拟方法的步骤。

71.此外,本发明实施例还提出一种硬件计算模拟系统,示例性地,参照图8,所述硬件计算模拟系统100包括:构建模块101、编译模块102和执行模块103,其中,构建模块101,用于通过构建接口获取神经网络;编译模块102,用于通过编译器将所述神经网络序列化为软件图结构;执行模块103,用于通过执行器获取待处理数据和所述软件图结构,并调用与所述软件图结构对应的软件算子对所述待处理数据进行软件计算,以模拟硬件模块对所述待处理数据的硬件计算。

72.此外,本发明实施例还提出一种计算机可读存储介质,所述计算机可读存储介质上存储有硬件计算模拟方法程序,所述硬件计算模拟方法程序被处理器执行时实现如上各个实施例所述的硬件计算模拟方法的步骤。

73.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该

要素的过程、方法、物品或者系统中还存在另外的相同要素。

74.上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

75.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在如上所述的一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得硬件计算模拟系统执行本发明各个实施例所述的方法。

76.以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1