一种PCIE接口验证板、测试系统及测试方法与流程

一种pcie接口验证板、测试系统及测试方法

技术领域

1.本发明涉及计算机技术领域,尤其涉及一种pcie接口验证板、测试系统及测试方法。

背景技术:

2.主板作为计算机内的重要器件,直接影响到计算机的计算、数据传输等性能。在主板上通常设置有pcie(peripheral component interconnect express,一种高速串行计算机扩展总线标准)插槽,来插接不同的pcie设备。通常一个pcie插槽上一般都只能插接一个pcie设备,但是在pcie设备所需要的通道宽度小于pcie插槽的通道宽度时,会造成pcie插槽的通道浪费现象。针对此,现有技术中存在了一个pcie插槽配置出多个pcie端口的设计方式,每个pcie端口均连接一个pcie设备,从而改善pcie插槽的通道浪费现象。

3.目前,针对一个pcie插槽配置出多个pcie端口的设计方式进行测试时,现有技术仍然采用传统的测试方式,先确定pcie插槽配置多个pcie端口的配置类型,之后一次只测试一个pcie端口,逐次测试该配置类型下的所有pcie端口。之后,再改变pcie插槽配置多个pcie端口的配置类型,并进行逐个测试该新的配置类型下的所有pcie端口。由于一个pcie插槽存在多种配置多个pcie端口的配置类型,且每个配置类型都包含多个pcie端口,从而造成测试pcie端口的次数呈几何倍数增加,耗时耗力,且不能对整个pcie插槽配置出的多个pcie端口同时进行测试,造成测试数据与实际应用效果存在偏差,从而降低了测试数据的准确性和可靠性。

技术实现要素:

4.本发明提供了一种pcie接口验证板、测试系统及测试方法,以减少测试pcie端口的次数,提高测试效率,省时省力;且还能够对整个pcie接口配置出的多个pcie端口同时进行测试,减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。

5.第一方面,本发明提供了一种pcie接口验证板,该pcie接口验证板用于测试支持配置为多pcie端口的单pcie接口。该pcie接口验证板包括一个电路板、以及设置在电路板上的第一pcie插接件,其中,第一pcie插接件用于与待测pcie接口插接。在电路板上设置有至少一个交换芯片,每个交换芯片均与第一pcie插接件连接。在电路板上还设置有至少两个第二pcie插接件,每个第二pcie插接件连接一个交换芯片,每个交换芯片连接至少一个第二pcie插接件。至少两个第二pcie插接件用于插接多个pcie设备,每个pcie设备插接在一个第二pcie插接件上,每个第二pcie插接件最多插接一个pcie设备。多个pcie设备与待测pcie接口被配置出的多个pcie端口一一对应,至少一个交换芯片用于配置每个pcie设备与对应的pcie端口通信连接。

6.在上述的方案中,通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片通过控制第一pcie插接件与每个第二pcie插接件之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种

配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

7.在一个具体的实施方式中,第一pcie插接件的通道宽度等于待测pcie接口的通道宽度,使第一pcie插接件的通道宽度能够完全覆盖待测pcie接口的通道宽度,且还不浪费第一pcie插接件的通道宽度。至少两个第二pcie插接件的通道宽度相等,使pcie设备在插接到至少两个第二pcie插接件上时,每个pcie设备可以随意插接在一个第二pcie插接件上,只需通过交换芯片识别配对即可完成每个pcie设备与对应pcie端口的通信连接,从而无需进行额外的插接限制。

8.在一个具体的实施方式中,每个第二pcie插接件的通道宽度与待测pcie接口的通道宽度相等。或每个第二pcie插接件的通道宽度,为待测pcie接口的通道宽度的一半。使第二pcie插接件能够对所有配置类型下的待测pcie接口进行测试。

9.在一个具体的实施方式中,待测pcie接口的通道宽度为x4、x8或x16。每个第二pcie插接件的通道宽度为x2、x4、x8或x16。以满足对常见类型的pcie接口进行测试的要求。

10.在一个具体的实施方式中,电路板上还设置有与每个交换芯片均连接的第一接口和存储模块。第一接口用于接收配置固件,并将配置固件写入存储模块中。每个交换芯片用于运行存储模块中的配置固件,控制第一pcie插接件与每个第二pcie插接件的导通或断开,以配置每个pcie设备与对应的pcie端口通信连接。以便于保存和运行不同类型的配置固件。

11.在一个具体的实施方式中,存储模块为快速擦写只读编程器,以提高配置固件的运行读取速度,提高测试效率。

12.在一个具体的实施方式中,电路板上还设置有复杂可编程逻辑器件。复杂可编程逻辑器件与每个交换芯片均连接,以控制每个交换芯片的上电、错误报警、在位检测或复位。以对交换芯片进行上电、错误报警、在位检测或复位等。

13.在一个具体的实施方式中,电路板上还设置有与复杂可编程逻辑器件均连接的第二接口和jtag((joint test action group,联合测试工作组,一种国际标准测试协议)接口。其中,第二接口用于与主板上的基板管理控制器连接,使基板管理控制器与复杂可编程逻辑器件进行信息交互。jtag接口用于更新复杂可编程逻辑器件内的固件。以在测试过程中与主板上的基板管理控制器进行信息交互,同时便于更新复杂可编程逻辑器件内的固件。

14.在一个具体的实施方式中,电路板上还设置有时钟缓冲器、以及与时钟缓冲器连接的第三接口。其中,第三接口用于接收和待测pcie接口连接的中央处理器生成的时钟信号。且时钟缓冲器与每个交换芯片均连接,以向每个交换芯片传输时钟信号。使连接在第二pcie插接件上的多个pcie设备采用同源时钟设计,更贴近实际应用场景,进一步减少测试数据与实际应用效果之间存在的偏差,进一步提高测试数据的准确性和可靠性。

15.第二方面,本发明还提供了一种pcie接口测试系统。pcie接口测试系统包括主板、位于主板上的中央处理器、以及位于主板上且与中央处理器均连接的至少一个待测pcie接

口,其中,每个待测pcie接口均支持配置为多pcie端口。该pcie接口测试系统还包括上述任意一种pcie接口验证板、以及插接在至少两个第二pcie插接件上的多个pcie设备。

16.在上述的方案中,通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片通过控制第一pcie插接件与每个第二pcie插接件之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

17.第三方面,本发明还提供了一种基于上述任意一种pcie接口验证板的pcie接口测试方法,该测试方法用于测试支持配置为多pcie端口的单pcie接口。该测试方法包括:将待测pcie接口与第一pcie插接件插接;在至少两个第二pcie插接件上插接多个pcie设备;至少一个交换芯片配置每个pcie设备与对应的pcie端口通信连接。

18.在上述的方案中,通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片通过控制第一pcie插接件与每个第二pcie插接件之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

附图说明

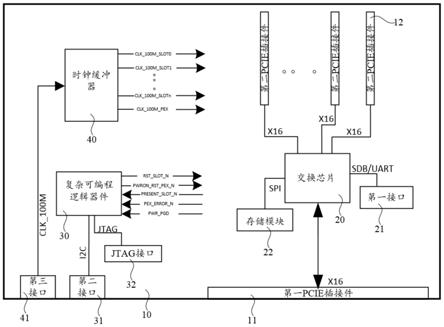

19.图1为本发明实施例提供的一种pcie接口验证板的整体拓扑框图;

20.图2为本发明实施例提供的另一种pcie接口验证板的整体拓扑框图;

21.图3为本发明实施例提供的一种交换芯片连接方式的拓扑图;

22.图4为本发明实施例提供的一种复杂可编程逻辑器件连接方式的拓扑图;

23.图5为本发明实施例提供的一种时钟缓冲器工作方式示意图;

24.图6为本发明实施例提供的一种待测pcie接口配置出多个pcie端口的配置示意图。

25.附图标记:

26.10-电路板 11-第一pcie插接件 12-第二pcie插接件

27.20-交换芯片 21-第一接口 22-存储模块

28.30-复杂可编程逻辑器件 31-第二接口 32-jtag接口

29.40-时钟缓冲器 41-第三接口 50-基板管理控制器

具体实施方式

30.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例

中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

31.为了方便理解本发明实施例提供的pcie接口验证板,下面首先说明一下本发明实施例提供的pcie接口验证板的应用场景,该pcie接口验证板用于测试支持配置为多pcie端口的单pcie接口,该待测pcie接口位于主板上,与主板上的中央处理器连接,由中央处理器将待测pcie接口配置出多个pcie端口。下面结合附图对该pcie接口验证板进行详细的叙述。

32.参考图1及图2,本发明实施例提供的pcie接口验证板包括一个电路板10、以及设置在电路板10上的第一pcie插接件11,其中,第一pcie插接件11用于与待测pcie接口插接。在电路板10上设置有至少一个交换芯片20,每个交换芯片20均与第一pcie插接件11连接。在电路板10上还设置有至少两个第二pcie插接件12,每个第二pcie插接件12连接一个交换芯片20,每个交换芯片20连接至少一个第二pcie插接件12。至少两个第二pcie插接件12用于插接多个pcie设备,每个pcie设备插接在一个第二pcie插接件12上,每个第二pcie插接件12最多插接一个pcie设备。多个pcie设备与待测pcie接口被配置出的多个pcie端口一一对应,至少一个交换芯片20用于配置每个pcie设备与对应的pcie端口通信连接。

33.在上述的方案中,通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片20通过控制第一pcie插接件11与每个第二pcie插接件12之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。下面结合附图对上述各个结构进行详细的介绍。

34.在设置电路板10时,参考图1,电路板10作为设置pcie插接件、交换芯片20等器件的支撑和互连结构,可以采用印刷电路板10作为电路板10,将pcie插接件、交换芯片20等器件设置在电路板10上,通过电路板10上或电路板10内的走线及过孔互连。

35.如图1及图2所示,在电路板10上设置有第一pcie插接件11,该第一pcie插接件11用于与待测pcie接口插接连接,以实现pcie接口验证板与待测pcie之间的连接。其中,待测pcie接口的通道宽度可以为x4、x8或x16等。在确定第一pcie插接件11的通道宽度时,需要保证第一pcie插接件11的通道宽度能够完全覆盖待测pcie接口的通道宽度。例如,可以使第一pcie插接件11的通道宽度等于待测pcie接口的通道宽度,以不浪费第一pcie插接件11的通道宽度。例如,如图1示出的第一pcie插接件11的通道宽度为x16,此时待测pcie接口的通道宽度也为x16。当然,还可以使第一pcie插接件11的通道宽度大于待测pcie接口的通道宽度,以保证第一pcie插接件11的通道宽度能够完全覆盖待测pcie接口的通道宽度。

36.参考图1,在电路板10上设置有至少一个交换芯片20,每个交换芯片20均与第一pcie插接件11连接,以通过第一pcie插接件11实现与待测pcie接口的连接。如图1示出的电路板10上设置有一个交换芯片20;如图2所示出的电路板10上设置有两个交换芯片20。应当理解的是,交换芯片20的个数并不限于1个或2个,除此之外,交换芯片20的个数还可以为3

个、4个等不少于3个的任意值。如图1及图2所示,在电路板10上还设置有至少两个第二pcie插接件12,每个第二pcie插接件12连接一个交换芯片20,每个交换芯片20连接至少一个第二pcie插接件12。即每个交换芯片20连接第二pcie插接件12的个数可以是一个,也可以是两个、三个、四个等不少于两个的任意值。但是,每个第二pcie插接件12仅与一个交换芯片20连接,而与其他的交换芯片20之间并不连接。在确定第二pcie插接件12的个数时,第二pcie插接件12的个数可以为2个、3个、4个、5个、6个、7个、8个、9个、10个等不少于2个的任意值。

37.在确定至少两个第二pcie插接件12的通道宽度时,可以使至少两个第二pcie插接件12的通道宽度相等,使pcie设备在插接到至少两个第二pcie插接件12上时,每个pcie设备可以随意插接在一个第二pcie插接件12上,只需通过交换芯片20识别配对即可完成每个pcie设备与对应pcie端口的通信连接,从而无需进行额外的插接限制。当然,至少两个第二pcie插接件12的通道宽度并不限于相同的设置方式,除此之外,还可以采用其他的设置方式。例如,可以使部分的第二pcie插接件12的通道宽度相等,而部分的第二pcie插接件12的通道宽度不相等;或者全部的第二pcie插接件12的通道宽度都不相等。

38.另外,可以使每个第二pcie插接件12的通道宽度均与待测pcie接口的通道宽度相等,以保证pcie设备能够插接到每个第二pcie插接件12上。当然,还可以使每个第二pcie插接件12的通道宽度,为待测pcie接口的通道宽度的一半。使第二pcie插接件12能够对所有配置类型下的待测pcie接口进行测试。每个第二pcie插接件12的通道宽度可以为x2、x4、x8或x16。以满足对常见类型的pcie接口进行测试的要求。应当理解的是,第二pcie插接件12的通道宽度的设置方式并不限于上述示出的方式,除此之外,还可以采用其他的设置方式。

39.第二pcie插接件12的个数具体与待测pcie接口连接的中央处理器,对待测pcie接口能够配置出的最多pcie端口数有关。在最优的实施方式中,第二pcie插接件12的个数需要至少不小于中央处理器对待测pcie接口能够配置出的最多pcie端口数。其中,中央处理器直接决定待测pcie接口能够被配置的pcie端口的个数。如图6所示中的待测pcie接口的通道宽度为x16。中央处理器针对该待测pcie接口所配置出的pcie端口类型可以为x8、x4、x2、x1等。如图6示出的将待测pcie接口配置出3个通道宽度为x4的pcie端口、和2个通道宽度为x2的pcie端口。对于通道宽度为n的待测pcie接口,如果中央处理器能够针对待测pcie接口配置出的pcie端口的最小通道宽度为x2,则待测pcie接口最多能够被配置出n/2个pcie端口,则需要尽可能保证第二pcie插接件12的个数在n/2个以上。如果中央处理能够针对待测pcie接口配置出的pcie端口的最小通道宽度为x1,则待测pcie接口最多能够被配置出n个pcie端口,则需要尽可能保证第二pcie插接件12的个数在n个以上。

40.交换芯片20的个数具体根据也与待测pcie接口连接的中央处理器,对待测pcie接口能够配置出的最多pcie端口数有关。待测pcie接口能够被中央处理器配置出较多的pcie端口时,交换芯片20的个数设置的需要多些;待测pcie接口能够被中央处理器配置出较少的pcie端口时,交换芯片20的个数设置的可以少些。另外,交换芯片20的个数还与每个交换芯片20所支持的最多端口数有关,例如,有的交换芯片20所支持的下行pcie端口的个数为4个,有的交换芯片20所支持的下行pcie端口的个数为8个。而在相同的待测pcie接口的情况下,由于不同交换芯片20所支持的下行pcie端口的个数不同,所使用的交换芯片20的个数也不同。

41.在具体测试时,至少两个第二pcie插接件12插接有多个pcie设备,每个pcie设备插接在一个第二pcie插接件12上,每个第二pcie插接件12最多插接一个pcie设备。多个pcie设备与待测pcie接口被配置出的多个pcie端口一一对应,至少一个交换芯片20配置每个pcie设备与对应的pcie端口通信连接。通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片20通过控制第一pcie插接件11与每个第二pcie插接件12之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

42.下面以图2示出的待测pcie接口的通道宽度为x16,电路板10上设置有两个交换芯片20,每个交换芯片20连接有四个通道宽度为x16的第二pcie插接件12为例,示出几种配置方案。

43.例1,中央处理器能够针对图2的待测pcie接口配置出4个通道宽度均为x4的pcie端口。此时,插接在第二pcie插接件12上的pcie设备的个数也为四个,且每个pcie设备的通道宽度也均为x4,显然,x4的pcie设备能够插接到x16的第二pcie插接件12上。此时,可以将四个pcie设备均插接在其中任意一个交换芯片20下的四个第二pcie插接件12上即可,从而能够满足对待测pcie接口配置出的4个x4的pcie端口同时进行测试的要求。当然,还可以将两个pcie设备均插接在其中一个交换芯片20下的任意两个第二pcie插接件12上,将两外两个pcie设备均插接在另一个交换芯片20下的任意两个第二pcie插接件12上,以能够满足对待测pcie接口配置出的4个x4的pcie端口同时进行测试的要求。

44.例2,中央处理器能够针对图2示出的待测pcie接口配置出1个通道宽度均为x4的pcie端口、和6个通道宽度为x2的pcie端口。此时,插接在第二pcie插接件12上的pcie设备的个数为七个,七个pcie设备中有一个pcie设备的通道宽度为x4,另外六个pcie设备的通道宽度均为x2,显然,x4或x2的pcie设备能够插接到x16的第二pcie插接件12上。此时,可以将四个x2的pcie设备插接在其中一个交换芯片20下的四个第二pcie插接件12上,另外两个x2的pcie设备和一个x4的pcie设备插接在另外一个交换芯片20下的任意三个第二pcie插接件12上,以能够满足对待测pcie接口配置出的6个x2和1个x4的pcie端口同时进行测试的要求。

45.参考图1、图2及图3,在电路板10上还可以设置有与每个交换芯片20均连接的第一接口21和存储模块22。其中,第一接口21用于接收配置固件,并将配置固件写入存储模块22中。每个交换芯片20用于运行存储模块22中的配置固件,控制第一pcie插接件11与每个第二pcie插接件12的导通或断开,以配置每个pcie设备与对应的pcie端口通信连接。以便于保存和运行不同类型的配置固件。在确定存储模块22时,可以采用快速擦写只读编程器作为存储模块22,以提高配置固件的运行读取速度,提高测试效率。应当理解的是,存储模块22并不限于采用快速擦写只读编程器,除此之外,还可以采用其他类型的存储介质作为存储模块22。参考图1,交换芯片20可以通过诸如但不限于spi(serial peripheral interface,串行外设接口)接口等接口与存储模块22连接。继续参考图1,第一接口21可以

为诸如但不限于sdb(smart deep buffer,智能深度缓冲)接口、uart(universal asynchronous receiver/transmitter,通用异步收发传输器)接口等接口类型。

46.参考图1及图4,还可以在电路板10上设置复杂可编程逻辑器件30,复杂可编程逻辑器件30与每个交换芯片20均连接,以控制每个交换芯片20的上电、错误报警、在位检测或复位等功能。具体的,参考图1,其中的pwr_pgd表示电源接地信号,pex_error_n表示第n个交换芯片20错误报警信号,present_slot_n表示第n个第二pcie插接件12的在位检测信号,pweon_rst_pex_n表示第n个交换芯片20的重启上电信号,rst_slot_n表示第n个第二pcie插接件12的复位信号。以对交换芯片20进行上电、错误报警、在位检测或复位等。另外,如图1及图4所示,还可以在电路板10上进一步设置有与复杂可编程逻辑器件30均连接的第二接口31和jtag接口32。其中,第二接口31用于与主板上的基板管理控制器50连接,使基板管理控制器50与复杂可编程逻辑器件30进行信息交互。第二接口31可以采用诸如但不限于i2c接口等通信接口。jtag接口32用于更新复杂可编程逻辑器件30内的固件。在主板上预留有jtag接口时,可以使主板上的jtag接口32与pcie接口验证板上的jtag接口32连接,从而能够通过主板上的基板管理控制器50更新复杂可编程逻辑器件30内的固件。通过上述方式,能够在测试过程中与主板上的基板管理控制器50进行信息交互,同时便于更新复杂可编程逻辑器件30内的固件。

47.参考图1及图5,还可以在电路板10上设置时钟缓冲器40、以及与时钟缓冲器40连接的第三接口41。其中,第三接口41用于接收和待测pcie接口连接的中央处理器生成的时钟信号。如图1所示,第一接口41输出的clk_100m(一种时钟信号)传输给时钟缓冲器40。且时钟缓冲器40与每个交换芯片20均连接,以向每个交换芯片20传输时钟信号。即电路板10上的交换芯片20和连接在交换芯片20的下行端口的pcie设备采用同源时钟设计,使中央处理器的cpu差分时钟信号依次通过主板上的走线、第三接口41、电路板10上的走线连接到时钟缓冲器40,时钟缓冲器40推出的各种类型的clk_100m再连接到交换芯片20以及各个第二pcie插接件12上,从而实现交换芯片20和pcie设备之间采用同源时钟信号。具体的,从时钟缓冲器40推出的各种类型的clk_100m可以为如图1示出的clk_100m_slot0~n(分别表示传输给不同第二pcie插接件12的时钟信号)、和clk_100m_pex(表示传输给交换芯片20的时钟信号)。

48.使连接在第二pcie插接件12上的多个pcie设备采用同源时钟设计,更贴近实际应用场景,进一步减少测试数据与实际应用效果之间存在的偏差,进一步提高测试数据的准确性和可靠性。

49.通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片20通过控制第一pcie插接件11与每个第二pcie插接件12之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

50.另外,本发明实施例还提供了一种pcie接口测试系统。该pcie接口测试系统包括

主板、位于主板上的中央处理器、以及位于主板上且与中央处理器均连接的至少一个待测pcie接口。具体的,主板上可以含有的待测pcie接口的个数可以为1个、2个、3个、4个等任意个数,且每个待测pcie接口均支持配置为多pcie端口。参考图1及图2,该pcie接口测试系统还包括上述任意一种pcie接口验证板、以及插接在至少两个第二pcie插接件12上的多个pcie设备。通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片20通过控制第一pcie插接件11与每个第二pcie插接件12之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

51.另外,如前述pcie接口验证板部分所述,参考图1及图4,在主板上还可以设置有基板管理控制器50,可以使基板管理控制器50通过电路板10上的第二接口31,和电路板10上的复杂可编程逻辑器件30连接,使基板管理控制器50与复杂可编程逻辑器件30进行信息交互。

52.再者,本发明还提供了一种基于上述任意一种pcie接口验证板的pcie接口测试方法,该测试方法用于测试支持配置为多pcie端口的单pcie接口。参考图1及图2,该测试方法包括:

53.将待测pcie接口与第一pcie插接件11插接;

54.在至少两个第二pcie插接件12上插接多个pcie设备;

55.至少一个交换芯片20配置每个pcie设备与对应的pcie端口通信连接。具体实现配置每个pcie设备与对应的pcie端口通信连接的方式参考前述关于pcie接口验证板部分的描述,在此不再赘述。

56.通过设计一个pcie接口验证板作为待测pcie接口与多个pcie设备之间连接的转接设备,使至少一个交换芯片20通过控制第一pcie插接件11与每个第二pcie插接件12之间的导通或断开,配置每个pcie设备与对应的pcie端口通信连接,从而能够对一种配置类型下该待测pcie接口配置出的多个pcie端口同时进行测试,使测试场景与实际应用场景非常贴近,从而减少测试数据与实际应用效果之间存在的偏差,提高测试数据的准确性和可靠性。且由于能够同时对同一配置类型下的多个pcie端口进行测试,从而也就无需对同一配置类型下的单个pcie端口进行逐个测试,减少了测试pcie端口的次数,提高测试效率,省时省力。

57.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1