一种基于兆芯ZXE处理器的密码安全平台主板的制作方法

一种基于兆芯zxe处理器的密码安全平台主板

技术领域:

1.本实用新型属于密码安全平台主板技术领域,特别涉及一种基于兆芯zxe处理器的密码安全平台主板。

背景技术:

2.随着网络安全形势越发严峻,国家对重要网络的安全防护要求逐步提升。《网络安全法》等系列标准中要求各企事业单位对重要信息系统和关键数据必须采用密码技术,解决用户身份认证、数据安全传输和数据安全存储等问题。在现有技术中,很多密码安全平台仍在使用基于非国产的处理器搭建的硬件平台,不利于相关的企事业对于安全系统的全方位防护。同时金融支付、身份认证、网络加密等专用功能,也需要设计更多符合专用设备的接口。

3.公开于该背景技术部分的信息仅仅旨在增加对本实用新型的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

4.本实用新型的目的在于提供一种基于兆芯zxe处理器的密码安全平台主板,从而克服上述现有技术中的缺陷。

5.为实现上述目的,本实用新型采用的技术方案如下:

6.一种基于兆芯zxe处理器的密码安全平台主板,包括cpu处理器、分别与cpu处理器连接的io扩展模块、电源模块、lpc模块、ec控制器模块和vga显示模块,所述cpu处理器通过一路pcie x4插槽与io扩展模块连接,通过lpc总线与lpc模块、ec控制器模块连接,通过vga接口与vga显示模块连接。

7.所述cpu处理器选用兆芯zxe系列处理器,所述cpu处理器还设置有ddr4控制器接口、sata控制器接口、pcie x1通道、pcie x8插槽、两路usb2.0控制器输出接口和两路usb3.0输出接口,所述ddr4控制器接口连接两个ddr4内存插槽,所述pcie x1通道与一路千兆网络控制器相连。

8.所述io扩展模块选用zx

‑

200芯片,所述io扩展模块设置有五路pcie x1通道、pcie x4插槽和usb2.0接口,所述五路pcie x1通道连接五路千兆网络控制器,所述usb2.0接口连接与密码算法芯片。

9.所述ec控制器模块选用it8786控制器,所述ec控制器模块通过lpc总线连接到cpu处理器,所述ec控制器模块设置有ps/2接口、并口、风扇接口和串口。

10.所述lpc模块通过lpc转isa总线转换后再通过lpc总线连接到cpu处理器。

11.所述千兆网络控制器选用intel i210以太网控制器。

12.所述密码算法芯片选用32位soc安全芯片ach512。

13.采用本实用新型的技术方案的一个方面具有以下有益效果:

14.本实用新型在cpu处理器上接io扩展模块,可增加主板的可扩展性,以符合专用设备的;io扩展模块连接密码算法芯片,可直接通过usb2.0接口调用硬件加密算法,提高通信效率、减少编码成本;此外cpu处理器、密码算法芯片均采用国产芯片,可提高主板的安全性。

附图说明:

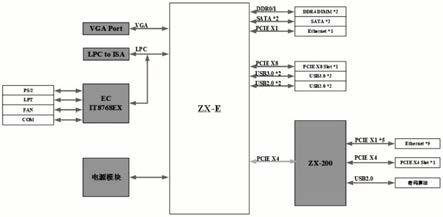

15.图1为本实用新型的一种基于兆芯zxe处理器的密码安全平台主板的示意图。

具体实施方式:

16.下面对本实用实用新型的具体实施方式进行详细描述,但应当理解本实用新型的保护范围并不受具体实施方式的限制。

17.除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

18.如图1所示,一种基于兆芯zxe处理器的密码安全平台主板,包括cpu处理器、分别与cpu处理器连接的io扩展模块、电源模块、lpc模块、ec控制器模块和vga显示模块,所述cpu处理器通过一路pcie x4插槽与io扩展模块连接,通过lpc总线与lpc模块、ec控制器模块连接,通过vga接口与vga显示模块连接。

19.所述cpu处理器选用兆芯zxe系列处理器,所述cpu处理器还设置有ddr4控制器接口、sata控制器接口、pcie x1通道、pcie x8插槽、两路usb2.0控制器输出接口和两路usb3.0输出接口,所述ddr4控制器接口连接两个ddr4内存插槽,所述pcie x1通道与一路千兆网络控制器相连。

20.其中zxe系列处理器主频高达3.0ghz,拥有8mb高速缓存,兼容x86指令集,支持cpu硬件虚拟化技术,支持双通道ddr4

‑

3200内存,兼容全系列windows操作系统及中科方德、中标麒麟、湖南麒麟、深度、普华等国产自主可控操作系统,并支持国内外主流应用及外设,芯片整体性能瞄准7代i5,能够更好满足应用需求。

21.cpu模块的显示控制器与vga接口相连,cpu通过lpc总线与lpc模块相连,cpu的ddr4控制器接口与两个ddr4内存插槽相连,cpu的sata控制器与sata接口相连,cpu的pcie通道与1路千兆网络控制器相连。cpu的usb控制器输出2路usb2.0及2路usb3.0接口。从cpu接出一路pcie x4插槽,提高可扩展性。

22.所述io扩展模块选用zx

‑

200芯片,所述io扩展模块设置有五路pcie x1通道、pcie x4插槽和usb2.0接口,所述五路pcie x1通道连接五路千兆网络控制器,所述usb2.0接口连接与密码算法芯片。

23.所述ec控制器模块选用it8786控制器,所述ec控制器模块通过lpc总线连接到cpu处理器,所述ec控制器模块设置有ps/2接口、并口、风扇接口和串口。

24.所述lpc模块通过lpc转isa总线转换后再通过lpc总线连接到cpu处理器。

25.所述千兆网络控制器选用intel i210以太网控制器,该控制器是一款低功耗、小尺寸、单端口的千兆网络控制器,为运行严格控制的媒体流同步和缓冲提供了理想的gbe解决方案,增强网络连接性,其功能可提高嵌入式应用的性能。

26.所述密码算法芯片选用32位soc安全芯片ach512,该算法芯片嵌入了经国家密码管理局批准的专用密码算法,如sm1、sm2、sm3、sm4等,符合国密局关于密码设备的各类标准,既提高了芯片的利用率,又能简化板卡设计,降低成本。

27.本实用新型设置有io扩展模块,可增加主板的可扩展性,以符合专用设备的;io扩展模块连接密码算法芯片,可直接通过usb2.0接口调用硬件加密算法,提高通信效率、减少编码成本;此外cpu处理器、密码算法芯片、所述ec控制器模块均采用国产芯片,可提高主板的安全性。

28.前述对本实用新型的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本实用新型限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本实用新型的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本实用新型的各种不同的示例性实施方案以及各种不同的选择和改变。本实用新型的范围意在由权利要求书及其等同形式所限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1