用于派发加载/存储指令的微处理器和方法与流程

1.本发明涉及一种微处理器,尤其涉及一种能够投机地发出加载/存储指令的方法和微处理器。

背景技术:

2.超纯量(superscalar)微处理器通过每频率周期执行多个指令且通过指令的乱序执行而实现高性能。指令必须有序回写到寄存器组,以避免诸如分支误预测、中断以及精确例外事件等控制危障(control hazard)。例如重新排序缓冲器、寄存器重命名等临时存储装置可用于暂存结果数据,直到可将之依序退役到寄存器组为止。此外,亦需要存储装置将来源操作数数据保持在执行队列中,直到指令可由功能单元执行为止。这些存储装置通常为架构寄存器组的大小的数倍大,且这些存储装置的读取/写入消耗很多的电力。

3.以性能来看,管线(pipeline)架构的微处理器中以加载和存储指令对性能影响最大,也最难优化。具有确定延迟和吞吐时间的指令可以安排在特定未来时间执行。然而,加载/存储指令可能因为tlb未命中、快取未命中或冲突等原因而无法事先知道知道其延迟时间。对于加载指令,加载数据可在下一周期或许多周期后返回,且提早写回加载数据会违反数据相依性,例如写后写(write-after-write;waw)数据相依性和读后写(write-after-read;war)数据相依性。对于存储指令,存储数据会在下一周期或许多周期后从寄存器组读取,且提早读取存储数据会违反数据相依性,例如写后读(read-after-write;raw)数据相依性。当加载/存储指令具有数据相依性时,加载/存储指令会暂停在解码/发射单元中,直到数据相依性被解开为止。在解码/发射单元中暂停加载/存储指令可能会降低微处理器的性能。

技术实现要素:

4.本发明描述一个以纪录寄存器组的个别寄存器使用状况的记分板来投机地发出加载/存储指令的微处理器和方法。

5.本发明的微处理器包含一个记录指令延迟和读取时间的记分板用以追踪所有具有确定延迟和读取时间的指令。微处理器将指令连同从寄存器组的多个读取端口读取数据的默认读取时间,以及将数据写入到寄存器组的多个写入端口派的预设写入时间一起派发到执行队列。有未定(unknown)延迟时间的加载指令可以被派发、执行并且运用专用写入端口回写到寄存器组。可能有未定读取时间的存储指令,可以被派发,且运用专用读取端口从寄存器组读取数据。如果存在waw数据相依性、war数据相依性或raw数据相依性,那么记分板检查数据相依性且在解码/发射单元中暂停加载及存储指令。在解码/派发阶段中被暂停的加载/存储指令会阻止指令流前进。在本发明的实施例中,加载/存储指令分派到加载/存储执行队列,并在其中监视读取和写入端口以便清除数据相依性状态。而记分板的内容会被复制到加载/存储执行队列,从而允许指令流中的后续指令向前移动。后续指令只要不具有对加载/存储指令的数据相依性即可被派发且执行,因此改进微处理器性能。加载/存储

指令在加载/存储执行队列中等待数据相依性解开,且一旦数据相依性解开,则将之分派到加载/存储执行单元。在另一实施例中,加载/存储指令包含向量加载/存储指令,其中每一向量指令可具有多个微操作,且每一微操作可独立地解开其自身数据相依性,以便分派到加载/存储单元以供执行。其记分板内的未定栏位(unknown field)有多个位。多位的未定栏位得以将多个加载/存储指令分派到执行队列。

6.本发明的方法适用于包含一个记分板和一个加载/存储队列的微处理器,其中记分板包含多个记分板条目,且所述多个记分板条目中的每一项包括多个未定位值(unknown bits value)和一个计数值(count value)。所述方法包含以下步骤:将加载/存储指令连同依据加载/存储指令的目的地寄存器或来源寄存器所查到的记分板的未定位值和计数值派发到加载/存储队列。如果加载/存储指令为一加载指令,那么加载/存储指令的派发是基于加载/存储指令的目的地寄存器;且如果加载/存储指令为一存储指令,那么加载/存储指令的派发是基于加载/存储指令的来源寄存器。

附图说明

7.配合附图阅读以下详细描述可以最好地理解本发明的各方面。应注意,根据业界中的标准惯例,各个特征未按比例绘制。实际上,为了论述清楚起见,各个特征的尺寸可能会任意的增大或减小。

8.图1是根据一些实施例所绘制的数据处理系统的框图;

9.图2是根据本发明的一些实施例的记分板和寄存器组的图标;

10.图3a到图3b是根据本发明一些实施例的记分板条目的各种结构的图标;

11.图4是根据本发明的一些实施例中,与寄存器组的读取端口配合的读取移位器的图示;

12.图5是根据本发明的一些实施例中,与寄存器组的写入端口配合的写入移位器的图示;

13.图6是根据本发明的一些实施例的执行队列的图标;

14.图7是根据本发明的一些实施例的数据执行队列(data execution queue;deq)的图示;

15.图8是根据一些实施例对一个访问时间确定的waw数据相依性的加载指令的派发操作的图示;

16.图9是根据一些实施例对一个访问时间未定的waw数据相依性的加载指令的派发操作的图示;

17.图10a到图10b是根据一些实施例对一个访问时间确定的raw数据相依性的存储指令的派发操作的图示;

18.图11a和图11b是根据一些实施例对一个访问时间未定的raw数据相依性的存储指令的派发操作的图示;

19.图12a和图12b是根据一些实施例对一个访问时间确定的war数据相依性的存储指令的派发操作的图示;

20.图13a和图13b是根据一些实施例对一个访问时间未定的raw数据相依性的加载指令的派发操作的图示;

21.图14a到图14c是根据本发明的一些实施例对向量加载/存储指令排程的图标。

具体实施方式

22.以下公开内容提供用于实施本发明的不同特征的多个不同实施例或实例。更使用特定的组件实例和安排实例来简化本发明。当然,这些仅是实例而非意图限制本发明范围。举例来说,在以下描述中,两个特征的叠加可以包括两个特征直接接触形成的实施例,也可包括两个特征之间可不直接接触而通过附加特征以叠加的实施例。另外,本发明会在各种实例中重复使用附图标记和/或字母。此重复是出于简单和清晰的目的,而非暗示所论述的各种实施例和/或配置之间的关系。

23.本发明介绍一种将指令安排(调度;schedule)在未来某时间执行而非暂停管线的微处理器。此处理器还可被称作未来调度执行(future scheduling execution;fse)微处理器。传统上,如果指令使用的寄存器或功能单元尚未就绪(例如资源冲突,例如数据相依性、寄存器的读取和写入端口的可用状态、功能单元的可用状态等),那么解码/发射单元会暂停执行管线或将指令放置一旁,直到寄存器或功能单元的可用状态确定为止。在fse微处理器中,解码/发射单元则仍然可以根据某未来时间会解除数据相依性、寄存器和功能单元的读取和写入端口的可用状态,而将这些指令安排至该未来时间执行。

24.加载/存储指令可因为寄存器的未定延迟(unknown latency)和读取时间在解码/发射单元中暂停。在本发明中,耦合于解码/发射单元与加载/存储单元之间的数据执行队列配置成可以处理有未定存取(写入或读取)时间的加载/存储指令。与其暂停管线,加载/存储指令及其记分板的值可以一起派发至数据执行队列以安排在未来执行。

25.参考图1,这是根据一些实施例所绘制的,包含一个微处理器10和一个内存30的数据处理系统1的示意图。其中微处理器10通过执行存储于内存30中的指令来执行多种数据处理功能。内存30可包含2级(level 2,l2)快取和3级(level 3,l3)快取以及数据处理系统1的主存储器,其中l2快取和l3快取具有比主存储器快的访问时间。内存可包含随机存取内存(random access memory,ram)、动态随机存取内存(dynamic random access memory,dram)、静态随机存取内存(static random access memory,sram)、只读存储器(read only memory,rom)、可程序化只读存储器(programmable read only memory,prom)、可擦拭可规划式只读存储器(erasable programmable read only memory,eprom)、电子抹除式可复写只读存储器(electrically erasable programmable read only memory,eeprom)以及闪存中的至少一个。

26.微处理器10可以是一个在单个微处理器内实现指令层级平行的超纯量微处理器。超纯量微处理器通过每频率周期执行多个指令而实现高性能。将多个指令分派到不同功能单元以供并行执行。超纯量微处理器可采用乱序(out-of-order,ooo)执行,而可在第一指令之前执行对第一指令没有任何相依性的第二指令。在传统的乱序微处理器设计中,指令可乱序执行,但由于例如分支误预测、中断以及精确例外事件的控制危障,所述指令必须有序退休到微处理器的寄存器组。像重新排序缓冲器和寄存器重命名之类的临时存储装置可用于暂存结果数据,直到指令从执行管线有序退休为止。在本发明中,只要指令没有数据相依性和控制危障,微处理器10就可通过将结果数据不依序回写到寄存器组而乱序执行和退休该指令。在实施例中,此fse微处理器10不需要任何一个临时寄存器,这是因为微处理器

10配置成仍可通过调度与安排指令的未来运行时间而派发出有数据相依性或控制危障的指令。然而,此限制并非本发明的意图。在一些其它实施例中,临时寄存器还是可以使用。

27.参考图1,微处理器10可包含指令快取11、分支预测单元(branch prediction unit,bpu)12、解码/发射单元13、寄存器组14、记分板15、读取/写入控制单元16、加载/存储单元17、数据快取18、多个执行队列(execution queue;eq)19a~19e,多个功能单元(functional unit,funt)20a~20c。微处理器10亦包含读取总线31和结果总线32。读取总线31耦合到加载/存储单元17、功能单元20a-20c以及寄存器组14以用于将操作数数据从寄存器组14中的寄存器传输到加载/存储单元17和功能单元20a~20c,这动作还可被称作从寄存器组14读取操作数数据(或在存储指令的情况下为存储数据)。结果总线32耦合到数据快取18、功能单元20a~20c以及寄存器组14以用于将数据从数据快取18或功能单元20a~20c传输到寄存器组14的寄存器,这动作还可被称作将结果数据(或在加载指令的情况下为加载数据)回写到寄存器组14。附图内的组件的标记号码如果为数字接一个字母,本文中以后将只引用数字标记来统称这些组件。举例而言,执行队列19a-19e可统称为执行队列19。本发明的一些实施例可使用比图1中所示出的组件更多、更少或不同的组件。

28.在一些实施例中,指令快取11耦合(未示出)到内存30和解码/发射单元13,且配置成存储从内存30提取的指令并将所述指令分派到解码/发射单元13。指令快取11存储来自内存30的连续指令字节中的许多快取列。快取列可组织为直接映像、完全关联映像或组关联映像等。直接映像、完全关联映像以及组关联映像在相关技术中是众所周知的,因此省略关于以上映射的详细描述。

29.指令快取11可包含标记数组(未示出)和数据数组(未示出)以用于分别存储一部分由微处理器10频繁使用的指令的地址和数据。标记数组中的每一标记对应于数据数组中的快取列。当微处理器10需要执行指令时,微处理器10首先通过将指令的地址与存储于标记数组中的标记进行比较来检查指令是否在指令快取11中。如果指令地址与标记数组中的一个标记匹配(即,命中快取),那么从数据数组提取对应快取列。如果指令地址未能与标记数组中的任何条目匹配(即,未命中快取),那么微处理器10可存取内存30以找到指令。在一些实施例中,微处理器10还包含一个耦合到指令快取11和解码/发射单元13的指令队列(未示出),用于在将指令发送到解码/发射单元13之前存储来自指令快取11或内存30的指令。

30.bpu 12耦合到指令快取11且配置成投机地提取在分支指令之后的指令。bpu 12可基于分支指令的过往行为提供对分支指令的分支方向的预测(跳转或不跳转),且预测跳转分支指令的分支目标地址。分支方向可为“跳转”,则从该跳转分支指令的分支目标地址提取后续指令。分支方向可为“不跳转”,则从分支指令后面的连续内存位置提取后续指令。在一些实施例中,bpu 12使用基本块分支预测,从基本块的起始地址预测基本块的结束地址。基本块的起始地址(即基本块的第一指令的地址)可为先前跳转的分支指令的目标地址。基本块的结束地址是在基本块的最后一个指令之后的指令地址,该指令地址可为另一基本块的起始地址。基本块可包含多个指令,而结束于其中跳转到另一基本块的分支指令。

31.功能单元可包含分支执行单元(branch execution unit,beu)(例如,耦合到分支预测单元12的功能单元20c,如图1中所示),所述分支执行单元可执行分支指令且判断所预测分支方向是否不正确(误预测)。举例而言,beu可将所预测分支方向(跳转或不跳转)与实际执行的分支进行比较以判断所预测分支方向是否正确。误预测分支之后的指令不论在微

处理器中的各单元内皆会被舍弃。分支误预测还可来自解码/发射单元13针对未由bpu 12预测的无条件分支指令(永远跳转的分支)解码产生。解码单元13和beu 12可将更新信息提供给bpu12。在微处理器10中,在分支指令之后的指令必须等到分支指令执行之后才能回写到寄存器组14。

32.解码/发射单元13可对从指令快取11接收到的指令进行解码。指令可包含以下栏位:操作代码(或作业码)、操作数(例如,来源操作数和目的地操作数)以及立即数据。操作码可指定进行何种操作(例如,add、subtract、shift、store、load等)。操作数可指定寄存器组14中的寄存器的索引或地址,其中来源操作数指定将要从寄存器组读取的寄存器,且目的地操作数指定寄存器组中将写回结果数据的寄存器。这边要指出,来源操作数和目的地操作数有时亦可称作来源寄存器和目的地寄存器,在下文中会交换使用。在实施例中,一个操作数会需要5位索引才能在一个具有32个寄存器的寄存器组中识别其中一个寄存器。一些指令可能使用指令中所指定的立即数据而不是寄存器数据。每一指令将在功能单元20或加载/存储单元17中执行。基于由操作码指定的操作类型和资源的可用状态(例如,寄存器、功能单元等),每一指令皆有一个执行延迟时间和一个吞吐时间。执行延迟时间(或延迟时间)是指指令完成执行指定的操作并回写结果数据的时间(即,频率周期数)。吞吐时间是指下一道指令可进入功能单元20的时间(即,频率周期数)。

33.在实施例中,在解码/发射单元13中对指令进行解码并根据操作码获得执行延迟时间、吞吐时间以及指令类型。多个指令可派发到一个执行队列19,并在其中累计一个含括多个指令的吞吐时间的累积吞吐时间。累积吞吐时间是根据执行队列19先前派发的指令所统计出来,下一指令可进入功能单元20执行的时间。指令可送至功能单元20的时间被称作读取时间(读取寄存器组的时间),且指令由功能单元20完成的时间被称作写入时间(写到寄存器组的时间)。指令派发到执行队列19时,每一指令皆有安排好分派到功能单元20或加载/存储单元17执行的读取时间。累积吞吐时间为当前派发指令的读取时间。当指令派发到执行队列19的下一可用条目时,指令的指令延迟时间与累积吞吐时间相加以求得写入时间。修改后的执行延迟时间在本文中将被称作最近派发的指令的写入时间,且修改后的开始时间在本文中将被称作所派发指令的读取时间。写入时间和读取时间还可被称作访问时间,描述所派发指令从寄存器组14写入或读取一个寄存器的特定时间点。由于仅在时间上安排从寄存器组14实时读取来源寄存器以供功能单元20执行的时间,所以执行队列中不需要存储来源寄存器的临时寄存器,这与其它微处理器的一些实施例相比是个优点。如果与其它功能单元20或数据快取24存在冲突,由于可在时间上安排未来从功能单元20或数据快取24回写到寄存器组14的目的地寄存器的确切时间以错开冲突,所以不需要临时寄存器来存储结果数据,这与其它微处理器的一些实施例相比亦是个优点。对于多于一个指令的并行派发,可基于在第二指令之前派发的第一指令而进一步调整第二指令的写入时间和读取时间。在一些实施例中,解码/发射单元13可将一个加载/存储指令解码为标记微操作和数据微操作组成的两个微操作。

34.在实施例中,解码/发射单元13配置成在派发指令之前检查和解决所有可能冲突。指令可具有以下4种基本类型的冲突:(1)数据相依性,其包含读后写(war)、写后读(raw)以及写后写(waw);(2)用以从寄存器组读取数据到功能单元的读取端口的可用状态;(3)用以从功能单元回写数据到寄存器组的写入端口的可用状态;以及(4)用以执行数据的功能单

元160的可用状态。在指令可派发到执行队列19之前,解码/发射单元13可存取记分板15以检查数据相依性。此外,寄存器组14具有有限数目个读取和写入端口,且所派发指令必须仲裁或保留读取和写入端口以在未来时间存取寄存器组14。解码/发射单元13可存取读取/写入控制单元16以检查寄存器组14的读取端口和写入端口的可用状态,以便安排指令的访问时间(即,读取和写入时间)。在其它实施例中,写入端口之一可专用于有未定执行延迟时间的指令以在不使用写入端口控制的情况下写回寄存器组14,且读取端口之一可保留给具有未定读取时间的指令,以从寄存器组14读取数据而不使用读取端口控制。寄存器组14的读取端口的数目可动态保留(不专用)用于未定读取操作。在这种情况下,功能单元20或加载/存储单元17在试图从寄存器组14读取数据时必须确保读取端口不忙碌。在实施例中,功能单元20的可用状态可通过与执行队列19协调其累积的排队指令(即,先前发出到执行队列的指令)的吞吐时间而解决。基于执行队列中的累积吞吐时间,指令可分派到执行队列19,在其中安排指令在功能单元20未来有空的特定时间发出到功能单元20。

35.图2为根据本发明的一些实施例的寄存器14和记分板15所绘制的框图。寄存器组14可包含多个寄存器r(0)-r(n)、读取端口以及写入端口(未示出),其中n是大于1的整数。在实施例中,寄存器组14可包含纯量寄存器组和向量寄存器组。本发明并没有限制寄存器组14中的寄存器、读取端口以及写入端口的数目。记分板15包含多个条目150(0)到150(n),且每一记分板条目对应于寄存器组14中的一个寄存器且记录与对应寄存器相关的信息。在实施例中,记分板15具有与寄存器组14数目相同的条目(即,n个条目),但本发明并没有限制记分板15中的条目数。

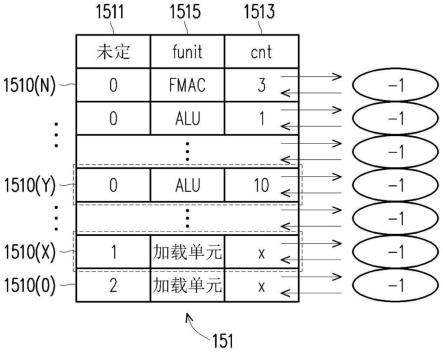

36.图3a-图3b是根据本发明一些实施例的记分板条目的各种结构的图标。在实施例中,记分板15可包含一个用于处理到寄存器组14的回写操作的第一记分板151和一个用于处理来自寄存器组14的读取操作的第二记分板152。第一记分板151及第二记分板152可共存或不共存于微处理器10中。本发明并不做此限制。在其它实施例中,可将第一记分板151和第二记分板152实施为或查看为同时处置读取和写入操作的单一记分板15。图3a示出用于所派发指令的目的地寄存器的第一记分板151。图3b示出用于所派发指令的来源寄存器的第二记分板15。参考图3a,第一记分板151的每一条目1510(0)到1510(n)包含未定栏位(“unknown”)1511、计数栏位(“cnt”)1513以及功能单元栏位(“funit”)1515。这些栏位纪录所派发指令即将写入的目的地寄存器有关的信息。这些记分板条目的栏位在派发指令时设置。

37.未定栏位1511包含一个位值用以指示对应于记分板条目的寄存器的写入时间是确定(known)还是未定(unknown)。举例来说,未定的加载栏位1511可包含一个位,其中非零值指示寄存器有未定的写入时间,而零值指示寄存器有确定写入时间,如写入计数栏位1513所示。在一些实施例中,未定栏位1511可包含任意数目的位,用以指示有安排一或多个写入时间未定的指令写入寄存器。未定栏位1511可在指令的派发时间设置或修改且在未定寄存器写入时间确定之后复位(清零)。复位操作可由解码/发射单元13、加载/存储单元17(例如,在数据命中之后)或功能单元20(例如,在int div操作确定做除法运算所需的位数之后)以及微处理器中涉及执行写入时间未定指令的任何其它单元来发起。在一些实施例中,未定栏位1511可包含两个位,有四个状态可以额外记录三个写入寄存器时间未定的派发指令。在又一些其它实施例中,未定栏位1511可包含三个位、四个位等,以记录多个有未

定写入时间的派发指令。

38.写入计数栏位1513记录下一(等待派发的)指令写入寄存器之前所需的频率周期数,此栏位还可被称作记录写入计数值的写入计数栏位。换句话说,写入计数栏位1513记录先前派发的指令完成操作且将结果数据回写到寄存器所需的频率周期数。写入计数栏位1513的写入计数值是根据派发指令时的写入时间来设置。接着,计数值每一频率周期皆向下计数(即,递减一),直到计数值变为零为止(即,这是一个自复位计数器)。举例来说,add指令的写入时间为2个频率周期,则写入计数栏位1513的计数值在为目的地寄存器派发add指令时设置为2且在计数器栏位达到0时自复位(self-reset)。计数值3表示结果数据将在3个频率周期后回写到对应于记分板条目的寄存器,计数值1表示结果数据将在此频率周期中回写到寄存器,且计数值0表示存取该寄存器没有数据相依性问题。

39.记分板条目的功能单元栏位1515纪录将回写到寄存器的功能单元20(由所发出指令指定)。举例来说,功能单元栏位1515记录为alu表示结果数据将从alu功能单元回写到寄存器。在一些实施例中,功能单元栏位1515中所记录的功能单元可在写入计数栏位1513达到值1时将来自该功能单元的结果数据转发到下一指令的来源操作数。

40.图3b是根据本发明的一些实施例的记分板条目的结构的图标。具有记分板条目1520(0)-1520(n)结构的第二记分板152被设计用以解决派发指令写入到一寄存器而相对应的记分板条目纪录有更前面的指令要读取此寄存器的冲突,即war数据相依性的冲突。第二记分板还可被称作处理war数据相依性的war记分板。记分板条目1520(0)-1520(n)中的每一个条目包含未定栏位1521和读取计数栏位(还可被称作计数栏位)1523。功能单元栏位在war记分板的实施方案中可以省略。未定栏位1521包含一个位值,用以表示对应于记分板条目的寄存器的读取时间是确定还是未定。未定栏位1521的操作和功能类似于未定栏位1511,因此,出于简洁的目的省略其细节。读取计数栏位1523记录一个读取计数值,用以表示先前的派发指令要读取对应寄存器的频率周期数。读取计数栏位1523还可被称作存储读取计数值的读取计数栏位。类似于写入计数栏位1513的写入计数值,读取计数值每一频率周期皆向下计数,直到读取计数值达到0为止。除非另外有描述,否则(读取)计数栏位1523的操作和功能类似于(写入)计数栏位1513,且因此省略其细节。

41.读取/写入控制单元16配置成记录寄存器组14的读取端口和/或写入端口在未来的数个频率周期内的可用状态以用于安排待派发指令的存取。在派发指令时,基于指令所指定的访问时间,解码/发射单元13存取读取/写入控制单元16以检查寄存器组14的读取端口和/或写入端口的可用状态。详细地说,读取/写入控制单元16根据读取端口的可用状态选择未来某一时间当作预定读取时间以将来源操作数读取到功能单元20,且根据写入端口可用状态选择未来某一时间当作预定写入时间以回写来自功能单元20的结果数据。在实施例中,读取/写入控制单元16可包含一个读取移位器161和一个写入移位器163以如上文所述用于安排读取端口和写入端口的使用。

42.图4是根据本发明的一些实施例中,与寄存器组的读取端口配合的读取移位器161的图示。图5为根据本发明的一些实施例中,与寄存器组的写入端口配合的写入移位器163的图示。寄存器组14的每一个读取端口皆有一个配合的读取移位器161,且寄存器组14的每一个写入端口皆有一个配合的写入移位器163。在实施例中,多个读取移位器161和多个写入移位器163可包含于读取/写入控制单元16中。然而,本发明不限于此。在一些其它实施例

中,读取端口和写入端口不是读取/写入控制单元16的一部分。专用读取和写入端口用于使未定读取和写入时间的指令能够动态读取和写入寄存器组14。

43.参考图4,读取移位器161包含多个条目1610(1)~1610(m),其中每一条目可包含读取有效栏位1611及地址栏位1613,且m为大于1的整数。条目1610(1)-1610(m)中的每一项各自代表未来的一个频率周期,且记录对应读取端口在所述频率周期中的可用状态。举例来说,条目1610(1)指示读取端口在紧接着的下一个频率周期的可用状态,而条目1610(m)指示读取端口在未来的第m个频率周期中的可用状态。参考图4,条目1610(1)=1610(m)中,每一频率周期最底下的条目将被移出,且对时间m分配一个新的条目。举例来说,最底条目1610(1)将立即在下一频率周期中移出。在实施例中,读取有效栏位1611记录一个读取有效值(“rd”),用来标记对应的频率周期中读取端口的可用状态。举例来说,第x条目中的读取有效栏位1611(x)若非零值,表示读取端口在未来的第x个频率周期处于忙碌状态,其中x大于1且小于m。第x条目中的读取有效栏位1611(x)若为零值表示对应读取端口在未来的第x个频率周期处于空闲状态可以自由存取。地址栏位1613记录从寄存器组14读取数据的寄存器地址(“rd_addr”)。举例来说,条目1610(1)表示相应的读取端口在紧接的下一频率周期会忙于从寄存器7(即,地址“r7”)读取数据。在一些替代实施例中,读取移位器161的每一条目中会存在更多或更少的栏位用于记录其它信息。

44.在派发指令之前,解码/发射单元13检查读取/写入控制单元16以判断寄存器组14的读取端口在指令的读取时间的可用状态。举例来说,读取时间为x个频率周期。读取/写入控制单元16检查读取移位器161的第x条目以判断在未来的第x个频率周期处读取端口是否空闲。如果可用读取端口的数目在读取时间大于或等于指令所需的读取端口的数目,那么解码/发射单元13可派发并安排指令在第(x+1)个频率周期执行。解码/发射单元13将派发指令的每一来源寄存器所预约到的读取端口发送到执行队列19,使得执行队列19知道将来源操作数数据提取到功能单元20的确切读取端口。对派发指令的每一有效来源寄存器皆设定其读取端口的读取有效栏位1611和读取地址1613。如果可用读取端口的数目小于所需读取端口的数目,那么解码/发射单元13可暂停指令且在下一频率周期中重新检查读取移位器。在所安排的读取时间,读取移位器将读取有效值rd和寄存器地址rd_addr提供给寄存器组14以读取来源寄存器。

45.参考图5,写入移位器163(可被称为延迟时间移位器)包含多个条目1630(1)-1630(p),其中每一条目包含回写有效栏位(“wr”)1631、写入地址栏位(“wr_addr”)1633以及功能单元栏位(“funit”)1635,其中p为大于1的整数。1630(1)-1630(m)中的每一个条目对应未来的一个频率周期,且记录对应写入端口在所述频率周期中的可用状态。举例来说,条目1630(1)表示写入端口在紧接着的下一频率周期的可用状态,且条目1630(p)指示写入端口在未来的第p个频率周期中的状态。参考图5,条目1630(1)-1630(p)中每一个频率周期都会移出最底部的条目。举例来说,最底条目1630(1)将在紧接着的下一频率周期中移出,且针对时间m配置一个新条目。在实施例中,回写有效栏位1631记录回写有效值(“wr”),所述回写有效值表示写入端口在对应于所述条目的频率周期的可用状态。举例来说,第y条目中的回写有效栏位1631(y)中,非零值表示写入端口在未来的第y频率周期将会是忙碌的,其中y大于1且小于p。第y条目中的读取值栏位1631(y)中,零值表示写入端口在未来的第y个频率周期可以自由存取。写入地址栏位1633纪录寄存器组14中的寄存器的地址(“wr_addr”),以

让功能单元将结果数据回写到所述寄存器。功能单元栏位1635纪录将结果数据回写到写入端口的功能单元20或加载/存储单元17(“funit”)。举例来说,写入移位器163的第一条目1630(1)表示写入端口在紧接着的下一频率周期中将为忙碌的,其中功能栏位1635记录alu 0将把结果数据回写到写入地址栏位1633所记录的寄存器22(“r22”)内。

46.在派发指令之前,解码/发射单元13检查读取/写入控制单元以判断寄存器组14的写入端口在指令的写入时间的可用状态。举例来说,写入时间为y个频率周期。读取/写入控制单元16检查写入移位元器161的第y条目以判断在未来的第y个频率周期处写入端口是否空闲。如果在写入时间y处可用写入端口的数目大于或等于指令所需的写入端口的数目,那么解码/发射单元13可派发并安排指令在第y个频率周期(即,所安排的写入时间)执行完成。对所派发指令的每一有效目的地寄存器皆设定回写有效栏位1631、功能单元1635以及目的地地址1633。如果可用写入端口的数目小于所需写入端口的数目,那么解码/发射单元13可暂停指令且在下一频率周期中重新检查写入移位器。在所安排的写入时间,读取/写入端口控制器根据记录于功能单元栏位1635中的功能单元20取得来自该单元的结果数据,且将结果数据写入到写入地址栏位1633中所指定的寄存器。

47.参考图1,执行队列19配置成纪录分派到功能单元20的已派发指令。功能单元20可包含但不限于:整数乘法、整数除法、算术逻辑单元(arithmetic logic unit,alu)、浮点单元(floating-point unit,fpu)、分支执行单元(beu)、一个接收经解码指令且执行其操作的单元等。在实施例中,每一个执行队列19皆耦合到或专用于一个功能单元20。在其它实施例中,一个执行队列19可耦合到多个功能单元20。举例来说,执行队列19a耦合在解码/发射单元13与对应功能单元20a之间以让需要使用功能单元20a执行的指令排队等候并分派。类似地,执行队列19b耦合在解码/发射单元13与对应功能单元20b之间,且执行队列19c耦合在解码/发射单元13与对应功能单元20c之间。在实施例中,执行队列19d、执行队列19e耦合在解码/发射单元13与加载/发射单元17之间以处理加载/存储指令,细节稍后会详细说明。执行队列19d、执行队列19e还可分别被称作标记执行队列(tag-execution queue,teq)19d和数据执行队列(data-execution queue,deq)19e,这将在下文详细地描述。

48.图6是根据本发明的一些实施例的执行队列19的图标。执行队列19可包含多个条目190(0)-190(q),用于以将要发送到功能单元20的次序来记录由解码/发射单元13发出的指令的信息,其中q为大于0的整数。在一实例中,执行队列19的每一条目包含有效栏位191、执行控制数据栏位193、数据栏位195以及读取计数栏位197,在图6中分别标记为“v”、“ex_ctrl”、“data”以及“rd_cnt”。在其它实施例中,执行队列的每一条目可能记录更多或更少的栏位,且数据栏位195除立即数据之外可具有其它数据。

49.有效栏位191表示条目是否有效(例如,“1”代表条目有效而“0”代表条目无效)。执行控制信息栏位193和数据栏位195存储功能单元20的执行控制信息和指令的立即数据,其中立即数据由指令编码求得。读取计数栏位197记录指令的读取计数值rd_cnt,用以表示指令的读取时间。存储于读取计数栏位197中的读取时间每一频率周期皆向下减一,直到读取计数rd_cnt达到零为止。当读取计数栏位197中的读取时间为0时,执行队列19将有效指令分派到功能单元20。

50.执行队列19可包含或耦合到一个累积计数器199,用于存储累积计数值acc_cnt,所述累积计数值每一频率周期向下减一,直到计数值变成零为止。累积计数为零代表执行

队列19为空。累积计数器199的累积计数值acc_cnt代表未来可将下一指令分派到功能单元20或加载/存储单元17的时间(即,频率周期数)。解码/发射单元13中的下一指令可以派发到执行队列19时,根据累积计数器199的累积计数值安排此指令分派到功能单元20或加载/存储单元17的时间。在一些实施例中,指令的读取时间就是累积计数值,而下一指令的累积计数值可根据当前acc_cnt和指令吞吐时间的总和(acc_cnt=acc_cnt+inst_xput_time)来设置。在一些其它实施例中,读取时间会需要调整(这时读取时间大于当前累积计数),则下一指令的累积计数值需根据指令的读取时间(rd_cnt)和指令的吞吐时间的总和(acc_cnt=rd_cnt+inst_xput_time)来设置。在一些实施例中,读取移位器161和写入移位器163设计成与执行队列19同步。举例来说,执行队列19可将指令分派到功能单元20或加载/存储单元17,同时根据读取移位元器161从寄存器组14读取来源寄存器,且来自功能单元20或加载/存储单元17的结果数据也同时根据写入移位元器163回写到寄存器组14。

51.参考图1,加载/存储单元17耦合到解码/发射单元13以处理加载和存储指令。在实施例中,解码/发射单元13将加载/存储指令派发成两个微操作,包含一个标记微操作和一个数据微操作。标记微操作被发送到teq 19d,而数据微操作被发送到deq 19e。在一些实施例中,加载/存储指令的微操作的吞吐时间为1个频率周期。teq 19d和deq 19e为独立的操作,且teq 19d先发出用于标记操作的标记微操作,再由deq 19e发出用于数据操作的数据微操作。

52.数据快取18耦合到寄存器组14、内存30以及加载/存储单元17,且配置成用以暂时存储从内存30提取的数据。加载/存储单元17存取数据快取18以用于加载数据或存储数据。数据快取18存储了包含来自内存30中连续数据字节的许多快取列。数据快取18的快取列被组织为类似于指令快取11的直接映像、完全关联映像或组关联映像,但其映像方式不需要与指令快取11相同。

53.数据快取18可包含标记数组(tag array,ta)22及数据数组(data array,da)24以用于分别存储一部分由微处理器10频繁使用的地址和数据。标记数组22中的每一标记对应于一条数据数组24中的快取列。当微处理器10需要执行加载/存储指令时,微处理器10首先通过将加载/存储地址与存储于标记数组22中的标记进行比较来检查加载/存储数据是否存在于数据快取18中。如果加载/存储地址与标记数组中的一个标记匹配(命中快取),那么使用数据数组24中对应的快取列做加载/存储数据存取。加载指令从数据数组24的快取列提取数据以写入到寄存器组14的目的地寄存器,而存储指令将来自寄存器组14的来源寄存器的数据写入到数据数组24中的快取列。如果加载/存储地址没有匹配到标记数组22中的任何条目(未命中快取),那么微处理器10可存取内存30以找到所需数据。在命中快取的情况下,加载/存储指令的执行延迟时间为确定的(例如2个、3个、4个或任何数目个频率周期)。在未命中快取的情况下,加载/存储指令的执行延迟时间为6个频率周期或更多。加载指令的执行延迟时间基本上是无法事先得知的,取决于是否命中快取以及内存30的延迟时间。

54.标记操作包含通过加载/存储单元17中的地址产生单元(address generation unit,agu)171计算地址,以及使用所计算的地址来存取标记数组22和数据翻译后备缓冲器(data translation look-aside buffer,数据tlb)(未示出),后者用于虚拟地址与物理地址之间的转译。地址计算为一加法运算,使用来自寄存器组14的来源寄存器和来自图6的数

据栏位195的立即数据(“imm data”)相加。图4的读取移位器161从寄存器组14读取来源寄存器的时机被安排与派发从teq 19d到agu 171的标记操作的时机同步。在一些实施例中,虚拟地址和物理地址是相同的,所以不需要数据tlb。teq 19a将标记操作分派到加载/存储单元17的地址产生单元(agu)171以计算加载/存储地址。加载/存储地址用于存取数据快取18的标记数组(ta)22。快取的命中与否和命中路线(组关联映像)会被记住以便由deq 19b的数据操作运用此信息以存取da 24中的命中路线的快取列。如果同时存取da 24与ta 22,那么da 24中的组关联映像的所有路线皆需要读取。在实施例中,先ta 22再da 24的顺序访问允许只读取da 24的单个路线,因此da 24可节省相当大的功率且减少数据组的存取冲突。

55.对于加载指令,在快取命中的情况下,数据从da 24提取且经过写入移位器163的写入控制而回写到寄存器组14的目的地寄存器。在快取未命中的情况下,则将记分板15中的目的地寄存器的状态更改为未定,且从内存30提取加载数据。随后,来自内存30的加载数据经过专用写入端口回写到寄存器组14的目的地寄存器。实作上,来自内存30的加载数据会写入到数据未命中缓冲器(未示出),然后数据未命中缓冲器将回写到寄存器组14的目的地寄存器且最终将快取列数据写进数据快取24。

56.对于存储指令,在快取命中的情况下,存储数据由读取移位器21安排成在需要写入到da24前,实时从寄存器组14读取。在快取未命中的情况下,可将存储数据发送到加载/存储单元17中的存储未命中缓冲器(未示出)。存储指令传统上的执行方式,可以同时从寄存器组14读取用于标记地址的来源寄存器和用于存储数据的来源寄存器,在此情况下,需要存储缓冲器来保留存储数据直到写入到da 24为止。在本发明中,将存储数据写入到da24的时间(假设快取命中)是确定的,因此,读取端口控制安排成在需要写入da24之前,“实时(just-in-time)”从寄存器组14读取用于存储数据的来源寄存器,因此不需要存储缓冲器。当快取未命中,存放存储数据的来源寄存器在需要将存储数据写入到数据快取前并不需事先从寄存器组14读取,即这是所述来源寄存器的“及时”读取。

57.对于快取未命中,加载/存储单元17可允许多个送往内存30的待办快取未命中请求。这些待办未命中请求被放在加载/存储单元17中的未命中请求队列(未示出)中。新的快取列从内存30提取到数据快取18中的未命中数据缓冲器(未示出)中。未命中数据缓冲器可以有多个快取列。另外,数据快取18中被替换的快取列可能是脏的,这些脏的快取列必须在来自内存30的新快取列可写入到数据快取18之前回写到内存30。在驱逐到内存30之前,脏的快取列从数据快取18提取到驱逐缓冲器中。驱逐缓冲器可实作为未命中数据缓冲器的一部分。后续加载/存储指令皆必须检查逐出缓冲器、未命中请求队列以及未命中数据缓冲器以检测是否有所需数据在里面并转发。

58.加载/存储指令可具有精确例外事件,发生时必须将所有后续指令从执行管线舍弃。类似于分支指令,加载/存储指令之后的所有后续指令无法回写到寄存器组14,直到加载/存储指令执行完为止。未命中快取的加载/存储指令可以有数据错误例外事件,是一种不精确例外事件,处理方式是停止解码/发射单元13继续派发指令且等待所有在执行管线中的指令完成之后才触发此例外事件。中断类似于不精确例外事件,处理方式是停止解码/发射单元13继续派发指令且在所有执行管线中的指令完成之后才触发中断。

59.在下文中,将解释使用记分板15、执行队列19中的指令的累积吞吐时间以及读取/

写入控制单元16以派发具有确定访问时间的指令的过程。

60.当解码/发射单元13从指令快取11接收到指令时,解码/发射单元13在派发所述指令之前存取记分板15以检查任何数据相依性。确切地说,检查对应于寄存器的记分板条目的未定栏位和计数栏位以用于判断先前派发的指令是否具有确定访问时间。在一些实施例中,还可存取累积计数器199的当前累积计数值以用于检查功能单元20的可用状态。如果先前派发的指令(即,第一指令)和新接收待派发的指令(即,第二指令)存取同一寄存器,那么第二指令会有数据相依性。第二指令会被接收下来并且在第一指令之后派发。通常,数据相依性可分类为写后写(waw)相依性、写后读(raw)相依性以及读后写(war)相依性。waw相依性是指在第二指令可写入到寄存器之前第二指令必须等待第一指令将结果数据回写到同一寄存器的状况。raw相依性是指在第二指令可从寄存器读取数据之前第二指令必须等待第一指令回写到同一寄存器的状况。在raw状况下,可将回写数据从功能单元转发到第二指令。war相依性是指在第二指令可写入到寄存器之前第二指令必须等待第一指令从同一寄存器读取数据的状况。通过上文所描述的记分板15和执行队列19,具有确定访问时间的指令可以派发并安排在一个未来时间执行以避开这些数据相依性。

61.在处置raw数据相依性的实施例中,如果写入计数栏位1513的写入计数值等于或小于待派发的指令的读取时间(即,inst_read_time),那么不存在raw相依性,且解码/发射单元可派发所述指令。如果写入计数栏位1513的计数值大于指令读取时间加1(即,inst_read_time+1),那么存在raw数据相依性,且解码/发射单元13可暂停指令的派发。如果写入计数栏位1513的写入计数值等于指令读取时间加1(即,inst_read_time+1),那么可从功能单元栏位1515中所记录的功能单元转发结果数据。在此情况下,具有raw数据相依性的指令仍可派发。功能单元栏位1515可用于转发来自所记录功能单元的结果数据到待派发指令的功能单元。在处置waw数据相依性的实施例中,如果写入计数栏位1513的写入计数值大于或等于待派发的指令的写入时间,那么存在waw数据相依性,且解码/发射单元13可暂停指令的派发。在处置war数据相依性的实施例中,如果读取计数栏位1523的读取计数值大于指令(即,目前待派发的指令)的写入时间,那么存在war数据相依性,且解码/发射单元13可能要暂停指令的派发。如果读取计数栏位1523的读取计数值小于或等于指令的写入时间,就没有war数据相依性,且解码/发射单元13可派发所述指令。应注意,所派发指令储放在执行队列19中且安排在未来的一个读取时间分派到功能单元20。

62.基于记分板15的计数栏位中的计数值,解码/发射单元13可预期寄存器的可用状态而将指令的执行安排存到执行队列19中,而该执行队列19可按照从解码/发射单元13接收到排队指令的次序将排队指令分派到功能单元20。执行队列19可累积执行队列19中排队指令的吞吐时间以预期功能单元20可用于执行下一指令的下一个可用频率周期。解码/发射单元13还可通过存取读取/写入控制单元16以在派发指令之前检查寄存器组14的读取端口和写入端口的可用状态而与寄存器组的读取端口和写入端口同步。举例来说,执行队列19中的第一指令的累积吞吐时间反映功能单元20将由第一指令占据达11个频率周期。如果第二指令的延迟时间是12个频率周期,那么结果数据将在未来的时间23(或从现在起的第23个频率周期)处从功能单元20回写到寄存器组14。换句话说,解码/发射单元13将确保来源寄存器和读取端口在第11个频率周期处是可以使用的以及用于写入目的地寄存器的写入端口相对于第二指令派发时间的第23个频率周期处是可以使用的。如果读取端口或写入

端口在对应的频率周期中为忙碌的,那么解码/发射单元13可暂停一个频率周期再检查寄存器和读取/写入端口的可用状态。

63.在管线微处理器中,减少解码/发射单元中任何指令(尤其是加载/存储指令)的暂停是很重要的,因其阻止指令流向前移动。具有确定访问时间的指令可通过使用如上文所描述的记分板15、读取/写入控制单元16以及执行队列19而派发到未来的特定时间。然而,因为数据相依性或指令存取寄存器的时间未定,具有未定访问时间的指令可能会在解码/发射单元13中暂停。加载指令就是一个例子,它回写到寄存器组14的目的地寄存器的执行延迟时间不能事先知道,而存储指令是另一个例子,它读取寄存器组14中的寄存器的读取时间也不能事先得知。有许多因素导致访问时间不能事先确定,例如但不限于快取是否命中、tlb是否命中、数据存储库(data bank)冲突以及外部内存访问时间。举例来说,加载指令的执行延迟时间取决于加载数据的位置,可能在数据快取或也可能在外部内存中。如果数据在数据快取中,可能需要2个频率周期来加载。然而,如果数据在耦合到微处理器的内存(例如,ram)中,那么可能需要50个频率周期到100个频率周期来加载。指令管线就要在解码/发射单元中暂停直到数据命中为止。下文描述一些实施例以说明fse微处理器如何处置具有未定访问时间的加载/存储指令。与其在指令解码/派发阶段暂停管线,fse微处理器将加载/存储指令安排到执行队列19d、执行队列19e内。

64.图7是根据本发明的一些实施例的数据执行队列(deq)19e的图示。deq 19e包含多个deq条目190e(0)-190e(3),以接收加载/存储指令的次序记录排队中的加载/存储指令的各种信息。也就是说,第一deq条目190e(0)中的排队指令比第二条目190e(1)中的排队指令先被接收到与安排派发到加载/存储单元17。每一deq条目对应于一个排队中的加载/存储指令,且包含有效栏位191(“v”)、执行控制信息栏位193(“ctrl/data”)、地址栏位192(“rd”)、未定载入栏位194(“unk_ld”)、未定存储栏位196(“unk_st”)以及前置计数栏位197(“pre_cnt”)。这些deq条目的栏位在从解码/发射单元13接收到加载/存储指令时(即,在解码/发射单元中的指令派发之后的第一频率周期)设置。当对应的加载/存储指令经确认并分派到加载/存储单元17时,该deq条目可以复位(作废)。有效栏位191指示条目是否有效(例如,“1”代表有效条目而“0”代表无效条目)。地址栏位192纪录加载/存储指令将要存取的寄存器。执行控制信息栏位193记录用于加载/存储单元17的执行控制信息和立即数据,这些值皆衍生自指令的机器码。未定加载栏位194纪录与先前加载指令有waw或raw数据相依性(按照定义加载指令具有未定写入时间)。举例来说,未定加载栏位194可在有waw或raw相依性的情况下设置。waw数据相依性源自当前指令为加载指令的情况,而raw数据相依性源自当前指令为存储指令的情况。未定存储栏位196纪录与先前存储指令的war数据相依性(按照定义存储指令具有未定读取时间)。未定载入栏位194和未定存储栏位196的值与记分板条目1510和1520的未定栏位1511和未定栏位1521的值相关联,稍后将详细地解释。如果当前加载/存储指令具有与前一指令的waw、war或raw数据相依性,那么对应于前一指令的记分板条目的计数值1513或计数值1523会被记录在前置计数栏位197中。当前加载/存储指令可具有多个数据相依性,在此情况下,将最差计数值(1513或1523)记录在前置计数栏位197中(即,来自对应的记分板条目的最大计数值)。前置计数值每一频率周期递减一(即,图7所图示的

“‑

1”方块)直到达到0为止,然后在此时间点,当前加载/存储指令相对于有确定访问时间的先前指令不再有数据相依性。应注意,当前加载/存储指令可以同时与具有确定

及未定访问时间的数个先前指令有多重数据相依性,在此情况下,栏位194、栏位196以及栏位197可能全部设置为非零值。deq 19e则必须等待到deq条目的未定加载栏位194中的未定载入计数、未定存储栏位196中的未定存储计数以及前置计数栏位197中的前置计数值达到0为止才能将对应于deq条目的加载/存储指令分派到加载/存储单元17。尽管图7仅图示了4个deq条目190e(0)~190e(3),但本发明并不意欲限制deq条目的数目。deq条目的数目可基于设计需求增加或减少。

65.在发出加载/存储指令的过程中,在将加载/存储指令发出到deq 19e之前,解码/发射单元13存取记分板15以检查加载/存储指令将要存取的寄存器的状态。在加载/存储指令的派发时间,将对应记分板条目中代表waw、war以及raw数据相依性的值与加载/存储指令一同发送到deq 19e。举例来说,未定加载栏位1511和存储栏位1521中的载入/存储未定状态以及写入计数栏位1513和读取计数栏位1523中的计数值可以连同加载/存储指令一起发送到deq 19e。加载/存储指令由解码/发射单元13以含一个标记微操作和一个数据微操作的两个微操作派发。标记微操作派发到teq 19d,而数据微操作派发到deq 19e。

66.如上文所描述,记分板条目的未定载入/存储栏位1511和1521可有多个记录位以纪录多个访问时间未定的加载/存储指令,其中加载指令会写到同一目的地寄存器或存储指令会读取同一来源寄存器。举例来说,2位最多可记录3个具有访问时间未定的指令,其中0(“00”)代表没有访问时间未定的指令派发到执行队列19,1(“01”)代表有一个访问时间未定的指令在执行队列19中排队,而3(“11”)代表有3个存取同一寄存器时间未定的指令在执行队列19中排队。在2位的实施例中,deq 19e可存储(或解码/发射单元13可派发到执行队列)的访问时间未定的指令的最大数目是3,以下称为事先决定好的未定数(或阈值)。如果访问时间未定的三个排队指令中的任一个的访问时间确定之前,解码/发射单元13收到访问时间未定的第四指令,那么解码/发射单元13可暂停管线。本发明并不意欲限制deq 19e存储访问时间未定的指令的数目。在一些其它实施例中,记分板条目的未定栏位可包含3位、4位等,其中3位可让记分板条目有能力纪录7个时间未定的指令已被派发且时间尚待确定。这里使用派发加载/存储指令时涉及raw、waw以及war数据相依性的实施例来说明加载/存储指令的处理。在下文中,第一指令是指已经派发到deq 19e且在deq 19e中排队的指令,其中与第一指令有关的信息(即,表示读取时间或写入时间的未定加载/存储值和确定计数值)记录在记分板条目和deq 19e中。第二指令是指在第一指令之后将要由解码/发射单元13派发到执行队列19的指令。应注意,相对应的记分板条目的未定加载栏位1511、存储栏位1521中的未定载入计数将个别受到检查,以判断未定载入计数或未定存储计数在发出第二指令之前是否等于或大于事先决定好的未定数(例如,如果此栏位宽度为2位,这个数可以为3)。如果记分板条目中的未定加载/存储值中的一个等于或大于事先决定好的未定数,那么解码/发射单元13可暂停第二指令的派发。如果为否,记分板条目的未定加载/存储值将在派发有数据相依性的第二指令,且此相依性的访问时间未定时,递增1。

67.图8为根据一些实施例中派发有确定访问时间的waw数据相依性的加载指令的操作的图标。在实施例中,通过解码/发射单元13接收加载指令(即,第二指令),其中加载指令将加载数据回写到寄存器r(y)。在发出加载指令之前,解码/发射单元13存取记分板条目1510(y)以检查数据相依性。记分板条目1510(y)纪录alu指令(即,第一指令)将基于写入计数栏位1513和功能单元栏位1515中的信息在10个频率周期内写入寄存器组14的寄存器r

(y)。由于alu指令具有确定访问时间,因此与alu指令有waw数据相依性的加载指令可被称为访问时间确定的waw数据相依性。在实施例中,解码/发射单元13将该加载指令连同记分板151中的记分板条目1510(y)中的记分板值派发到deq 19e的下一尚未使用的deq条目(例如,190e(0))。

68.在派发加载指令时,解码/发射单元13将更新记分板条目1510(y)的未定栏位1511以纪录最新发出的指令为一加载指令,且此指令对于寄存器r(y)的访问时间未定。图8还示出在发出加载指令之前和之后的记分板条目1510(y)的更动。详细地说,在发出加载指令之后,记分板条目1510(y)中的未定栏位1511的未定值将递增一,且功能单元栏位改变为“加载单元”。在实施例中,记分板条目1510(y)中的写入计数栏位1513中的写入计数值不一定会更新。由于未定栏位1511被设定,因此下一指令存取对应于记分板条目1510(y)的寄存器时将预期先前派发的指令是一个访问时间未定的指令。应注意,在派发加载指令前,写入计数栏位1513的写入计数值(即,“10”)将与第二指令一同派发到deq 19e。根据如图8中的deq 19e例子,加载指令将放置于(下一个尚未使用的)deq条目190e(0)中,且deq条目190e(0)的栏位将根据加载指令和与加载指令一起派发的记分板值而配置。详细地说,将有效栏位改为“1”以标示该条目使用中,执行控制信息栏位193改为存储加载指令的控制信息,地址栏位192改为“r(y)”以纪录加载指令将回写到寄存器r(y)。将记分板151的记分板条目1510(y)的未定栏位1511复制到deq条目190e(0)的未定载入栏位194,且deq条目190e(0)的未定存储栏位196将为第二记分板152的条目1520(y)的未定栏位1521的复本,在此实施例中假设为0。由于在加载指令之前的第一指令为具有确定访问时间的alu指令,因此记分板151的计数栏位1515的计数值将(在派发之前)复制到deq条目190e(0)的前置计数栏位197。将前置计数栏位197中的前置计数值设置为9,此值从派发之前的记分板条目150(y)中的计数值10衍算而来。由于deq条目190e(0)是在读取写入计数栏位1513中的写入计数值10之后一个频率周期后设定,因此当分配加载指令到deq条目190e(0)时,计数值10递减一(即,9)。换句话说,deq条目190e(0)中的前置计数值记录alu指令将结果数据回写到寄存器r(y)的所需频率周期数。deq条目190e(0)每一频率周期皆将前置计数值向下减一,直到前置计数值达到0为止(代表此时不再有waw数据相依性),然后将deq条目190e(0)中的加载指令派发到加载/存储单元17。在另一实施例中,前置计数值197可进一步减掉加载指令的最小延迟时间,即,如果加载指令的最小延迟时间为3个周期(而不是1个周期),那么前置计数值197设置为7。基本上,加载指令从派发时间起算,最早需要11个周期才会回写到r(y)。这边要特别指出,teq 19d可以在deq 19e可根据deq条目190e(0)发出加载指令之前数个频率周期就存取标记数组以决定快取命中与否,如果快取命中,可提早数个频率周期从da 24取得加载数据,但必须在加载数据可通过专用写入端口回写到寄存器组14的寄存器r(y)之前等待前置计数值降为零。teq 19d中只要快取未命中即可在deq 19e将加载指令分派到加载/存储单元17之前启动外部内存存取。加载指令有可能同时具有确定waw和war数据相依性,在此情况下,pre_cnt栏位197设成第一记分板151和第二记分板152的写入计数值1513和读取计数值1523中的较大值。

69.图9为根据一些实施例用以派发具有未定访问时间的waw数据相依性的加载指令的操作的图标。在实施例中,解码/发射单元13收到一个加载指令(即,第二指令或第二加载指令),且此加载指令将加载数据回写到寄存器r(x)。在发出加载指令之前,解码/发射单元

13存取记分板条目1510(x)以检查数据相依性。根据记分板条目1510(x)的未定栏位1511(“1”),记分板条目1510(x)显示有一个先前的加载指令(即,第一加载指令)会写入到寄存器组14的寄存器r(x)。与第一加载指令有waw数据相依性的第二加载指令可被称作具有未定访问时间的waw数据相依性。在实施例中,解码/发射单元13将第二加载指令连同记分板151中的记分板条目1510(x)中的记分板值一起派发到deq 19e的下一个尚未使用的deq条目(即,190e(1))。应注意,实施例还可存取第二记分板152的记分板条目1520(x)以检查寄存器r(x)的war数据相依性。实施例出于简洁的目的仅假设存在waw或war数据相依性。在其它实施例中,寄存器r(x)除上文所描述的waw数据相依性之外还会有war数据相依性。在这类实施例中,第二记分板152的记分板条目1520(x)的值(即,未定值和读取计数值)会与第二加载指令一起派发。

70.在第二加载指令派发时,解码/发射单元13将更新记分板条目1510(x)的未定栏位1511以纪录最新发出的指令为再一个对寄存器r(x)访问时间未定的加载指令,如图9所示。详细地说,在发出第二加载指令之后,记分板条目1510(x)中的未定栏位1511的未定值将递增一(即,变成值“2”)。由于前一个存取寄存器r(x)的已派发指令也是加载指令,因此记分板条目1510(x)的功能单元栏位1515已经设为加载单元。因此,实施例可或可不将记分板条目1510(x)的功能单元栏位1515改变为“加载单元”,而具体规范此作法并非本发明的意图。参考如图9中所示的deq 19e,第二加载指令将放置于(下一个尚未使用的)deq条目190e(1)中,且deq条目190e(1)的栏位将根据第二加载指令和与第二加载指令一起派发的记分板值而设定。详细地说,将有效栏位改变为“1”以标示该条目使用中,改变执行控制信息栏位193以存储第二加载指令的控制信息,将地址栏位192改变为“r(x)”以纪录第二加载指令将回写到寄存器r(x)。记分板条目1510(x)的未定栏位1511(具有值“1”)将复制到deq条目190e(1)的未定加载栏位194,以纪录在第二加载指令之前存在具有写入时间未定的第一加载指令。由于第二加载指令还具有未定访问时间,因此在发出第二加载指令之后,记分板条目1510(x)的未定栏位1511的未定值将更新为“2”。190e(0)条目的未定存储栏位196将是记分板152的条目1520(x)的未定栏位1521的副本,在此实施例中假设为0。详细地说,deq条目190e(1)的未定加载栏位194的值将从“0”改变为“1”,以便纪录在第二加载指令之前存在先前加载指令。在实施例中,由于第一加载指令具有未定访问时间,因此前置计数栏位197将为0。执行队列19e维护未定加载计数且监视用于回写到寄存器r(x)的专用写入端口(结果总线32中的一个),从而递减deq 19e中的未定载入计数,与记分板151作法一致。在一些实施例中,加载/存储单元17可将回写信号连同寄存器r(x)发送到deq 19e和记分板151以递减未定载入计数。如之前所提到,在将对应于deq条目的加载/存储指令分派到加载/存储单元17之前,deq 19e要等到deq条目190e的未定载入栏位194中的未定载入计数、未定存储栏位196中的未定存储计数以及前置计数栏位197中的前置计数值达到0为止。

71.图10a与图10b为根据一些实施例,发出具有确定访问时间的raw数据相依性的存储指令的操作的图标。参考图10a,解码/发射单元13收到一个存储指令(即,第二指令),其中此存储指令将从寄存器r(s)读取存储数据而将之存储至(例如)内存30。如果存储指令的来源操作数指定寄存器r(s),那么存储指令会与alu指令有raw数据相依性。在发出存储指令之前,解码/发射单元13存取第一记分板151以检查数据相依性,例如基于第一记分板151中的未定栏位1511检查是否有先前的加载指令有数据相依性或基于写入计数栏位1513检

查是否有确定访问时间的其它指令(例如,alu)。在实施例中,第一记分板151的记分板条目1510(s)基于写入计数栏位1513和功能单元栏位1515中的信息,纪录alu指令(即,第一指令)将在7个频率周期内写入到寄存器组14的寄存器r(s)。由于alu指令具有确定访问时间,因此与alu指令有raw数据相依性的存储指令可被称为有确定访问时间的raw数据相依性。在实施例中,解码/发射单元13将存储指令连同记分板151中的记分板条目1510(s)中的记分板值一起派发出到deq 19e的下一个尚未使用的deq条目(即,190e(2))。

72.参考图10a中的deq 19e,存储指令将放置于(下一个尚未使用的)deq条目190e(2)中,且deq条目190e(2)的栏位将根据存储指令和与之一起派发的记分板值而设定。详细地说,将有效栏位改变为“1”以标记此条目使用中,改变执行控制信息栏位193以存放存储指令的控制信息,且将地址栏位192改变为“r(s)”以纪录存储指令将会读取寄存器r(s)。由于存储指令只会与写入到r(s)的前一指令有raw数据相依性,因此记录在第一记分板151中的各种记分板值会连同存储指令一起派发到deq 19e。这边要特别指出,存储指令不会有来自第二记分板152的数据相依性(即,rar不构成数据相依性),所以执行队列190e(2)的未定存储栏位196中的未定存储计数对于存储指令而言会是0。举例来说,记录在第一记分板151中的未定栏位1511、写入计数栏位1513中的值可以发送到deq 19e。第一记分板151的记分板条目1510(s)的未定栏位1511将复制到deq条目190e(2)的未定载入栏位194。由于存储指令的前一道指令为具有确定访问时间的alu指令,所以如图10a所示,第一记分板151的计数栏位1515的写入计数值(即,“7”)(派发之前)将与存储指令一同发送到deq条目190e(2),用来设定deq条目190e(2)的前置计数栏位197。参考图10a中的deq 19e,将前置计数值设定为6,此值是在派发之前从记分板条目1510(s)中的写入计数值7衍算出来的。由于deq条目190e(2)在读取写入计数栏位1513中的写入计数值7之后的一个频率周期设定,因此当将存储指令放置在deq条目190e(2)中时,计数值7已经被递减一(即,变成6)。换句话说,deq条目190e(2)中的前置计数值记录alu指令未来还要多少频率周期才会将结果数据回写到寄存器r(s)。deq 190e(2)针对每一频率周期将前置计数值向下计数一,直到前置计数值达到0为止,这时代表先前发出,有确定访问时间的指令不再有raw数据相依性。deq 190e(2)中的存储指令会在deq条目190e(2)的栏位194,196以及197为零时,才派发到加载/存储单元17。在另一实施例中,前置计数197值1代表来自alu的结果数据回写到寄存器组14时,同时deq条目190e(2)可连同从alu转发的数据一起派发到加载/存储单元17。deq条目190e(2)要派发到加载存储单元17还必须满足其它两个条件:(1)未定载入栏位194中的未定载入计数应为零,和(2)必须有一个读取端口可用于转发alu结果数据,这可由解码/发射单元13先安排。在一些实施例中,deq 19e检查读取端口移位器161以获得读取端口的可用状态。

73.参考图10b,在派发存储指令之后,解码/发射单元13将更新第二记分板152中的记分板条目1520(s)的未定栏位1523以纪录最新发出的指令是一个存储指令,对寄存器r(s)具有未定读取时间。详细地说,记分板条目1520(s)中的未定栏位1521的未定值将加一(从“0”变为“1”,如图10b中的第二记分板152(派发之后)的未定栏位1521所示)。

74.图11a和图11b为根据一些实施例用以派发具有未定访问时间的raw数据相依性的存储指令的操作的图标。参考图11a,解码/发射单元13接收了一道存储指令(即,第二指令),此存储指令将从寄存器r(z)读取存储数据以写入到da24。在派发存储指令之前,解码/发射单元13存取第一记分板151(即,记分板条目1510(z)以检查数据相依性,例如基于第一

记分板151中的未定栏位1511检查是否有先前的加载指令或基于写入计数栏位1513检查是否有确定访问时间的其它指令。根据记分板条目1510(z)的未定栏位1511(“2”),有两个先前加载指令(即,第一指令)会写入到寄存器组14的寄存器r(z)且访问时间未定,并且记分板条目1520(z)显示有一个先前存储指令(即,第一指令)会读取寄存器组14的寄存器r(z),且访问时间未定。存储指令与先前加载指令有raw数据相依性可被称作具有未定访问时间的raw数据相依性。在实施例中,解码/发射单元13将存储指令连同记分板151中的记分板条目1510(z)中的记分板值一起派发到deq 19e的下一个尚未使用的deq条目(例如,190e(3))。

75.参考图11a中的deq 19e,存储指令将分配到(下一个尚未使用的)deq条目190e(3),且deq条目190e(3)的栏位将根据存储指令和与存储指令一起派发的记分板值而设定。详细地说,将有效栏位改变为“1”以标记此条目使用中,改变执行控制信息栏位193以存储存储指令的控制信息,将地址栏位192改变为“r(z)”以纪录存储指令将会读取寄存器r(z)。记分板151的写入未定栏位1511和写入计数栏位1513中的值用于设定deq条目190e(3)中的栏位194和栏位197。deq条目190e(3)中的栏位196对于存储指令必须为0。详细地说,将第一记分板151的写入未定栏位1511中的值(即,值“2”)复制到未定加载栏位194作为未定加载计数。在实施例中,由于条目1510(z)的未定栏位1511有设值,因此前置计数栏位197将为0。执行队列19e维护未定加载计数且监视专用写入端口(结果总线32中的一个)以检测回写到寄存器r(z)的操作,从而以与第一记分板151相同的方式递减deq 19e中的未定加载计数。在一些实施例中,加载/存储单元17可将回写信号连同寄存器r(z)发送到deq 19e和第一记分板151以递减未定载入计数。如上文所描述,在将对应于deq条目的加载/存储指令分派到加载/存储单元17之前,deq 19e必须等到deq条目的未定加载计数、未定存储计数以及前置计数值达到0为止。在另一实施例中,来自加载/存储单元17的回写信号指示加载结果数据回写到寄存器组14且同时deq条目190e(3)可从加载/存储单元17转发数据而派发到加载/存储单元17。deq条目190e(3)要派发到加载存储单元17还必须满足两个其它条件:(1)未定载入栏位194中的未定载入计数应为一,和(2)要有一个使用读取端口或使用加载/存储单元17的内部总线转发加载结果数据的机制。在一些实施例中,deq 19e检查读取端口移位器161以获得读取端口的使用状态。

76.参考图11b,在发出存储指令之后,解码/发射单元13将更新记分板条目1520(z)的未定栏位1521以纪录最新发出的指令为一个对寄存器r(z)读取时间未定的存储指令。详细地说,记分板条目1520(z)中的未定栏位1521的未定值将加一(即,其值变成“2”)。

77.下面解释第二指令在以下条件派发的实施例:至少一个待由第二指令写入的寄存器与在未来时间读取至少一个寄存器的第一指令有war数据相依性,其中第一指令可具有确定读取时间或未定读取时间。一般来说,解码/发射单元13将存取第一记分板151和第二记分板152,其中使用第二指令将来自第一记分板151和第二记分板152的记分板信息发送到deq 19e以设定deq条目。在发出第二指令之后,可更新第一记分板151和第二记分板152的对应条目。在其中一个实施例中,仅更新第一记分板151中的写入未定栏位1511以纪录对应寄存器有一个先前派发过的指令,写入时间未定,因为第二指令(加载指令)将会回写到对应寄存器。然而,这并非本发明意欲规范限制的行为。在其它实施例中,记分板条目的更多栏位可一起更新以记录所派发的第二指令的信息。举例来说,功能单元栏位1515还可更

新以记录写到对应寄存器的加载指令具有未定访问时间。

78.图12a和图12b是根据一些实施例,派发一个访问时间确定,有war数据相依性的加载指令的操作的图标。在处理war数据相依性的实施例中,解码/发射单元13收到一条加载指令(即,第二指令),其中加载指令将加载数据写到寄存器r(t),且t大于1且小于n。在发出加载指令之前,解码/发射单元13存取记分板条目1510(t)、记分板条目1520(t)以检查数据相依性。记分板条目1520(t)的读取计数栏位1523显示有一个被安排在8个频率周期时读取寄存器r(t)的先前派发指令(即,第一指令)。记分板条目1510(t)的写入计数栏位1513显示有安排另一个先前派发指令(亦称作第一指令之一),在5个频率周期后写入寄存器r(t)。由于读取时间大于写入时间,因此派发指令是基于记分板条目1520(t)的读取计数栏位1523且忽略记分板条目1510(t)的写入计数栏位1513。这种情况可被称作在加载指令派发时间有确定读取时间的war数据相依性。在实施例中,解码/发射单元13将第二记分板152(在图12a中标为152(派发之前))中的记分板条目1520(t)中的记分板值与加载指令一同派发到deq19e的下一个尚未使用的deq条目(例如190e(0))。

79.参考如图12a中的deq 19e,加载指令将会被放置在(下一个尚未用的)deq条目190e(0),且deq条目190e(0)的栏位将根据加载指令和与加载指令一起配发的记分板值而设置。详细地说,记分板条目1510(t)、记分板条目1520(t)的未定栏位1511、未定栏位1521中的未定值将分别复制到未定加载栏位194和未定存储栏位196。由于加载指令写入寄存器r(t)的时间未定,因此deq条目190e(0)的重点的是确保第一指令在加载指令写入到寄存器r(t)之前已读取寄存器r(t)。因此,派发出加载指令之前的读取计数栏位1523的读取计数值会用来设定deq条目190e(0)的前置计数栏位197。由于deq条目190e(0)是在读取读取计数栏位1523中的读取计数值8之后的一个频率周期设定,因此当将加载指令放置到deq条目190e(0)中时,读取计数值8要减一(即,变成7)。换句话说,deq条目190e(0)中的前置计数值记录第一指令未来还要多少个频率周期才会从寄存器r(t)读取数据。在另一实施例中,前置计数值197可进一步扣除加载指令的最小延迟时间,即,如果加载指令的最小延迟时间为3个周期(而不是1个周期),那么前置计数值197设定为5。基本上,加载指令最早只会在派发时间算起的9个周期后才会写回r(t)。如之前所提到,在将对应于deq条目的加载/存储指令分派到加载/存储单元17之前,deq 19e将必须等到deq条目的未定加载计数、未定存储计数以及前置计数值皆为0。

80.参考图12b,在派发加载指令之后,解码/发射单元13将更新记分板条目1510(t)的未定栏位1511以纪录刚刚派发的指令为一个会回写到寄存器r(t),访问时间未定的加载指令。详细地说,记分板条目1510(t)中的未定栏位1511的未定值将加一(即,变成值“1”)。功能单元栏位1515应改成“加载单元”,以纪录第二指令的操作。

81.图13a到图13b为根据一些实施例用以派发访问时间未定的war数据相依性的加载指令的操作的图标。在实施例中,解码/发射单元13收到一条加载指令(即,第二指令),而此加载指令将加载数据回写到寄存器r(u)。在派发加载指令之前,解码/发射单元13存取记分板条目1510(u)、记分板条目1520(u)以检查数据相依性。基于记分板条目1510(u)的未定栏位1511(“2”),记分板条目1510(u)显示有两个先前加载指令(即,两个第一指令)会写入到寄存器组14的寄存器r(u),亦即待派发的加载指令与两个先前加载指令有waw数据相依性。基于记分板条目1520(u)的未定栏位1521(“1”),记分板条目1520(u)显示存在一个先前存

储指令(即,一个第一指令)会读取寄存器组14的寄存器r(u),亦即待派发的加载指令与先前存储指令有war数据相依性。由于记分板条目1510(u)、记分板条目1520(u)皆记录至少有一个先前指令有未定访问时间,因此写入计数栏位1513、读取计数栏位1523中的值不可用于设定deq条目190e(1)中的前置计数栏位197。在实施例中,解码/发射单元13将加载指令连同第一记分板151及第二记分板152中的记分板条目1510(u)、记分板条目1520(u)中的记分板值一起派发到deq 19e的下一个尚未使用的deq条目(例如,190e(1))。

82.参考图13a中的deq 19e,加载指令将配置到(下一个尚未使用的)deq条目190e(1),且deq条目190e(1)的栏位将根据加载指令和与加载指令一起发送的记分板值而设定。详细地说,将有效栏位改变为“1”以标示该条目使用中,改变执行控制信息栏位193以存储加载指令的控制信息,将地址栏位192改变为“r(u)”以纪录第二加载指令将回写到寄存器r(u)。记分板条目1510(u)的未定栏位1511中的未定值将复制到deq条目190e(1)的未定载入栏位194作为未定载入计数。记分板条目1520(u)的未定栏位1521中的未定值将复制到deq条目190e(1)的未定存储栏位196作为未定存储计数。在实施例中,因为记分板条目1510(u)、记分板条目1520(u)的未定栏位1511、未定栏位1521非零,所以先前加载和存储指令各自有未定访问时间,因此前置计数栏位197要设为0。执行队列19e监视预留的读取总线31对寄存器r(u)的读取操作以与记分板15相同方式递减deq 19e中的未定存储栏位196的未定存储计数。执行队列19e还监视预留的结果总线32对寄存器r(u)的写入操作以与记分板151相同方式递减deq 19e中的未定加载栏位194的未定载入计数。在一些实施例中,加载/存储单元17可将读取信号连同寄存器r(u)发送到deq 19e和记分板152以用于递减未定存储计数和未定读取计数。如之前所提到,在将对应于deq条目的加载/存储指令派发到加载/存储单元17之前,deq 19e将必须等到deq条目的未定加载计数、未定存储计数以及前置计数值递减到0。

83.参考图13b,在派发加载指令之后,解码/发射单元13将更新记分板条目1510(u)的未定栏位1511以纪录最新派发的指令为一条写入寄存器r(u)时间未定的加载指令。详细地说,记分板条目1510(u)中的未定栏位1511的未定值将递增一(即,变成值“3”)。应注意,如果在图13b中的151(派发之后)中的未定值为“3”的情况下解码/发射单元13收到再一个写寄存器r(u)的加载指令,那么解码/发射单元13可暂停派发新接收到的加载指令,这是由于未定栏位1511的未定写入计数等于或大于一个事先设好的未定值(例如,“3”)。

84.图14a到图14c为根据本发明的一些实施例处理向量加载/存储指令的图标。数据执行队列(deq)29e用于处理向量加载/存储指令。记录于deq 29e中的加载/存储指令为有多个加载/存储微操作的向量加载/存储指令。每一个加载/存储微操作被配置成对向量寄存器组的至少一个寄存器做加载或存储操作。参考图14a,deq 29e中有数个deq条目290e(0)到290e(3),用接收到加载/存储指令的次序记录排队中的加载/存储指令的各种信息。应注意,限制deq条目的数目并非此实施例的意图,其它实施例可包含更多或更少的deq条目。每一deq条目对应于一个排队中的加载/存储指令,且包含有效栏位291(“v”)、执行控制信息栏位293(“ctrl/data”)、地址栏位292(“vd”)、未定载入栏位294(“unk ld”)、未定存储栏位296(“unk st”)以及前置计数栏位297(“pre_cnt”),而这些栏位的功能和操作类似于如图7中示的deq19e的栏位。在实施例中,deq 29e还包含微操作栏位(“mop”)298以在每一加载/存储指令中记录多个微操作。deq条目的栏位在从解码/发射单元13收到加载/存储指

令时(即,在解码/发射单元派发指令之后的一个频率周期)设定。图7画的执行队列用于处理有1个微操作的加载/存储指令,而执行图14a到图14c中画的执行队列是用于处理有多个微操作的向量加载/存储指令。deq必须增加栏位以处理向量加载/存储指令的每一微操作的确定和未定的数据相依性。向量加载/存储指令的每一微操作的操作会类似图8到图13b所示的操作和过程,且因出于简洁的目的,此处将省略处理微操作的详细描述。当将对应的加载/存储指令(所有微操作)分派到加载/存储单元17时,该deq条目即可清空(设定为未使用)。

85.参考图14b到图14c,每一deq条目290e(0)到290e(3)配置成用以记录每一微操作的地址信息、未定加载信息以及未定存储信息。举例来说,deq条目290e(0)中的加载/存储指令包含8个微操作,且deq条目290e(1)中的加载/存储指令有4个微操作。参考图14b,地址栏位292(0)、未定加载栏位294(0)和未定栏位296(0)扩展成有8组数据以处理deq条目290e(0)中的8个微操作。参考图14c,地址栏位292(1)、未定加载栏位294(1)和未定栏位296(1)扩展成有4组数据以处理deq条目290e(1)中的4个微操作。

86.类似于图7中的deq 19e,地址栏位292记录由向量加载/存储指令存取的向量寄存器组(未示出)中的向量寄存器的寄存器地址。向量寄存器比寄存器组14的纯量寄存器宽得多。举例来说,纯量寄存器对于64位的单一元素为64位,而向量寄存器为512位,可表示(举例)8个64位的元素或64个8位的元素。微操作的数目指的是连续的向量寄存器的数目。举例来说,deq条目290e(0)中的向量加载/存储指令的地址栏位292中的寄存器值“v24”表示图14b所示的8个微操作会存取寄存器地址v24到寄存器地址v31。deq条目290e(1)中的加载/存储指令的地址栏位292中的寄存器值“v20”表示图14c所示的4个微操作会存取寄存器地址v20到寄存器地址v23。deq 29e基于地址栏位292中所指定的第一向量寄存器v24及第一向量寄存器v20以及“mop”栏位298中的微操作的数目而算出其它有效向量寄存器。

87.在一些实施例中,将每个微操作视为独立指令。参考图14b和图14c,每一微操作有地址栏位292(0)、地址栏位292(1)、未定加载栏位294(0)、未定载入栏位294(1)、未定存储栏位296(0)、未定存储栏位296(1)以及前置计数栏位297(0)、前置计数栏位297(1)。条目290e(0)和条目290e(1)中的每一微操作的计数栏位297(0)、计数栏位297(1)配置成记录在向量加载/存储指令的微操作会存取的寄存器当中(确定的raw、waw或war数据相依性)的最大计数值(例如,先前第一指令的写入或读取时间)。举例来说,条目290e(0)的计数栏位297(0)可记录8个计数值,所述计数值对应于记录在deq条目290e(0)中的加载/存储向量指令的8个加载/存储微操作。记录在计数栏位297(0)中的计数值沿每个频率周期向下计数直到计数值达到0为止。加载/存储队列29e可基于对应于载入/存储微操作的计数值将加载/存储向量指令的加载/存储微操作个别分派到加载/存储单元17。应注意,用于每一微操作的未定栏位294(0)和未定栏位296(0)也必须为零才能将个别微操作分派到负载/存储单元17。

88.在一个替代实施例中,条目290e(0)中的加载/存储指令的8个计数栏位297(0)可合并起来只记录单个最大确定前置计数值。也就是说,同一条目(例如,290e(0))中的所有微操作共享一个前置计数栏位297,所述栏位记录所有微操作的最大确定数据相依性。计数值针对每一频率周期向下减一,直到计数值达到0为止。加载/存储向量指令的所有加载/存储微操作可在计数值达到0时分派到加载/存储单元17执行。应注意,未定栏位294(0)和未

定栏位296(0)也必须为零才能将所有微操作分派到负载/存储单元17。

89.在一些实施例中,记录于加载/存储队列29e中的加载/存储指令为加载/存储向量指令,有数个存取特定寄存器的多个加载/存储微操作,且特定寄存器上的数据相依性(例如,waw、war、raw数据相依性)为未定数据相依性。换句话说,用于解开数据相依性的时序是未定的。在deq 29e中,对每一deq条目中的微操作的每一寄存器,必须监视专用写入端口(结果总线32的一部分)以检测回写到向量寄存器组的特定向量寄存器,然后以与记分板151相同的方式递减未定加载栏位294。同理,每一deq条目中的每一微操作寄存器必须监视预留读取总线31以检测对向量寄存器组的特定向量寄存器的读取,然后以与记分板152相同的方式递减未定存储栏位296。在一些实施例中,加载/存储单元17可将回写信号连同写入寄存器以及读取信号连同读取寄存器发送到deq 29e、第一记分板151以及第二记分板152以递减deq条目中的未定计数。举例来说,图14b中的第一条目190e(0)对8个向量寄存器(即,v24到v31)有8个监视器在结果总线32的专用写入端口上检测回写到向量寄存器组的特定向量寄存器,并且在检测到匹配时递减未定加载栏位294(0)中的值。同时,图14b中的第一条目290e(0)对8个向量寄存器(即,v24到v31)有8个监视器在结果总线32的专用读取端口上检测对向量寄存器组的特定向量寄存器的读取,并且在检测到匹配时递减未定存储栏位296(0)中的值。如之前所提到,对应于加载/存储单元17的加载/存储微操作在分派之前,deq 29e(0)中的每一微操作必须等到deq条目290e(0)的未定载入计数294(0)、未定存储计数296(0)以及前置计数值297(0)递减到0。有4个有效条目的deq 29e可以在结果总线32的专用写入端口上有至多32个监视器且在来自向量寄存器组的预留读取总线31上有至多32个监视器。在一些实施例中,微操作会按照顺序分派到加载/存储单元17。当对应的第一未定加载栏位294(0)、第一未定存储栏位296(0)以及前置计数栏位297(0)为零时,图14b中的deq 29e的第一条目290e(0)派发加载向量寄存器v24的第一微操作。当派发第一微操作时,mop栏位298递减1。当对应的第二未定加载栏位294(0)、第二未定存储栏位296(0)以及前置计数栏位297(0)为零时,派发加载向量寄存器v25的第二微操作。当派发第二微操作时,mop栏位298递减1。当mop栏位递减到零时,来自第一条目290e(0)的所有8个微操作已全部分派到加载/存储单元17所以第一条目可以注销,然后当对应的未定加载栏位294(1)、未定加载栏位296(1)以及前置计数栏位297(1)为零时,可派发图14c中第二条目290e(1)的微操作。

90.根据以上实施例,微处理器的记分板可包含未定栏位和计数栏位,其中未定栏位用于记录写入和读取时间未定的指令,而计数栏位用于纪录写入和读取时间确定的指令。对写入和读取时间确定的先前指令有数据相依性(例如,waw、war、raw数据相依性)的加载/存储指令被称作有确定数据相依性。对写入和读取时间未定的先前指令有数据相依性(例如,waw、war、raw数据相依性)的加载/存储指令被称作有未定数据相依性。具有这两种类型数据相依性的加载/存储指令皆可立即派发到加载/存储队列而不是暂停在解码/发射单元中。通过此方式,微处理器的效能可以得到改进。另外,加载/存储指令可为纯量加载/存储指令或者是包含多个载入/存储微操作的加载/存储向量指令。

91.前文已概述了若干实施例的特征以使得本领域的技术人员可更好地理解以下详细描述。本领域的技术人员应可理解到,他们可以容易地使用本发明作为设计或修改其他工艺和结构的基础,以实现与本文介绍的实施例相同的目的和/或实现相同的优点。本领域

技术人员也应该认识到,这样的等效构造并不脱离本发明的精神和范围,在不脱离本发明的精神和范围的情况下,可以在本文中进行各种变化、替换和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1