一种数据处理设备的制作方法

1.本发明涉及芯片领域,特别是涉及一种数据处理设备。

背景技术:

2.大数据时代,存在各种的数据处理设备(例如plc(programmable logic controller,可编程逻辑控制器)等),目前很多的数据处理设备对于输入接口以及输出接口存在大量需求,但是数据处理设备中(用于对数据进行逻辑处理)的逻辑处理芯片本身能够提供的输入接口以及输出接口的数量是有限的,如何低成本且小空间的扩展数据处理设备的输入输出接口io数量是亟待解决的技术问题。

3.因此,如何提供一种解决上述技术问题的方案是本领域技术人员目前需要解决的问题。

技术实现要素:

4.本发明的目的是提供一种数据处理设备,由于并转串芯片以及串转并芯片本身具有体积小成本低的特点,因此本技术在扩展了数据处理设备的io数量的同时,节省了成本,控制了数据处理设备的体积。

5.为解决上述技术问题,本发明提供了一种数据处理设备,包括:

6.主控装置,用于将待处理数据发送至逻辑处理芯片;

7.与所述主控装置连接的所述逻辑处理芯片,用于提供多个输入接口以及多个输出接口,对所述待处理数据进行指定的逻辑处理后将其发送至指定的输出接口,将从输入接口接收到的数据进行指定的逻辑处理后将其发送至指定的所述主控装置或所述输出接口;

8.相互串接且一端与所述逻辑处理芯片的第一串口连接的多个并转串芯片,用于将从自身提供的多个输入接口输入的并行数据转换为串行数据后发送至所述逻辑处理芯片;

9.相互串接且一端与所述逻辑处理芯片的第二串口连接的多个串转并芯片,用于将所述逻辑处理芯片发送的串行数据转换为并行数据后,通过自身提供的多个输出接口输出。

10.优选地,该数据处理设备还包括:

11.与距离所述逻辑处理芯片最近的所述并转串芯片提供的所述输入接口连接的电平设定电路,用于将连接的各个所述输入接口的电平组合设定为预设组合,以便通过所述预设组合确定所述并转串芯片提供的输入接口的总数以及所述串转并芯片提供的输出接口的总数。

12.优选地,所述电平设定电路包括电平上拉电路以及电平下拉电路。

13.优选地,所述主控装置为arm处理器。

14.优选地,所述逻辑处理芯片为现场可编程逻辑门阵列fpga或复杂可编程逻辑器件cpld。

15.优选地,所述第一串口以及所述第二串口为同种类型。

16.优选地,所述第一串口以及所述第二串口均为串行外设接口spi接口。

17.优选地,该数据处理设备为可编程逻辑控制器plc。

18.本发明提供了一种数据处理设备,为了节省逻辑处理芯片上的引脚数量,本技术中可以通过逻辑处理芯片的第一串口连接多个并转串芯片,通过第二串口连接多个串转并芯片,如此一来,由并转串芯片提供的多个输入接口的输入数据便可以均经由第一串口输入逻辑处理芯片,逻辑处理芯片通过第二串口也可以输出大量的数据至指定的输出接口,由于并转串芯片以及串转并芯片本身具有体积小成本低的特点,因此本技术在扩展了数据处理设备的io数量的同时,节省了成本,控制了数据处理设备的体积。

附图说明

19.为了更清楚地说明本发明实施例中的技术方案,下面将对现有技术和实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

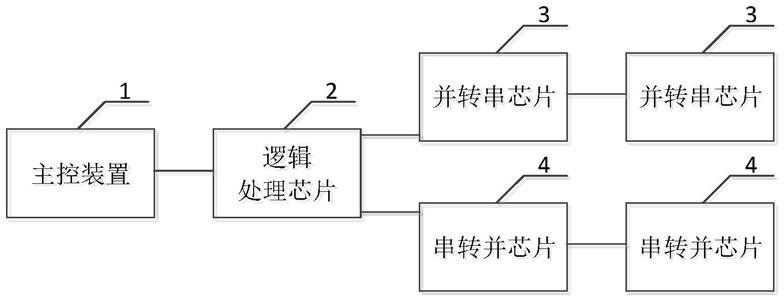

20.图1为本发明提供的一种数据处理设备的结构示意图;

21.图2为本发明提供的另一种数据处理设备的结构示意图;

22.图3为本发明提供的一种并转串芯片的接线示意图;

23.图4为本发明提供的一种串转并芯片的接线示意图。

具体实施方式

24.本发明的核心是提供一种数据处理设备,由于并转串芯片以及串转并芯片本身具有体积小成本低的特点,因此本技术在扩展了数据处理设备的io数量的同时,节省了成本,控制了数据处理设备的体积。

25.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

26.请参考图1,图1为本发明提供的一种数据处理设备的结构示意图,该数据处理设备包括:

27.主控装置1,用于将待处理数据发送至逻辑处理芯片2;

28.与主控装置1连接的逻辑处理芯片2,用于提供多个输入接口以及多个输出接口,对待处理数据进行指定的逻辑处理后将其发送至指定的输出接口,将从输入接口接收到的数据进行指定的逻辑处理后将其发送至指定的主控装置1或输出接口;

29.相互串接且一端与逻辑处理芯片2的第一串口连接的多个并转串芯片3,用于将从自身提供的多个输入接口输入的并行数据转换为串行数据后发送至逻辑处理芯片2;

30.相互串接且一端与逻辑处理芯片2的第二串口连接的多个串转并芯片4,用于将逻辑处理芯片2发送的串行数据转换为并行数据后,通过自身提供的多个输出接口输出。

31.具体的,考虑到如上背景技术中的技术问题,又结合考虑到逻辑处理芯片2上的引脚数量有限,因此本技术选择利用串口外接并转串芯片3以及串转并芯片4,如此并不会占

用逻辑处理芯片2太多的引脚,便可以完成io接口的大量扩展,其中,并转串芯片3提供的多个输入接口的数据为并行数据,也即每一个输入接口的数据都是独立的,因此相当于扩充了数据处理设备的输入接口,而对于串转并芯片4来说,其可以接收逻辑处理芯片2输出的串行数据并将其转换为并行数据并通过自身提供的多个输出接口输出,每个输出接口的数据都是独立的,相当于扩充了数据处理设备的输出接口。

32.具体的,并转串芯片3以及串转并芯片4的数量均可以进行自主设定,例如均设置了8个等,本发明实施例在此不做限定。

33.其中,值得一提的是,逻辑处理芯片2提供的io接口可以为高速io接口,而并转串芯片3以及串转并芯片4提供的io接口可以为低速io接口,如此便能够满足大多数接口需求且稳定性较强。

34.本发明提供了一种数据处理设备,为了节省逻辑处理芯片上的引脚数量,本技术中可以通过逻辑处理芯片的第一串口连接多个并转串芯片,通过第二串口连接多个串转并芯片,如此一来,由并转串芯片提供的多个输入接口的输入数据便可以均经由第一串口输入逻辑处理芯片,逻辑处理芯片通过第二串口也可以输出大量的数据至指定的输出接口,由于并转串芯片以及串转并芯片本身具有体积小成本低的特点,因此本技术在扩展了数据处理设备的io数量的同时,节省了成本,控制了数据处理设备的体积。

35.为了更好地对本发明实施例进行说明,请参考图2至图4,图2为本发明提供的另一种数据处理设备的结构示意图;图3为本发明提供的一种并转串芯片3的接线示意图;图4为本发明提供的一种串转并芯片4的接线示意图,在上述实施例的基础上:

36.作为一种优选的实施例,该数据处理设备还包括:

37.与距离逻辑处理芯片2最近的并转串芯片3提供的输入接口连接的电平设定电路5,用于将连接的各个输入接口的电平组合设定为预设组合,以便通过预设组合确定并转串芯片3提供的输入接口的总数以及串转并芯片4提供的输出接口的总数。

38.具体的,为了便于不同的数据处理设备知晓自身通过串转并芯片4以及并转串芯片3扩充的io接口的数量,本发明实施例中还可以通过电平设定电路5设定距离逻辑处理芯片2最近的并转串芯片3提供的输入接口的电平组合为预设组合,如此一来,逻辑处理芯片2通过接收到的串行数据的前几位的预设组合,便可以确定出并转串芯片3提供的输入接口的总数以及串转并芯片4提供的输出接口的总数。

39.其中,在图3中,各个引脚的定义如下:

40.clk:时钟输入;clk inh:数据输出使能;sh/ld:数据加载位;ser:串行输入;a~h:并行输入:qh:串行输出;’qh:串行输出反向。

41.其中,在图4中,各个引脚的定义如下:

42.srclk:时钟输入;rclk:数据锁存时钟;oe:输出使能;srclr:复位脚;ser:串行输入;qa~qh:并行输出:qh:串行输出;’qh:串行输出反向。

43.作为一种优选的实施例,电平设定电路5包括电平上拉电路以及电平下拉电路。

44.具体的,电平上拉电路以及电平下拉电路具有体积小、结构简单以及成本低等优点。

45.当然,除了电平上拉电路以及电平下拉电路的形式外,电平设定电路5还可以为其他多种类型,本发明实施例在此不做限定。

46.作为一种优选的实施例,主控装置1为arm处理器。

47.具体的,arm处理器具有处理能力强、体积小以及成本低等优点。

48.当然,除了arm处理器外,主控装置1还可以为其他多种类型,本发明实施例在此不做限定。

49.作为一种优选的实施例,逻辑处理芯片2为fpga(field programmable gate array,现场可编程逻辑门阵列)或cpld(complex programmable logic device,复杂可编程逻辑器件)。

50.具体的,fpga以及cpld均具有处理能力强、体积小以及成本低等优点。

51.当然,除了fpga以及cpld外,逻辑处理芯片2还可以为其他类型,本发明实施例在此不做限定。

52.作为一种优选的实施例,第一串口以及第二串口为同种类型。

53.具体的,将第一串口以及第二串口设定为同种类型可以提高工作效率。

54.当然,第一串口以及第二串口可以被设定为不同的类型,本发明实施例在此不做限定。

55.作为一种优选的实施例,第一串口以及第二串口均为spi(serial peripheral interface,串行外设接口)接口。

56.具体的,spi接口具有传输速度快以及稳定性强等优点。

57.当然,除了spi接口外,第一串口以及第二串口还可以为其他类型,例如i2c接口等,本发明实施例在此不做限定。

58.作为一种优选的实施例,该数据处理设备为可编程逻辑控制器plc。

59.具体的,plc具有数据处理能力强以及寿命长等优点。

60.当然,除了plc外,数据处理设备还可以为其他类型,本发明实施例在此不做限定。

61.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。还需要说明的是,在本说明书中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者设备中还存在另外的相同要素。

62.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其他实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1