一种可编程归一化协处理器数据处理系统及方法与流程

1.本发明涉及数据处理领域,特别是一种可编程归一化协处理器数据处理方法。适用于新一代微型静态红外地球敏感器的研制。

背景技术:

2.红外地球敏感器作为空间飞行器的一个重要姿态测量产品,被广泛应用于飞行器控制分系统中。通过测量本体与地球相对位置,经过数据融合与姿态解算,得到本体相对地球俯仰和滚动方向姿态信息。

3.在新一代微型静态红外地球敏感器的研制过程中,采用全数字设计方案,同时满足小型化、低成本研制要求。需要完成图像数据排序,图像去噪,图像补偿算法,图像非均匀校正,图像坏点去除,地球图像处理,地心矢量计算等功能。

4.在研制过程中,产品的cpu选用80c32,内核为8bit mcu,主频22mhz,性能无法满足以上复杂图像数据处理与解算。通过mcu+fpga(以a54sx72a为例)方案完成上述功能,面临如下技术问题:

5.(1)源图像数据使用mcu软件进行排序和计算,受处理速度和存储空间限制,迟滞严重,无法匹配满足图像数据刷新率与姿态结算周期要求,必须进行硬件加速。

6.(2)通过fpga进行硬件加速,传统硬件加速方法功能固定,在研发过程中,面临算法方案更动,数据排序和数据处理优化调整时,需要不断重新设计,增加研发难度,拉长研发周期。

7.(3)完成上述图像数据的全流程处理功能,选取的fpga芯片内部逻辑资源紧张,无法全部实现。选型高性能级别的cpu+fpga方案,整机产品成本极大上升,无法适应未来面向商业航天应用。

技术实现要素:

8.本发明解决的技术问题是:克服现有技术的不足,针对以上问题进行了分析、提取和归纳,提出了一种可编程归一化协处理器数据处理系统及方法。

9.本发明的技术解决方案是:一种可编程归一化协处理器数据处理系统,数据排序归一化协处理器、数据算法归一化协处理器;目标序列数据存储器、高可靠存储器;

10.所述高可靠存储器按照预先设置的存储规则,设计针对源序列数据的地址跳转指令以及数据处理算法指令;

11.所述数据排序归一化协处理器,通过解析高可靠存储器输入的地址跳转指令,完成原始序列到目标序列排序,并将排序后的目标序列存储至目标序列数据存储器;所述的原始序列为传感器输出的源序列数据;

12.所述数据算法归一化协处理器,从目标序列数据存储器中读取目标序列数据,根据高可靠存储器输入的数据处理算法指令对读取的目标序列数据进行运算,完成全部目标序列数据的处理。

13.优选的,所述的数据排序归一化协处理器包括数据接收处理子模块、地址跳转指令解析子模块、数据可编程重排子模块;

14.所述的数据接收处理子模块接收传感器输出的源序列数据,从源序列数据的起始tick信号和结束tick信号之间接收有效标志tick信号,并将有效标志tick信号对应的数据锁存,记为data_m_n;

15.所述地址跳转指令解析子模块通过地址寻址,读取地址跳转指令,进行译码解析,得到数据data_m_n在重新排序后新的目的地址x;

16.所述数据可编程重排子模块将锁存信号data_m_n存入目标序列数据存储器的目的地址x。

17.优选的,将数据接收处理子模块、地址跳转指令解析子模块、数据可编程重排子模块进行例化集成,通过状态机设计完成三个子模块逻辑控制部分;一次源序列数据的接收到数据重排后存储,作为一个闭环控制流程i;状态机设计根据源序列数据与目标序列数据容量,对闭环控制流程i进行循环控制,完成全部源序列数据的排序。

18.优选的,所述的地址跳转指令为自定义指令,按照预设的地址跳转顺序,为每个源序列数据按上述顺序分配对应的地址。

19.优选的,所述数据算法归一化协处理器包括源数据获取处理子模块、解算指令解析子模块、基本运算单元子模块;

20.所述源数据获取处理子模块从目标序列数据存储器中读取目标序列数据并进行数据有效性判断,获取有效的待处理数据;

21.所述解算指令解析子模块对数据处理算法指令进行译码解析,将图像数据处理过程中的算法分解为基本运算流程;

22.基本运算单元子模块针对有效的待处理数据按照基本运算流程进行运算,得到图像数据处理结果。

23.优选的,所述的基本运算单元子模块中包含但不限于数据定点转浮点转换模块、数据定点四则运算模块、数据浮点四则运算模块、数据浮点转定点运算模块、运算结果拟合模块,根据不同的算法流程要求在基本运算流程过程中调用对应的模块,以使算法流程能够依次顺利执行。

24.优选的,若有并行处理要求,则设计多个基本运算单元子模块并行完成运算。

25.优选的,针对设计所需的全部图像数据处理过程,编写数据处理算法指令集合,并下载到高可靠存储器中;

26.根据设计所需的源序列数据到目标序列数据需求,编写重排地址跳转指令集合内容,下载到高可靠存储器中。

27.优选的,数据排序归一化协处理器、数据算法归一化协处理器;目标序列数据存储器运行在fpga或asic中。

28.一种可编程归一化协处理器数据处理方法,在fpga或asic中运行如下步骤:

29.接收原始序列即传感器输出的源序列数据,从源序列数据的起始tick信号和结束tick信号之间接收有效标志tick信号,并将有效标志tick信号对应的数据锁存,记为data_m_n;

30.通过地址寻址,读取地址跳转指令,进行译码解析,得到数据data_m_n在重新排序

后新的目的地址x;

31.将锁存信号data_m_n存入目标序列数据存储器的目的地址x;完成原始序列到目标序列排序;

32.从目标序列数据存储器中读取目标序列数据并进行数据有效性判断,获取有效的待处理数据;

33.接收数据处理算法指令并对数据处理算法指令进行译码解析,将图像数据处理过程中的算法分解为基本运算流程;

34.针对有效的待处理数据按照基本运算流程进行运算,得到图像数据处理结果。

35.本发明与现有技术相比的优点在于:

36.(1)归一化协处理器数据处理方法,逻辑资源占用为传统数据处理方法的1/3,并且随着复杂度的提升可进一步降低。

37.(2)可编程数据处理方法,解决了传统数据处理模式功能锁定,调整处理算法需更改设计的问题,极大精简研发过程中的回归迭代。

38.(3)定制化的精简指令集,可裁剪的协处理器架构,并行、流水处理,综合效果较传统数据处理方式速度可提升一个数量级。

39.(4)数据与指令深度融合,指令校验,较传统处理方法能够提高系统运行鲁棒性。

40.(5)将不同数据排序、数据算法特征提取,提出了一种可编程归一化协处理器数据处理方法,通过外部存储器指令编程,实现灵活可变的数据处理模式。

41.(6)设计了精简的自定义数据处理指令集,包含地址跳转类指令,数据算法类指令,指令集可根据设计需求进行定制化裁剪,将us级的软件指令组合降低到fpga系统主频ns级实现。

42.(7)设计的数据处理方法实现时可硬件裁剪,并行计算,流水处理。完成多数据源并行处理,完成数据排序、去噪、校正、坏点剔除流水处理,处理效率成倍提升。

附图说明

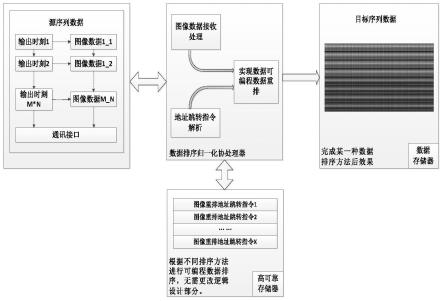

43.图1为本发明的基于可编程归一化协处理器的数据排序框图;

44.图2为非可编程归一化排序方法与可编程归一化排序方法效果对比图;

45.图3为本发明的基于可编程归一化协处理器的数据处理框图;

46.图4为cpu软件计算方式、非可编程归一化硬件加速计算方式和可编程归一化计算方式效果对比图;

具体实施方式

47.本发明包含数据排序和数据计算两部分。

48.(一)数据排序

49.数据排序完成了传感器输出原始数据排序功能,本发明方法根据源序列数据,通过设置指令,生成需要的目标序列数据,能够适应不同类型数据传感器,结合附图对本发明方法进行详细说明,如图1、图2所示本发明方法包括如下步骤:

50.步骤1,根据使用数据传感器型号,根据数据传感器使用的工作模式,得到传感器在不同时刻输出的源序列数据格式。

51.步骤2,设计相应数据传感器的通讯接口,将传感器输出的源序列数据接收,输出到数据排序归一化协处理器。该步骤起到数据管道通路作用,不对数据进行处理。

52.步骤3,设计数据排序归一化协处理器,该模块由数据接收处理、地址跳转指令解析、实现数据可编程重排三个子模块实现。包含各个子模块设计与模块整体集成设计。

53.步骤a,实现图像数据接收处理子模块设计:

54.接收由步骤2输出的源序列数据,从源序列数据的起始tick信号和结束tick信号之间接收有效标志tick信号,并将有效标志tick信号对应的数据锁存,记为data_m_n。〃

55.步骤b,实现地址跳转指令解析子模块设计:

56.通过地址寻址,读取高可靠存储器内数据重排地址跳转指令。进行译码解析,得到步骤a中读取的数据,在重新排序后新的目的地址x。

57.步骤c,实现数据可编程重排子模块设计:

58.将步骤a,步骤b得到的数据data_m_n存入数据存储器的目的地址x。数据存储器可以是易失存储器(如:sram)或者非易失存储器(如:flash)。排序后的目标序列数据可以给数据处理模块或者数据下传模块使用。

59.步骤d,实现上述三个子模块集成:

60.将步骤a,步骤b,步骤c,设计完成的子模块进行例化集成,通过状态机设计完成三个子模块逻辑控制部分。一次源序列数据的接收到数据重排后存储,作为一个闭环控制流程i。状态机设计根据源序列数据与目标序列数据容量,对闭环控制流程i进行循环控制,完成全部数据的排序。

61.本发明在数据排序过程中需要设计一类自定义的地址跳转指令。例如:在步骤3子步骤a中,如果源序列数据存储到目标序列数据的地址a时,下一个源序列数据存储到目标地址b。然后步骤3子步骤b,会读取下一条地址跳转指令在步骤3子步骤a中,如果源序列数据存储到目标序列数据的地址c时,下一个源序列数据存储到目标地址d,依次类推,完成全部数据排序。

62.根据设计所需的源序列数据到目标序列数据需求,编写重排地址跳转指令集合内容,下载到高可靠存储器中,以适应空间抗辐照高可靠应用。

63.当研制过程中,方案更改,数据排序面临优化调整时,只需要对外部高可靠存储器中地址跳转指令编程,即可实现灵活的排序方法,无需更改fpga设计,降低研发难度与研发周期。

64.地址跳转指令具有可扩展性,根据实际设计需求,可以设计但不限于以下的指令,如:地址剔除指令、地址暂停指令、地址偏移指令、地址镜像指令、地址数据截位指令等。可以根据实际的设计需求,进行精简化裁剪与扩充。

65.(二)数据计算

66.数据计算完成了图像去噪,图像补偿算法,图像非均匀校正,图像坏点去除等数据处理功能。能够适应不同数据处理算法,结合附图对本发明方法进行详细说明,如图3、图4所示本发明方法包括如下步骤:

67.步骤1,首先,将数据排序后数据存储器(即目标序列数据存储器)中的图像数据读

出,通过读存储器时序接口完成。

68.步骤2,根据设计需要的图像数据处理过程(在本例背景微型静态红外地球敏感器的设计过程中,包含图像去噪,图像补偿算法,图像非均匀校正,图像坏点去除),分解算法处理步骤,将算法流程分解为基本运算流程。

69.步骤3,设计数据算法归一化协处理器模块,该模块由源数据获取处理、解算指令解析、基本运算单元三个子模块实现。包含各个子模块设计与模块整体集成设计。

70.步骤a,实现图像源数据获取处理子模块设计:

71.接收由步骤1输出的源数据,根据地址寻址,读取需要进行处理数据,对数据进行有效性判断(例如阈值门限判断),开始进行数据处理。如为:data_m_n。

72.步骤b,实现解算指令解析子模块设计:

73.通过地址寻址,读取高可靠存储器内数据处理算法指令,进行译码解析。针对步骤a中得到的数据,由数据处理分解出来的基本运算步骤,进行运算。包含不限于明确基本运算的操作数、运算类型、结果小数部分处理,运算结果存储。

74.步骤c,实现基本运算单元子模块设计:

75.基本运算单元子模块,包含不限于数据定点转浮点转换模块、数据定点四则运算模块、数据浮点四则运算模块、数据浮点转定点运算模块、运算结果拟合模块组成。基本运算单元子模块完成数据处理分解出来的基本运算步骤中的全部运算。如果有并行处理的需求,可以设计例化多个基本运算模块,完成并且高速运算。

76.步骤d,实现上述三个子模块集成:

77.将步骤a,步骤b,步骤c,设计完成的子模块进行例化集成,通过状态机设计完成三个子模块逻辑控制部分。一次源序列数据的读取到数据处理基本运算完成,作为一个闭环控制流程i。状态机设计根据图像数据处理过程,对闭环控制流程i进行循环控制,完成全部数据处理工作。

78.本发明数据处理过程中需设计一类自定义的数据处理算法指令。例如:在步骤3子步骤b中,对该指令进行解析,得到步骤3子步骤c中需要进行的基本运算,以及结果处理。在完成步骤3子步骤d中一个闭环控制流程i,会读取下一条数据处理算法指令,依次类推,完成全部数据处理,得到目标算法结果,如姿态信息。

79.根据设计所需的全部图像数据处理过程,编写数据处理算法指令集合内容,下载到高可靠存储器中,以适应空间抗辐照高可靠应用。

80.当研制过程中,方案更改,数据处理算法面临优化调整时,只需要对步骤5中外部高可靠存储器中地址跳转指令编程,即可实现灵活的排序方法,无需更改fpga设计。

81.数据处理算法具有可扩展性,根据实际设计需求,可以设计但不限于以下的指令,如:计算循环指令、计算仲裁指令、计算跳转指令、计算拟合指令等。可以根据实际的设计需求,进行精简化裁剪与扩充。

82.本发明在actel公司的a54sx72a fpga芯片上实现,图像处理时间由数秒减少到百毫秒级;fpga内部逻辑资源占用由300%减少到80%,极大降低资源消耗;通过可编程归一化特性,可适应不同数据排序、计算要求。适用于复杂数据处理,通过一种通用架构实现,具

有高效、灵活和普适特点。本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1