用于FPGA的可编程晶振实时配置及监控方法与流程

用于fpga的可编程晶振实时配置及监控方法

技术领域

1.本发明涉及fpga时钟电路设计,具体涉及一种用于fpga的可编程晶振实时配置及监控方法。

背景技术:

2.fpga(field-programmable gate array,现场可编程门阵列)内部逻辑电路的正常运行几乎都离不开稳定、可靠的时钟,而不同的设计需求往往需要fpga搭配不同频率的晶振。为了使硬件平台具有更好的适应性,fpga往往会搭配可编程晶振。可编程晶振,顾名思义就是可通过编程方式控制晶振在一定频率范围内输出任意频率的时钟,以便适应不同的设计需求。

3.但在fpga使用可编程晶振作为时钟源时会遇到以下技术问题:

4.为了使可编程晶振输出指定频率的时钟,就需要对其进行配置,而用于配置可编程晶振的fpga相关逻辑也是需要时钟驱动才能正常工作,该时钟是无法由可编程晶振自身提供。通常的解决方案是,增加一片晶振为配置可编程晶振的fpga相关逻辑提供时钟。但额外增加的这片晶振一般只在配置可编程晶振时才会发挥作用,一旦可编程晶振配置完成,该晶振的工作就结束了。这样不仅造成了硬件资源的浪费,也不利于产品集成度的提高。

技术实现要素:

5.本发明的目的在于提供一种用于fpga的可编程晶振实时配置及监控方法,使fpga不需要额外的晶振为配置可编程晶振的逻辑提供时钟,fpga外部仅搭配一片可编程晶振就可以正常工作,从而节省了硬件资源,并提高了产品集成度。

6.为了达到上述的目的,本发明提供一种用于fpga的可编程晶振实时配置及监控方法,利用fpga内部cfgmclk信号和eos信号,以cfgmclk信号作为工作时钟,以eos信号作为复位信号,为配置可编程晶振的逻辑提供时钟及复位。

7.上述用于fpga的可编程晶振实时配置及监控方法,其中,fpga内部设置startup原语功能模块和时钟配置及监控功能模块,cfgmclk信号和eos信号均由startup原语功能模块提供,当时钟配置及监控功能模块接收到cfgmclk信号和eos信号后,对可编程晶振进行配置。

8.上述用于fpga的可编程晶振实时配置及监控方法,其中,时钟配置及监控功能模块接口按照默认频率或者用户逻辑指定的频率对可编程晶振进行配置。

9.与现有技术相比,本发明的有益技术效果是:

10.本发明的用于fpga的可编程晶振实时配置及监控方法,利用了fpga内部startup原语功能模块提供的时钟来驱动可编程晶振的配置及监控,因此无需外部独立晶振就可完成可编程晶振的实时配置及时钟监控,与现有技术相比,可以省掉用于为配置可编程晶振的fpga相关逻辑提供时钟的外部晶振。经过实际测试,本发明的用于fpga的可编程晶振实时配置及监控方法能够降低硬件成本,提升产品集成度。

附图说明

11.本发明的用于fpga的可编程晶振实时配置及监控方法由以下的实施例及附图给出。

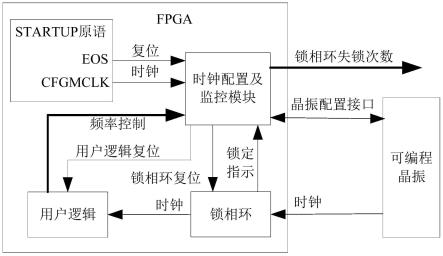

12.图1为本发明较佳实施例中用于fpga的可编程晶振实时配置及监控方法的原理框图。

13.图2为本发明较佳实施例中时钟配置及监控模块接口示意图。

14.图3为本发明较佳实施例中时钟配置及监控功能模块工作流程图。

具体实施方式

15.以下将结合图1~图3对本发明的用于fpga的可编程晶振实时配置及监控方法作进一步的详细描述。

16.本发明的用于fpga的可编程晶振实时配置及监控方法,利用fpga内部两种特殊信号:cfgmclk(configuration master clock)信号和eos(end of startup)信号,以cfgmclk信号作为工作时钟,以eos信号作为复位信号,为配置可编程晶振的逻辑提供时钟及复位。cfgmclk信号和eos信号均由fpga内部startup原语功能模块提供。

17.本发明的用于fpga的可编程晶振实时配置及监控方法,利用fpga内部已有的时钟信号和复位信号为配置可编程晶振的逻辑提供时钟,即可省去为配置可编程晶振的逻辑提供时钟的晶振,使得fpga仅需一片可编程晶振就能正常工作,从而降低硬件成本,提升产品集成度。

18.图1所示为本发明较佳实施例中用于fpga的可编程晶振实时配置及监控方法的原理框图;图2所示为本发明较佳实施例中时钟配置及监控模块接口示意图。

19.参见图1,本实施例的fpga包括startup原语功能模块、时钟配置及监控功能模块、时钟锁相环和用户逻辑功能模块。

20.所述startup原语功能模块提供cfgmclk信号和eos信号;cfgmclk信号为时钟信号,该时钟信号在fpga加电后会一直工作,除了为fpga配置阶段提供配置时钟外,也可以作为fpga其他逻辑电路的驱动时钟;eos信号是fpga配置完成指示信号,在fpga加电后至fpga配置完成前处于无效状态,而在fpga配置完成后处于有效状态,可以作为fpga逻辑电路的复位信号。所述startup原语功能模块是fpga的基本功能模块。

21.所述时钟配置及监控功能模块与所述startup原语功能模块、所述用户逻辑功能模块和所述时钟锁相环均相连。所述startup原语功能模块提供的cfgmclk信号和eos信号输出至所述时钟配置及监控功能模块,为可编程晶振实时配置及监控的相关逻辑提供时钟驱动;所述时钟配置及监控功能模块主要功能包括:配置及监控可编程晶振;为用户逻辑功能模块及时钟锁相环提供复位信号;接收用户逻辑功能模块的频率控制字以及失锁指示。

22.所述用户逻辑功能模块实现产品功能的fpga逻辑。

23.所述时钟锁相环是fpga的基本功能模块。

24.可编程晶振提供spi接口或iic接口,fpga通过晶振配置接口与可编程晶振的spi接口或iic接口连接;可编程晶振为fpga提供可编程的工作时钟,该工作时钟为fpga逻辑(即用户逻辑)提供时钟驱动;同时,fpga通过spi接口或iic接口对可编程晶振进行编程(即对可编程晶振进行配置)。

25.参见图2,所述时钟配置及监控功能模块包括晶振配置接口、时钟锁相环复位接口、用户逻辑复位接口、时钟锁相环失锁次数接口、时钟锁相环锁定指示接口、频率控制字接口和频率控制字锁存接口;

26.所述时钟配置及监控功能模块接收到所述startup原语功能模块提供的cfgmclk信号和eos信号后,通过其晶振配置接口对可编程晶振进行配置并访问可编程晶振内部寄存器以判断可编程晶振状态;所述时钟锁相环复位接口用于对fpga内部的时钟锁相环进行复位;所述用户逻辑复位接口用于对fpga内部的用户逻辑功能模块进行复位;所述时钟锁相环锁定指示接口用于接收时钟锁相环的锁定信号;所述频率控制字接口和所述频率控制字锁存接口用于接收用户逻辑功能模块发送的频率控制字信号,所述频率控制字锁存接口通过频率控制字信号的上升沿或下降沿判断频率控制字信号的有效性,当时钟配置及监控功能模块接收到新的频率控制字信号时,会按照新的频率控制字对可编程晶振进行重新配置;所述时钟锁相环失锁次数接口用于指示在fpga成功加载后时钟锁相环失锁的次数,所述时钟锁相环失锁次数接口可以连接至fpga外部,用于故障指示或辅助故障排查。

27.图3所示为本发明较佳实施例中时钟配置及监控功能模块工作流程图。

28.参见图3,所述时钟配置及监控功能模块工作流程包括以下步骤:

29.s101:fpga加载完成,准备对可编程晶振进行配置;

30.fpga加载过程中,startup原语功能模块一直向时钟配置及监控功能模块发送cfgmclk信号,fpga加载完成,startup原语功能模块向时钟配置及监控功能模块发送eos信号;

31.s102:fpga按照默认频率或者用户逻辑指定的频率对可编程晶振进行配置;

32.时钟配置及监控功能模块接收到cfgmclk信号和eos信号后,通过晶振配置接口按照默认频率或者用户逻辑指定的频率对可编程晶振进行配置;

33.s103:fpga判断可编程晶振配置是否成功,如果是则转到s104,如果否则转到s102;

34.时钟配置及监控功能模块通过晶振配置接口访问可编程晶振内部寄存器,据此判断可编程晶振配置是否成功;

35.s104:复位fpga时钟锁相环;

36.时钟配置及监控功能模块通过时钟锁相环复位接口向时钟锁相环发送时钟锁相环复位信号,实现时钟锁相环复位;

37.s105:判断fpga时钟锁相环是否已锁定,如果是则转到s106,如果否则转到s108;

38.时钟配置及监控功能模块的时钟锁相环锁定指示接口接收到时钟锁相环发送的锁定信号,判断时钟锁相环已锁定;

39.s106:对用户逻辑功能模块进行复位;

40.时钟配置及监控功能模块通过用户逻辑复位接口向用户逻辑功能模块发送用户逻辑复位信号,实现用户逻辑功能模块复位;

41.s107:持续监控频率控制字是否发生改变,如果是则转到s102;

42.若时钟配置及监控功能模块接收到用户逻辑功能模块发送的频率控制字信号,则判断频率控制字发生改变,此时返回s102,时钟配置及监控模块将按照新的频率控制字对可编程晶振进行重新配置;

43.s108:失锁计数加1;

44.s109:判断失锁次数是否超过n,如果是则转至s110,如果否则转至s102;

45.s110:配置失败。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1