神经网络计算方法及光子神经网络芯片架构

1.本公开涉及人工智能技术领域、计算机芯片技术领域,更具体地,涉及一种神经网络计算方法及光子神经网络芯片架构。

背景技术:

2.随着光子技术迅速发展,光子神经网络芯片凭借光子作为信息传输载体的高带宽、低时延和低损耗特性,加速了神经网络模型中的推理运算过程,突破传统电子芯片的计算框架,但是通过光子神经网络进行高精度模拟计算时,会产生较高的功耗,不利于光子神经网络的发展。

3.在实现本公开构思的过程中,发明人发现相关技术中至少存在如下问题:如何解决光子模拟计算性能和计算功耗之间的平衡问题。

技术实现要素:

4.有鉴于此,本公开提供了一种神经网络计算方法及光子神经网络芯片架构。

5.本公开的一个方面提供了一种神经网络计算方法,包括:

6.通过电子逻辑芯片,接收与神经网络中的每一个计算层对应的计算任务,将所述计算任务划分为p个子计算任务,其中,p为正整数;通过所述电子逻辑芯片向q个光子神经网络核心发送p个所述子计算任务,其中,q为正整数,所述光子神经网络核心通过至少一种精度进行计算;通过q个所述光子神经网络核心对每个所述子计算任务计算得到对应的子计算结果;基于每个所述子计算结果,通过所述电子逻辑芯片确定所述计算层的计算结果;根据所述神经网络中每一个计算层的所述计算结果,确定所述神经网络的输出结果。

7.根据本公开的实施例,其中,所述光子神经网络核心包括核心缓存单元、数模转换器阵列和光子计算单元,所述通过q个所述光子神经网络核心对所述子计算任务计算得到对应的子计算结果,包括:针对每个所述光子神经网络核心,通过所述核心缓存单元接收所述子计算任务并发送到所述数模转换器阵列;所述数模转换器阵列将所述子计算任务的第一数字电信号转换为第一模拟电信号发送到所述光子计算单元;通过所述光子计算单元对所述子计算任务计算得到对应的所述子计算结果。

8.根据本公开的实施例,其中,所述光子计算单元包括激光器、调制器阵列和探测器阵列,所述通过所述光子计算单元对所述子计算任务计算得到对应的所述子计算结果,包括:通过所述调制器阵列接收所述子计算任务的第一模拟电信号和所述激光器发出的恒定光信号;根据所述恒定光信号对所述子计算任务进行计算得到对应的所述子计算结果的第一光信号;通过所述探测器阵列将所述第一光信号转换为所述子计算结果的第二模拟电信号。

9.根据本公开的实施例,其中,所述光子神经网络核心包括模数转换器阵列,所述基于每个所述子计算结果,通过所述电子逻辑芯片确定所述计算层的计算结果,包括:通过所述模数转换器阵列接收所述光子计算单元发送的子计算结果的第二模拟电信号并转换为

第二数字电信号;通过所述模数转换器阵列将所述第二数字电信号发送至所述电子逻辑芯片,以确定所述计算层的所述计算结果。

10.根据本公开的实施例,其中,所述计算层包括卷积神经网络的卷积层,所述通过电子逻辑芯片,接收与神经网络中的每一个计算层对应的计算任务,将所述计算任务划分为p个子计算任务,包括:通过所述电子逻辑芯片,接收与所述卷积神经网络中的每一个所述卷积层对应的所述计算任务,将所述计算任务划分为p个子计算任务,其中,所述计算任务包括对输入图像和所述卷积层的卷积核进行计算。

11.根据本公开的实施例,其中,所述计算层包括全连接神经网络的全连接层,所述通过电子逻辑芯片,接收与神经网络中的每一个计算层对应的计算任务,将所述计算任务划分为p个子计算任务,包括:通过所述电子逻辑芯片,接收与所述全连接神经网络中的每一个所述全连接层对应的所述计算任务,将所述计算任务划分为p个子计算任务,其中,所述计算任务包括对所述全连接层中的子矩阵进行计算。

12.本公开的另一方面提供了一种光子神经网络芯片架构,包括:q个光子神经网络核心,用于通过至少一种精度对神经网络的每个计算层的计算任务进行计算,其中,n为正整数;电子逻辑芯片,用于将所述计算任务划分为p个子计算任务以及向q个所述光子神经网络核心发送所述子计算任务以及接收计算结果,其中,q为正整数。

13.根据本公开的实施例,其中,所述光子神经网络核心包括:核心缓存单元,用于对第一数字电信号和第二数字电信号进行接收、发送和缓存,其中,所述第一数字电信号包括所述子计算任务,第二数字电信号包括所述子计算结果;数模转换器阵列,用于接收所述第一数字电信号,以及将所述第一数字电信号转换为第一模拟电信号发送至光子计算单元,其中,所述第一模拟电信号包括所述子计算任务;所述光子计算单元,用于对接收到的所述第一模拟电信号进行计算得到第二模拟电信号,以及将所述第二模拟电信号发送至模数转换器阵列,其中,所述第二模拟电信号包括所述子计算结果;所述模数转换器阵列,用于接收所述第二模拟电信号,以及将所述第二模拟电信号转换为第二数字电信号发送至所述核心缓存单元。

14.根据本公开的实施例,其中,所述光子计算单元包括:激光器,用于与调制器阵列连接,以及提供恒定光信号;所述调制器阵列,用于根据接收所述恒定光信号和所述第一模拟电信号进行计算得到第一光信号,以及将所述第一光信号发送至探测器阵列;所述探测器阵列,用于将接收到的所述第一光信号转换为第二模拟电信号,以及发送到所述模数转换器阵列。

15.根据本公开的实施例,其中,所述电子逻辑芯片包括:公共缓存单元,用于对所述计算任务和所述计算结果进行发送和接收;逻辑控制单元,用于控制所述公共缓存单元和逻辑运算单元。逻辑运算单元,用于提供所述芯片的算子和函数。

16.根据本公开的实施例,电子逻辑芯片可以将神经网络的计算层的计算任务划分为p个子计算任务,然后再发送至q个光子神经网络核心进行计算,光子神经网络核心可以通过至少一种精度进行计算,根据光子神经网络核心计算得到子计算结果,电子逻辑芯片确定计算层的计算结果,然后再根据神经网络中每一个计算层的计算结果,确定神经网络的输出结果,通过将神经网络的计算任务划分为多个子计算任务,并发送至多个光子神经网络核心以不同计算精度进行线性计算,至少部分地克服了光子模拟计算性能和计算功耗之

间的平衡问题,可以实现多种深度神经网络模型的灵活部署,提升了光子神经网络的计算性能。

附图说明

17.通过以下参照附图对本公开实施例的描述,本公开的上述以及其他目的、特征和优点将更为清楚,在附图中:

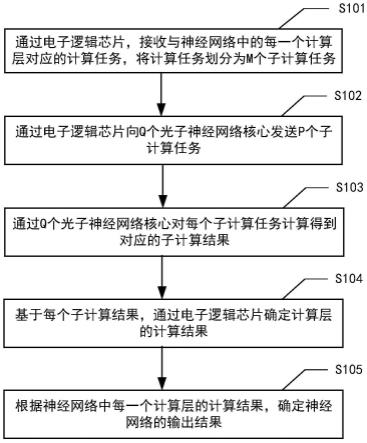

18.图1示意性示出了根据本公开实施例的神经网络计算方法的流程图;

19.图2a示意性示出了根据本公开实施例的神经网络计算方法对卷积神经网络卷积层的计算方法的示意图;

20.图2b示意性示出了根据本公开实施例的神经网络计算方法对全连接神经网络全连接层的计算方法的示意图;

21.图3示意性示出了根据本公开实施例的神经网络计算方法对深度神经网络lenet的计算方法流程图;

22.图4示意性示出了根据本公开的实施例的光子神经网络芯片架构的框图;

23.图5示意性示出了根据本公开的实施例的一种光子神经网络核心结构的框图;

24.图6示意性示出了根据本公开的实施例的光子计算单元结构的框图;

25.图7a示意性示出了根据本公开实施例的调制器阵列的基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列示意图;

26.图7b示意性示出了根据本公开实施例的调制器阵列的基于相干点乘网络结构的马赫曾德干涉仪阵列示意图;

27.图7c示意性示出了根据本公开实施例的调制器阵列的基于广播权重组网络结构的微环谐振器阵列示意图;

28.图7d示意性示出了根据本公开实施例的调制器阵列的基于交叉阵列网络结构的微环谐振器阵列示意图;以及

29.图8示意性示出了根据本公开的实施例的电子逻辑芯片结构的框图。

具体实施方式

30.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。在下面的详细描述中,为便于解释,阐述了许多具体的细节以提供对本公开实施例的全面理解。然而,明显地,一个或多个实施例在没有这些具体细节的情况下也可以被实施。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

31.在此使用的术语仅仅是为了描述具体实施例,而并非意在限制本公开。在此使用的术语“包括”、“包含”等表明了所述特征、步骤、操作和/或部件的存在,但是并不排除存在或添加一个或多个其他特征、步骤、操作或部件。

32.在此使用的所有术语(包括技术和科学术语)具有本领域技术人员通常所理解的含义,除非另外定义。应注意,这里使用的术语应解释为具有与本说明书的上下文相一致的含义,而不应以理想化或过于刻板的方式来解释。

33.在使用类似于“a、b和c等中至少一个”这样的表述的情况下,一般来说应该按照本

领域技术人员通常理解该表述的含义来予以解释(例如,“具有a、b和c中至少一个的系统”应包括但不限于单独具有a、单独具有b、单独具有c、具有a和b、具有a和c、具有b和c、和/或具有a、b、c的系统等)。在使用类似于“a、b或c等中至少一个”这样的表述的情况下,一般来说应该按照本领域技术人员通常理解该表述的含义来予以解释(例如,“具有a、b或c中至少一个的系统”应包括但不限于单独具有a、单独具有b、单独具有c、具有a和b、具有a和c、具有b和c、和/或具有a、b、c的系统等)。

34.随着光子技术迅速发展,光子神经网络芯片得到广泛研究,但大部分研究集中在小规模数据集和固定大小、单一功能的神经网络结构的实现,完成深度神经网络模型部分层的部署,还不能充分发挥光子神经网络芯片对人工智能运算的加速优势。此外,相比于成熟的数字电子技术,光子神经网络按照光学方式进行非线性计算时会增加功耗,失去光子线性计算时的高速低功耗优势,而高精度模拟计算还会额外增加模数/数模转换的计算开销,导致光子神经网络芯片的应用受阻,并且,。当前以单核心为主的光子神经网络芯片在计算规模和通用性上受限,扩大芯片规模会导致噪声、损耗、功耗等一系列开销,造成计算精度下降,限制了光子神经网络的应用。为了获得更高的计算精度,在单核部署统一的高精度模拟计算方式也产生更大功耗,不利于光子神经网络的发展。因此,需要对光子神经网络芯片设计灵活配置的方法,解决光子计算在非线性运算方面的不足,进一步解决光子模拟计算性能和计算功耗之间的平衡问题。

35.本公开的实施例提供了一种神经网络计算方法。该方法包括通过电子逻辑芯片,接收与神经网络中的每一个计算层对应的计算任务,将计算任务划分为p个子计算任务,其中,p为正整数;通过电子逻辑芯片向q个光子神经网络核心发送p个子计算任务,其中,q为正整数,光子神经网络核心通过至少一种精度进行计算;通过q个光子神经网络核心对每个子计算任务计算得到对应的子计算结果;基于每个子计算结果,通过电子逻辑芯片确定计算层的计算结果;根据神经网络中每一个计算层的计算结果,确定神经网络的输出结果。

36.图1示意性示出了根据本公开实施例的神经网络计算方法的流程图。

37.如图1所示,该方法包括操作s101~s105。

38.在操作s101,通过电子逻辑芯片,接收与神经网络中的每一个计算层对应的计算任务,将计算任务划分为p个子计算任务,其中,p为正整数。

39.根据本公开的实施例,神经网络可以是包括输入层、输出层和多个隐藏层的深度神经网络,还可以是卷积神经网络或者全连接神经网络,例如,可以是lenet神经网络,包括3个卷积层、2个池化层、3个全连接层。

40.根据本公开的又一实施例,计算任务可以是外部计算机根据设定的神经网络的参数产生的。

41.根据本公开的又一实施例,可以将计算任务中的乘法运算划分为p个子计算任务的乘法。

42.在本公开的实施例中,计算层可以包括卷积神经网络的卷积层,可以通过电子逻辑芯片,接收与卷积神经网络中的每一个卷积层对应的计算任务,将计算任务划分为p个子计算任务,其中,计算任务包括对输入图像和卷积层的卷积核进行计算。

43.根据本公开的实施例,计算任务可以是卷积层中将输入图像转换为像素权重后与卷积核的向量乘法运算,例如,计算任务可以是卷积层汇总16*1维向量,可以将16*1维向量

划分为8个2维向量进行乘法运算。

44.在本公开的实施例中,计算层可以包括全连接神经网络的全连接层,可以通过电子逻辑芯片,接收与全连接神经网络中的每一个全连接层对应的计算任务,将计算任务划分为p个子计算任务,其中,计算任务包括对全连接层中的子矩阵进行计算。

45.根据本公开的实施例,计算任务可以是全连接层中的矩阵乘法运算,例如,计算任务可以是全连接层中的网络权重与输入的矩阵乘法运算,可以将矩阵拆分为4个子矩阵进行乘法运算。

46.在操作s102,通过电子逻辑芯片向q个光子神经网络核心发送p个子计算任务,其中,q为正整数,光子神经网络核心通过至少一种精度进行计算。

47.根据本公开的实施例,光子神经网络核心可以是同构核心或者异构核心,每个光子神经网络核心可以通过至少一种精度进行计算,例如,可以通过6位精度进行计算,还可以通过8位精度进行计算。

48.根据本公开的实施例,将p个子计算任务发送至q个光子神经网络核心可以是将8个子计算任务发送至8个光子神经网络核心,也可以是将8个子计算任务发送至4个光子神经网络核心,例如,可以将卷积神经网络的卷积层中8个2维向量子计算任务发送至8个光子神经网络核心,也可以将8个2维向量子计算任务发送至4个光子神经网络核心计算两次,还可以将全连接神经网络的全连接层中4个矩阵子计算任务发送至4个光子神经网络核心。

49.在操作s103,通过q个光子神经网络核心对每个子计算任务计算得到对应的子计算结果。

50.根据本公开的实施例,可以通过光子神经网络核心的不同计算精度对子计算任务进行计算。

51.在本公开的实施例中,光子神经网络核心包括核心缓存单元、数模转换器阵列和光子计算单元,可以针对每个光子神经网络核心,通过核心缓存单元接收子计算任务并发送到数模转换器阵列;数模转换器阵列将子计算任务的第一数字电信号转换为第一模拟电信号发送到光子计算单元;通过光子计算单元对子计算任务计算得到对应的子计算结果。

52.根据本公开的实施例,子计算任务可以通过第一数字电信号进行传递,第一数字信号可以携带子计算任务中的计算数据,例如,可以是输入矩阵和对应的网络权重。

53.根据本公开的又一实施例,核心缓存单元可以是静态随机存取存储器(static random-access memory,sram)。

54.根据本公开的又一实施例,数模转换器阵列可以是数模转换阵器集成芯片或模块,数模转换器阵列的转换精度可以是2位至20位精度。

55.在本公开的实施例中,光子计算单元可以包括激光器、调制器阵列和探测器阵列,可以通过调制器阵列接收子计算任务的第一模拟电信号和激光器发出的恒定光信号;根据恒定光信号对子计算任务进行计算得到对应的子计算结果的第一光信号;通过探测器阵列将第一光信号转换为子计算结果的第二模拟电信号。

56.根据本公开的实施例,激光器可以是可调谐激光器或多波长激光器。

57.根据本公开的又一实施例,调制器阵列可以是基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列、基于相干点乘网络结构的马赫曾德干涉仪阵列、基于广播权重组网络结构的微环谐振器阵列或基于交叉阵列网络结构的微环谐振器阵列,调制器阵列可以是热

光调制器、电光调制器或相变材料调制器。

58.根据本公开的又一实施例,调制器阵列可以根据恒定光信号对第一模拟电信号中的子计算任务进行计算,然后得到对应的子计算结果。

59.根据本公开的实施例,可以通过探测器阵列接收子计算结果的第一光信号,转换为第二模拟电信号后发送到模数转换器阵列。

60.在操作s104,基于每个子计算结果,通过电子逻辑芯片确定计算层的计算结果。

61.根据本公开的实施例,可以通过每个子计算任务对应的子计算结果确定当前计算层的计算结果。

62.在本公开的实施例中,光子神经网络核心可以包括模数转换器阵列,通过模数转换器阵列接收光子计算单元发送的子计算结果的第二模拟电信号并转换为第二数字电信号;通过模数转换器阵列将第二数字电信号发送至电子逻辑芯片,以确定计算层的计算结果。

63.根据本公开的实施例,模数转换器阵列可以是模数转换阵器集成芯片或模块,模数转换器阵列的转换精度可以是2位至20位精度。

64.在操作s105,根据神经网络中每一个计算层的计算结果,确定神经网络的输出结果。

65.根据本公开的实施例,上一个计算层的计算结果可以作为当前计算层的输入然后对当前计算层进行计算,根据最后的计算结果,确定神经网络的输出结果。

66.根据本公开的实施例,电子逻辑芯片可以将神经网络的计算层的计算任务划分为p个子计算任务,然后再发送至q个光子神经网络核心进行计算,光子神经网络核心可以通过至少一种精度进行计算,根据光子神经网络核心计算得到子计算结果,电子逻辑芯片确定计算层的计算结果,然后再根据神经网络中每一个计算层的计算结果,确定神经网络的输出结果,通过将神经网络的计算任务划分为多个子计算任务,并发送至多个光子神经网络核心以不同计算精度进行线性计算,至少部分地克服了光子模拟计算性能和计算功耗之间的平衡问题,可以实现多种深度神经网络模型的灵活部署,提升了光子神经网络的计算性能。

67.为了更好的理解本公开实施例所提出的神经网络计算方法,下面结合图2a和图2b进行说明。

68.图2a示意性示出了根据本公开实施例的神经网络计算方法对卷积神经网络卷积层的计算方法的示意图。

69.如图2a所示,对一个4维神经元到4维神经元仿射的全连接神经网络进行计算,可以映射为4*4的矩阵乘法计算任务,其中网络权重为w

11

、w

12

、

…w44

,输入为x1、x2、x3、x4,可以通过电子逻辑芯片存储来自外部计算机设备的数据流。

70.通过电子逻辑芯片将计算任务中的矩阵乘法划分为4个子矩阵的子计算任务,其中,每个子计算任务中的子矩阵维度为2*2,将子计算任务发送给4个光子神经网络芯片核心。

71.通过4个2~20位精度的光子神经网络芯片核心完成子计算任务的运算后,生成中间运算数据x

1(1)

、x

2(1)

、x

3(1)

、x

4(1)

和x

1(2)

、x

2(2)

、x

3(2)

,并发送到电子逻辑芯片。

72.再通过电子逻辑芯片的逻辑运算单元完成累加计算,生成x1’

、x2’

、x3’

、x4’

,进行

偏置b和激活函数操作,生成运算结果y1、y2、y3、y4,并发送到电子逻辑芯片。

73.图2b示意性示出了根据本公开实施例的神经网络计算方法对全连接神经网络全连接层的计算方法的示意图。

74.如图2b所示,对2*2维卷积核和4*4维图像的进行卷积计算,其中卷积核权重为k1、k2、k3、k4,图像的每个像素权重为x

11

、x

12

、

…

x

44

,将图像转换为16*1维向量的计算任务,可以通过电子逻辑芯片存储来自外部计算机设备的数据流。

75.通过电子逻辑芯片将16*1维向量的计算任务划分为8个2维向量的子计算任务,每个子计算任务维度为2*2,将8个子计算任务发送给8个子光子神经网络芯片核心。

76.通过8个2~20位精度的光子神经网络芯片核心完成子计算运算后,生成中间运算数据x

11’、x

12’、

…

x

44’,并发送到电子逻辑芯片。

77.使用电子逻辑芯片完成累加和偏置b操作,生成3*3维卷积图o

11

、o

12

、

…o33

,对非线性操作算子进行重构,对卷积图进行激活函数和步长为1的2*2池化操作,生成2*2维卷积结果y1、y2、y3、y4,发送到电子逻辑芯片。

78.图3示意性示出了根据本公开实施例的神经网络计算方法对深度神经网络lenet的计算流程图。

79.如图3所示,该流程包括以下步骤s301-s308。

80.步骤s301,对第一个卷积层的计算任务进行计算。

81.根据本公开的实施例,可以将mnist数据集中32*32维灰度图像作为输入,将lenet神经网络模型的第一个卷积层中6个5*5卷积核对输入图像的卷积子计算任务划分为6*(32-5+1)*(32-5+1)=4704个子计算任务,发送到6个光子神经网络核心进行784次计算,可以通过6位精度的基于交叉阵列网络结构的微环谐振器阵列进行计算。可以在电子逻辑芯片完成第一个卷积层的累加计算,得到6个28*28维的计算结果。

82.步骤s302,对第一池化层进行重构。

83.根据本公开的实施例,可以使用s301中6个28*28维的计算结果作为输入,将第一个池化层中步长为2的2*2池化操作映射为累加和激活函数计算,在电子逻辑芯片动态重构池化算子完成第一个池化层的逻辑计算,得到6个14*14维的计算结果。

84.步骤s303,对第二个卷积层的计算任务进行计算。

85.根据本公开的实施例,可以使用s302中6个14*14维的计算结果作为输入,将lenet神经网络模型的第二个卷积层中16个5*5卷积核将输入图像的16*(14-5+1)*(14-5+1)=1600个子计算任务发送到16个光子神经网络核心进行100次计算,可以通过6位精度的基于交叉阵列网络结构的微环谐振器阵列完成计算。可以在电子逻辑芯片完成第二个卷积层的累加计算,得到16个10*10维的计算结果。

86.步骤s304,对第二池化层进行重构。

87.可以通过s303中16个10*10维的计算结果作为输入,将lenet神经网络模型的第二个池化层中步长为2的2*2池化操作映射为累加和激活函数计算,在电子逻辑芯片动态重构池化算子完成第二个池化层的逻辑计算,得到16个5*5维的计算结果,展平为400*1维向量。

88.步骤s305,对第一个全连接层的计算任务进行计算。

89.可以通过s304中400*1维的矩阵计算结果作为输入,将lenet神经网络模型第一个全连接层中400*120的矩阵计算划分为48000个10*10的子计算任务,发送到16个光子神经

网络核心,进行3000次运算,可以通过8位精度的基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列进行计算,可以在电子逻辑芯片完成第一个全连接层的累加计算,得到120*1维的矩阵计算结果。

90.步骤s306,对第二个全连接层的计算任务进行计算。

91.可以通过s305中120*1维的矩阵计算结果作为输入,将lenet神经网络模型的第二个全连接层中120*84的矩阵计算划分为630个4*4的子计算任务,发送到10个光子神经网络核心,进行63次运算,可以通过8位精度的基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列进行计算。可以在电子逻辑芯片完成第二个全连接层的累加计算,得到84*1维的矩阵计算结果。

92.步骤s307,对第三个全连接层的计算任务进行计算。

93.可以通过s306中84*1维的矩阵计算结果作为输入,将lenet神经网络模型的第三个全连接层中84*10的矩阵计算划分为105个4*2的子计算任务,发送到5个光子神经网络核心,进行21次运算,可以通过8位精度的基于相干点乘网络结构的马赫曾德干涉仪阵列完成第三个全连接层的线性计算,在电子逻辑芯片完成第三个全连接层的累加计算,得到10*1维的矩阵计算结果,动态重构softmax分类函数,得到0~9数字的识别概率,取最大概率作为识别结果,完成最终计算结果。

94.步骤s308,输出计算结果。

95.根据本公开的实施例,可以将最终计算结果存储在电子逻辑芯片,可以通过高速串行接口发送给外部的计算机设备,进行后续评估分析。

96.图4示意性示出了根据本公开的实施例的光子神经网络芯片架构400的框图。

97.如图4所示,光子神经网络芯片架构400包括q个光子神经网络核心410和电子逻辑芯片420。

98.q个光子神经网络核心410,用于通过至少一种精度对神经网络的每个计算层的计算任务进行计算,其中,q为正整数。

99.电子逻辑芯片420,用于将计算任务划分为p个子计算任务以及向q个光子神经网络核心410发送子计算任务以及接收计算结果,其中,q为正整数。

100.根据本公开的实施例,光子神经网络核心410可以为同构核心或异构核心,每个核心可以配置不同的计算精度,并且可以独立运行,每个光子神经网络核心410都可以使用电信号作为输入和输出,光子神经网络核心410的输入端口和输出端口可以独立地与电子逻辑芯片420相连,图中所示的光子神经网络核心410包括6个,可以根据实际情况进行调整,在此不做限定。

101.根据本公开的又一实施例,电子逻辑芯片420可以是芯粒(chiplet)构成的多功能异构系统级封装(system in package,sip)。

102.根据本公开的又一实施例,光子神经网络芯片架构400还可以包括高速串行接口,用于连接光子神经网络芯片架构和外部设备,进行数据传输,高速串行接口可以是pcie接口。

103.图5示意性示出了根据本公开的实施例的一种光子神经网络核心410结构的框图。

104.如图5所示,光子神经网络核心410包括核心缓存单元411、数模转换器阵列412、光子计算单元413和模数转换器阵列414。

105.核心缓存单元411,用于对第一数字电信号和第二数字电信号进行接收、发送和缓存,其中,第一数字电信号包括子计算任务,第二数字电信号包括子计算结果。

106.数模转换器阵列412,用于接收第一数字电信号,以及将第一数字电信号转换为第一模拟电信号发送至光子计算单元413,其中,第一模拟电信号包括子计算任务。

107.光子计算单元413,用于对接收到的第一模拟电信号进行计算得到第二模拟电信号,以及将第二模拟电信号发送至模数转换器阵列414,其中,第二模拟电信号包括子计算结果。

108.模数转换器阵列414,用于接收第二模拟电信号,以及将第二模拟电信号转换为第二数字电信号发送至核心缓存单元411。

109.根据本公开的实施例,核心缓存单元411可以是静态随机存取存储器(static random-access memory,sram)。

110.根据本公开的又一实施例,核心缓存单元411可以包括两个输入端口,一个输入端口与电子逻辑芯片420相连,可以存储来自电子逻辑芯片420的第一数字电信号输入,另一个输入端口与模数转换器阵列414相连,用于写入来自模数转换器阵列414的第二数字电信号,核心缓存单元411还可以包括两个输出端口,一个输出端口与数模转换器阵列412相连,可以读出核心缓存单元411中的第一数字电信号,另一个输出端口与电子逻辑芯片420相连,用于发送一个光子神经网络核心410的第二数字电信号。

111.根据本公开的又一实施例,数模转换器阵列412可以是数模转换阵器集成芯片或模块,数模转换器阵列412的转换精度可以是2位至20位精度。

112.根据本公开的又一实施例,数模转换器阵列412可以包括多个输出端口,用于将权重数据和向量数据并行加载到光子计算单元413。

113.根据本公开的又一实施例,光子计算单元413可以包括多个输入端口,用于接收来自数模转换器阵列412的并行第一模拟电信号,第一模拟电信号可以包括权重数据和向量数据。

114.根据本公开的又一实施例,光子计算单元413还可以包括多个输出端口,可以并行发送计算得到的第二模拟电信号。

115.根据本公开的又一实施例,模数转换器阵列414可以是模数转换阵器集成芯片或模块,模数转换器阵列414的转换精度可以是2位至20位精度。

116.根据本公开的又一实施例,模数转换器阵列414可以包括多个输入端口,可以接收来自光子计算单元413的并行第二模拟电信号。

117.图6示意性示出了根据本公开的实施例的光子计算单元413结构的框图。

118.如图6所示,光子计算单元413包括激光器4131、调制器阵列4132和探测器阵列4133。

119.激光器4131,用于与调制器阵列4132连接,以及提供恒定光信号;

120.调制器阵列4132,用于根据接收恒定光信号和第一模拟电信号进行计算得到第一光信号,以及将第一光信号发送至探测器阵列4133;

121.探测器阵列4133,用于将接收到的第一光信号转换为第二模拟电信号,以及发送到模数转换器阵列414。

122.根据本公开的实施例,激光器4131可以是可调谐激光器4131或多波长激光器

4131,可以通过耦合器与调制器阵列4132相连。

123.根据本公开的又一实施例,调制器阵列4132可以包括一个光信号输入端口和多个电信号输入端口,光信号端口可以接收来自激光器4131的光信号,电信号端口可以加载来自数模转换器阵列412的并行第一模拟电信号。

124.根据本公开的又一实施例,调制器阵列4132可以是基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列、基于相干点乘网络结构的马赫曾德干涉仪阵列、基于广播权重组网络结构的微环谐振器阵列或基于交叉阵列网络结构的微环谐振器阵列,调制器阵列4132可以是热光调制器、电光调制器或相变材料调制器。

125.下面参考图7a-7d对本公开的实施例的调制器阵列4132进一步说明。

126.图7a示意性示出了根据本公开实施例的调制器阵列4132的基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列示意图。

127.如图7a所示,基于矩阵奇异值分解网络结构的马赫曾德干涉仪阵列可以包括依次连接的1分n分束器、1

×

1mzi输入向量阵列xi、第一酉矩阵阵列对角矩阵阵列σ和第二酉矩阵阵列u。

128.根据本公开的实施例,1分n分束器可以将外部激光器输入的单波长光均匀分为n路,包括log2n层级联的1分2分束器,分束器的分束比为50:50,n为偶数,当输入向量为偶数使用全部出光口,当输入向量为奇数使用n-1个出光口。

129.根据本公开的又一实施例,1

×

1mzi输入向量阵列xi可以将数据集向量通过1

×

1mzi调制到光路上,形成n维输入向量,1

×

1mzi包括内部移相器θ,通过调节移相器θ将xi编码到光路上。

130.根据本公开的又一实施例,第一酉矩阵阵列对角阵阵列σ和第二酉矩阵阵列u可以完成n

×

1维向量和n

×

n维矩阵乘法,将n

×

n维矩阵a进行奇异值分解,即映射为依次连接的第一酉矩阵阵列对角阵阵列σ和第二酉矩阵阵列u,当n路光传播过σ、u,完成n

×

n维矩阵乘法,其中u是n

×

n维酉矩阵,σ是n

×

n维对角矩阵。

131.根据本公开的又一实施例,第一酉矩阵阵列和第二酉矩阵阵列u可以计算n

×

n维矩阵a奇异值分解得到的和u酉矩阵,酉矩阵阵列包括三角形结构和矩形结构,通过级联光路交叉节点的2

×

2mzi形成n

×

n维酉矩阵和u;2

×

2mzi,包括内部移相器θ和外部移相器通过调节移相器θ和形成2

×

2酉矩阵。

132.根据本公开的又一实施例,对角矩阵阵列σ可以计算n

×

n维矩阵a奇异值分解得到的σ对角矩阵,n

×

n维对角矩阵等价于n维向量,通过n路1

×

1mzi将σ的对角元素编码到n个光路上。

133.图7b示意性示出了根据本公开实施例的调制器阵列4132的基于相干点乘网络结构的马赫曾德干涉仪阵列示意图。

134.如图7b所示,基于相干点乘网络结构的马赫曾德干涉仪阵列可以包括依次连接的1分n分束器、1

×

1mzi输入向量阵列xi和1

×

1mzi权重向量阵列wi。

135.根据本公开的实施例,1分n分束器可以将外部激光器输入的单波长光均匀分为n路,包括log2n层级联1分2分束器,分束器的分束比为50:50,n为偶数,当输入向量为偶数使

用全部出光口,当输入向量为奇数使用n-1个出光口。

136.根据本公开的又一实施例,1

×

1mzi输入向量阵列xi可以将数据集向量通过1

×

1mzi调制到光路上,形成n维输入向量,1

×

1mzi包括内部移相器θ,通过调节移相器θ将xi编码到光路上。

137.根据本公开的又一实施例,1

×

1mzi输入向量阵列xi可以将数据集向量通过1

×

1mzi调制到光路上,形成n维输入向量,1

×

1mzi包括内部移相器θ,通过调节移相器θ将xi编码到光路上。

138.根据本公开的又一实施例,1

×

1mzi权重向量阵列wi可以完成n

×

1维向量和n

×

m维矩阵乘法,将矩阵乘法分解为m个n维向量内积,矩阵权重向量通过1

×

1mzi调制到光路上,形成n维权重向量,完成一个xi*wi点乘操作。

139.图7c示意性示出了根据本公开实施例的调制器阵列4132的基于广播权重组网络结构的微环谐振器阵列示意图。

140.如图7c所示,基于广播权重组网络结构的微环谐振器阵列可以包括依次连接的复用器、微环谐振器输入向量阵列xi、1分n分束器和n

×

m维微环谐振器广播权重组阵列。

141.根据本公开的实施例,复用器可以将外部激光器输入的n个波长光复用到一条光路上。

142.根据本公开的又一实施例,微环谐振器输入向量阵列xi可以将数据集向量通过n个微环调制器调制到光路上,每个微环调制器可以对一个波长调制,形成n维输入向量。

143.根据本公开的又一实施例,1分n分束器可以将微环谐振器输入向量阵列xi输入的n个波长光均匀分为n路,每路光包括已调制的n个波长,包括log2n层级联1分2分束器,分束器的分束比为50:50,n为偶数,当输入向量为偶数使用全部出光口,当输入向量为奇数使用n-1个出光口。

144.根据本公开的又一实施例,n

×

m维微环谐振器广播权重组阵列,用于完成n

×

m维矩阵乘法,包括n*m个微环,每一行的n个微环权重组用于分别控制λ1~λn波长,对应n个xi*wi内积操作,不同行的微环权重组用于执行不同内积操作,使m行输出m个不同内积操作,每一行输出光路自动完成求和操作,输出m维向量。

145.图7d示意性示出了根据本公开实施例的调制器阵列4132的基于交叉阵列网络结构的微环谐振器阵列示意图。

146.如图7d所示,基于交叉阵列网络结构的微环谐振器阵列可以包括依次连接的复用器、1分n分束器、1

×

1mzi输入向量阵列xi和n

×

m维微环谐振器交叉阵列。

147.根据本公开的实施例,复用器可以将外部激光器输入的n个波长光复用到一条光路上。

148.根据本公开的又一实施例,1分n分束器可以将复用器输入的n个波长光均匀分为n路,每路光包括n个波长,包括log2n层级联1分2分束器,分束器的分束比为50:50,n为偶数,当输入向量为偶数使用全部出光口,当输入向量为奇数使用n-1个出光口。

149.根据本公开的又一实施例,1

×

1mzi输入向量阵列xi可以将数据集向量通过1

×

1mzi调制到光路上,形成n维输入向量,1

×

1mzi包括内部移相器θ,通过调节移相器θ将xi编码到光路上。

150.根据本公开的又一实施例,n

×

m维微环谐振器交叉阵列,用于完成n

×

m维矩阵乘

法,包括n*m个微环,其中n≥m,每一列的n个微环用于分别控制λ1~λn波长,对应n个xi*wi内积操作,相邻列的微环控制的波长错开一个波长,使m列输出m个不同内积操作,每一列输出光路自动完成求和操作,输出m维向量。

151.图8示意性示出了根据本公开的实施例的电子逻辑芯片420结构的框图。

152.如图8所示,电子逻辑芯片420包括公共缓存单元421、逻辑控制单元422和逻辑运算单元423。

153.公共缓存单元421,用于对计算任务和计算结果进行发送和接收。

154.逻辑控制单元422,用于控制公共缓存单元421和逻辑运算单元423。

155.逻辑运算单元423,用于提供芯片的算子和函数。

156.根据本公开的实施例,公共缓存单元421可以是静态随机存取存储器(static random-access memory,sram),公共缓存单元421可以接收来自高速串行接口的指令和数据流,还可以写入逻辑运算单元423输出的计算结果,然后发送到高速串行接口。

157.根据本公开的又一实施例,逻辑控制单元422可以是现场可编程逻辑门阵列(field programmable gate array,fpga)、专用集成电路(application specific integrated circuit,asic)或中央处理器(central processing unit,cpu)。

158.根据本公开的又一实施例,逻辑控制单元422可以控制公共缓存单元421根据指令向不同光子神经网络发送不同的计算任务,并对公共缓存单元421的数据进行控制;逻辑控制单元422还可以控制逻辑运算单元423根据指令对逻辑运算单元423的算子和函数进行重构。

159.根据本公开的又一实施例,逻辑运算单元423可以是现场可编程逻辑门阵列(field programmable gate array,fpga)、专用集成电路(application specific integrated circuit,asic)、中央处理器(central processing unit,cpu)或图形处理器(graphics processing unit,gpu)。

160.根据本公开的又一实施例,逻辑运算单元423可以接收不同的光子神经网络核心410的第二数字电信号,并进行逻辑运算,逻辑运算单元423可以进行累加操作、池化操作、非线性激活函数或者自定义函数。

161.附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,上述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图或流程图中的每个方框、以及框图或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。本领域技术人员可以理解,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合和/或结合,即使这样的组合或结合没有明确记载于本公开中。特别地,在不脱离本公开精神和教导的情况下,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合和/或结合。所有这些组合和/或结合均落入本公开的范围。

162.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而

并非为了限制本公开的范围。尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。本公开的范围由所附权利要求及其等同物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1