包括安全处理器的片上系统和包括该片上系统的半导体系统的制作方法

包括安全处理器的片上系统和包括该片上系统的半导体系统

1.相关申请的交叉引用

2.本技术要求于2021年6月15日在韩国知识产权局提交的韩国专利申请no.10-2021-0077282的优先权,其全部内容通过引用并入本文。

技术领域

3.本公开涉及包括安全处理器的片上系统和包括该片上系统的半导体系统。

背景技术:

4.应用处理器(ap)可以以片上系统(以下简称为soc)的形式实现。soc可以代表一个芯片,在该芯片上集成了各种系统。由于soc集成了各种系统,因此soc的内部存储器(例如,静态随机存取存储器(sram))的容量可能受到限制。由于内部存储器的容量有限,因此soc可以与外部存储设备通信。

5.同时,soc可以包括提供soc的安全功能和安全存储位置的安全元件。此时,在soc的内部存储器和soc的外部存储器之间的通信中,需要在保持安全稳定性的同时提高通信速度。

技术实现要素:

6.本公开的各方面提供了一种具有提高的安全性和通信速度的片上系统和包括该片上系统的半导体系统。

7.本公开的各方面还提供了具有提高的安全性和通信速度的安全处理器。

8.根据本发明构思的一个方面,提供了一种片上系统,包括安全处理器,其中安全处理器包括:ram,该ram包括存储页的ram高速缓存区域和存储时间戳的时间戳表;加密/解密引擎,被配置为通过使用时间戳加密页;以及直接存储器存取dma模块,被配置为:将加密的页发送给设置在片上系统外部的第一存储器的交换区域,其中,第一存储器包括:标签表区域,存储由加密页的加密/解密引擎生成的标签;以及时间戳备份区域,备份时间戳,以及交换区域、标签表区域和时间戳备份区域被备份在设置在片上系统外部的第二存储器中。

9.根据本发明构思的一个方面,提供了一种安全处理器,包括:ram,被配置为存储对页进行存储的ram高速缓存区域和对用于加密页的时间戳进行存储的时间戳表;加密/解密引擎,被配置为:从ram接收页和时间戳,加密页,并且生成标签;以及dma模块,被配置为将加密的页发送给第一外部存储器的交换区域,并且将标签发送给第一外部存储器的标签表区域,其中交换区域和标签表区域备份在第二外部存储器中。

10.根据本发明构思的一个方面,提供了一种半导体系统,包括:片上系统,包括应用处理器和安全处理器,该应用处理器包括多个cpu核;以及第一存储器和第二存储器,设置在片上系统外部,其中,安全处理器包括:ram,被配置为存储ram高速缓存区域和时间戳表,所述ram高速缓存区域存储页,所述时间戳表存储时间戳;加密/解密引擎,被配置为通过使用时间戳加密页;以及dma模块,被配置为:将加密的页发送给第一存储器的交换区域,第一

存储器包括:标签表区域,存储由加密页的加密/解密引擎生成的标签;以及时间戳备份区域,备份时间戳,以及第二存储器包括非易失性数据备份区域,交换区域、标签表区域和时间戳备份区域被备份在非易失性数据备份区域中。

附图说明

11.通过参考附图详细描述本公开的示例实施例,本公开的上述和其它方面以及特征将变得更清楚,在附图中:

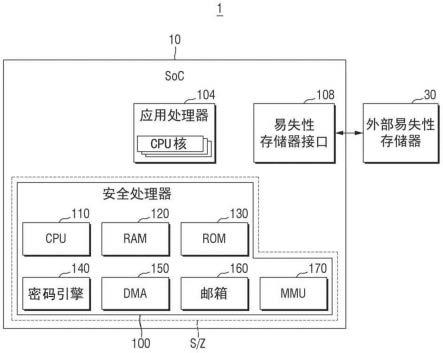

12.图1是示出根据一些实施例的包括片上系统的半导体系统的示例图。

13.图2是描述存储器管理表(mmt)的示例图。

14.图3是示出根据一些示例实施例的图1的半导体系统的操作的示例框图。

15.图4是描述根据一些示例实施例的图1的半导体系统的换出操作的示例梯形图。

16.图5是描述根据一些示例实施例的图1的半导体系统的换出操作的示例流程图。

17.图6是描述根据一些示例实施例的图1的半导体系统的换入操作的示例梯形图。

18.图7是描述根据一些示例实施例的图1的半导体系统的换入操作的示例流程图。

19.图8是示出根据一些示例实施例的包括片上系统的另一半导体系统的示例图,该片上系统包括安全处理器。

20.图9是示出根据一些示例实施例的图8的半导体系统的操作的示例框图。

21.图10和图11是描述根据一些示例实施例的图8的半导体系统的操作的示例梯形图。

22.图12是示出根据一些示例实施例的包括片上系统的另一半导体系统的示例图,该片上系统包括安全处理器。

23.图13是示出根据一些示例实施例的图12的半导体系统的操作的示例框图。

24.图14是描述安全数据信息区域的示例图。

25.图15和图16是描述图13的操作的示例流程图。

26.图17是示出根据一些示例实施例的图12的半导体系统的操作的另一示例框图。

27.图18和图19是描述图17的操作的示例流程图。

28.图20至图22是描述根据一些示例实施例的半导体系统的操作的示例流程图。

具体实施方式

29.图1是示出根据一些示例实施例的包括片上系统的半导体系统的示例图。

30.参考图1,根据一些示例实施例的半导体系统1包括片上系统10和设置在片上系统10外部的第一存储器30。

31.片上系统10包括应用处理器104、第一存储器接口108和安全处理器100。根据以下一些示例实施例的片上系统10的配置是示例性的,并且还可以包括图形处理单元(gpu)、编解码器、定标器、显示控制器、访问控制器等。

32.根据一些示例实施例的片上系统10可以被包括在例如以下中的任意一个中:服务器、计算机、智能电话、平板电脑、个人数字助理(pda)、数码相机、便携式多媒体播放器(pmp)、可穿戴设备、物联网(iot)设备、智能扬声器、汽车等,但不限于此。

33.应用处理器104包括多个cpu核并且可以处理片上系统10的总体任务。多个cpu核

中的每一个是支持trustzone的处理单元,并且例如可以是arm核。在以下描述中,假设cpu 110是arm核。

34.第一存储器接口108可以控制第一存储器30。

35.第一存储器30可以是易失性存储器。例如,第一存储器30可以是dram、sdram、ddram或sram,但不限于此。

36.安全处理器100可以包括cpu 110、ram 120、rom 130、加密/解密引擎140、直接存储器存取(dma)模块150、邮箱160和存储器管理单元(mmu)170。安全处理器100的配置是示例并且可以进一步包括例如不能物理复制的功能单元或随机数发生器。

37.安全处理器100与应用处理器104隔离并且可以由专用固件操作。例如,安全处理器100可以通过内部邮箱160与应用处理器104通信。即,虽然要由应用处理器104的多个cpu核处理的软件是在trustzone中执行的软件,但是对安全处理器100的访问可能是不可能的。除了应用处理器104提供的安全功能之外,通过在片上系统10内部单独地配置安全处理器100,可以提高安全性。例如,当未验证安全性时,从第一存储器30执行的软件可能无法访问安全处理器100中的ram 120。

38.cpu 110可以控制安全处理器100的总体操作。

39.rom 130例如可以是一次性可编程(otp)存储器。rom 130可以存储加密/解密引擎140执行加密操作所需的密钥。尽管通过安全处理器100执行的软件的一部分存储在外部存储器(例如,第一存储器30)中,但是它可以通过存储在安全处理器100的rom 130中的密钥来保持安全(保证机密性)。

40.ram 120是易失性存储器并且可以是例如sram。ram 120可以临时存储例如安全数据或安全代码等。此外,ram 120可以存储用于数据加密的时间戳或计数器。此外,ram 120可以存储存储器管理表(mmt)121。将参考图2详细描述存储器管理表。

41.图2是描述存储器管理表(mmt)的示例图。

42.参照图1和图2,存储器管理表121针对每个数据或页(以下称为页)存储虚拟存储器地址(va)和物理存储器地址(pa)。此外,存储器管理表121可以针对每个页存储脏度(dirtiness)d、有效性v和其他附加信息(etc)。

43.虚拟存储器地址va是由cpu 110执行的软件的每个页单元的虚拟地址。物理存储器地址pa是ram 120中的ram高速缓存区域的地址,由cpu 110执行的软件的页存储在ram 120中。

44.脏度d可以指示换入(swap in)到ram高速缓存区域的页在被换入之后是否已经被cpu 110改变。例如,当从第一存储器30换入到ram 120的ram高速缓存区域122的页随后被cpu 110改变时,可以在脏度d中指示脏。

45.有效性v可以指示关于每个页的信息(例如上述的虚拟存储器地址va、物理存储器地址pa和脏度d)是否有效。例如,当对应页的脏度d不正确时,指示无效的信息可以出现在有效性中。

46.再次参照图1,当安全区域s/z中的数据被发送到外部时,加密/解密引擎140可以对数据执行加密。备选地,当安全区域s/z外部的数据访问安全区域s/z时,加密/解密引擎140可以对数据执行解密。

47.例如,加密/解密引擎140可以包括加密/解密单元和散列单元。加密/解密单元可

以根据加密算法使用安全参数对从cpu 110发送的安全数据执行加密计算。当加密/解密单元执行加密计算时,可以使用存储在ram 120中的时间戳或计数器。在下文中,将使用时间戳来描述。通过加密/解密单元使用时间戳进行加密计算,可以避免将在主机环境中运行的软件的一部分改变为不同版本的重放攻击。

48.加密/解密单元可以对从外部存储器(例如,第一存储器30)发送的加密的数据执行解密计算。

49.由加密/解密单元使用的加密算法可以是高级加密标准(aes)、数据加密标准(des)、三重des、seed、高安全性和轻量级(hight)、aria、轻量级加密算法(lea)等。此外,例如,加密算法可以以分组密码模式执行加密计算。分组密码模式可以是伽罗瓦/计数器模式(gcm)、电子密码本(ecb)模式、密码块链接(cbc)模式、ctr模式、传播密码块链接(pcbc)模式、密码反馈(cfb)模式等。

50.散列单元可以使用安全参数计算消息认证码(mac)。散列单元可以通过使用基于散列的消息认证码(hmac)算法、基于密码的消息认证码(cmac)算法等来计算消息认证码。例如,在通过加密/解密单元对安全数据执行加密之后,散列单元可以针对加密数据生成标签。这样,当通过cpu 110执行的软件的数据的一部分被存储在外部存储器(例如,第一存储器30)中时,可以避免可能发生的篡改攻击(保证完整性)。

51.加密/解密引擎140可以即时(on the fly)执行加密和解密,并且可以同时生成如上所述的标签。

52.dma模块150可以连接到加密/解密引擎140,以将通过加密/解密引擎140加密的数据或页以及生成的标签发送到安全区域s/z的外部。此外,dma模块150可以将从安全区域s/z外部发送的数据或页以及标签发送给加密/解密引擎140。

53.存储器管理单元170使用存储在ram 120中的存储器管理表将由cpu 110执行的软件的虚拟地址快速转换为物理地址,并且帮助cpu 110访问ram内部的ram高速缓存区域中的代码、数据或页。

54.当执行大小大于ram 120的大小的软件时,ram 120可以使用外部存储器(例如,第一存储器30)。安全区域s/z中的ram 120可以具有较小的大小,例如从几十kb到几百kb。因此,为了在安全区域s/z中执行比安全区域s/z中的ram 120的大小更大的软件,可以利用由应用处理器104使用的外部存储器(例如,第一存储器30)。更详细地,由软件使用的信息(例如,存储器管理表、页等)可以从安全区域s/z中的ram 120换出(swap out)到外部存储器(例如,第一存储器30)。将参考图3描述在安全区域s/z中通过换出而执行比ram 120的大小大的软件的操作。此外,相反地,在图3中,还将描述用于将由软件使用的信息(例如,存储器管理表、页等)从外部存储器(例如,第一存储器30)读取到安全区域s/z中的ram 120中的换入操作。在下文中,外部存储器将被描述为第一存储器30。

55.图3是示出根据一些示例实施例的图1的半导体系统的操作的示例框图。

56.参照图1和图3,ram 120可以存储对多个存储器管理表121和多个页进行存储的ram高速缓存区域122、对多个时间戳进行存储的时间戳表123、对所有页执行时间戳功能的主时间戳124、以及对所有页执行标签功能的主标签125。

57.在存储器管理表121中,存储每个软件的存储器管理表。例如,用于第零软件的第零存储器管理表mmt#0、用于第一软件的第一存储器管理表mmt#1和/或用于第n软件的第n

存储器管理表mmt#n可以存储在存储器管理表121中。

58.由cpu 110执行的每个软件所使用的页可以存储在ram高速缓存区域122中。例如,在ram高速缓存区域122中,可以存储由cpu110执行的第零软件所使用的第零页page#0、第一页page#1和/或第n页page#n。

59.时间戳表123可以存储当对存储在ram高速缓存区域122中的每个页执行加密时使用的时间戳。例如,在时间戳表123中,可以存储用于加密第零页page#0的第零时间戳timestamp#0、用于加密第一页page#1的第一时间戳timestamp#1、和/或用于加密第n页page#n的第n时间戳timestamp#n。

60.主时间戳124可以用于当时间戳表123被换出到第一存储器30时执行的加密操作。此外,主时间戳124不限于此,并且可以用于当ram高速缓存区域122被换出到第一存储器30时执行的加密操作。

61.主标签125不限于此,并且可以用于当时间戳表123被换出到第一存储器30时执行的加密操作。此外,主标签125不限于此,并且可以用于当ram高速缓存区域122被换出到第一存储器30时执行的加密操作。

62.也就是说,当在安全区域s/z中操作的软件所使用的信息(例如,存储器管理表121和ram高速缓存区域122)被换出到第一存储器30时,必须对每一条信息执行加密。可以通过加密/解密引擎执行加密。将参考图4描述换出操作。

63.图4是描述根据一些示例实施例的图1的半导体系统的换出操作的示例梯形图。

64.参照图1、图3和图4,例如,描述了假设在安全区域s/z中执行的第零软件使用第一存储器30来操作的情况。

65.在第一存储器30中,通过加密/解密引擎140加密的用于第零软件的第零存储器管理表121可以通过dma模块150存储在第一存储器30中的存储器管理表备份区域300中。

66.此外,用于执行第零软件的目标页可以被加密并存储在第一存储器30的交换区域310中,并且在加密过程中生成的标签可以被存储在第一存储器30中的标签表区域320中。将详细描述该操作。

67.图4是描述换出过程的梯形图,并且省略对在第一存储器30中换出存储器管理表的操作的描述。

68.将要换出的页从ram高速缓存区域122发送到加密/解密引擎140(步骤s10)。此外,用于对要换出的页进行加密的时间戳也从时间戳表123发送到加密/解密引擎140(步骤s11)。步骤s10和s11的顺序不限于该图。例如,步骤s10和步骤s11可以同时发生,并且步骤s11可以在步骤s10之前执行。

69.加密/解密引擎140使用要换出的页和用于加密页的时间戳(不限于此,还可以使用存储在rom 130中的密钥和/或初始向量iv)对要换出的页加密(步骤s12)。在这种情况下,可以生成与要加密的页相对应的标签(或者可以是mac或hash,但不限于此,并且下文被描述为标签)。由加密/解密引擎140加密的页和生成的标签被发送给与加密/解密引擎140连接的dma模块150(步骤s13)。dma模块150可以将加密的页和生成的标签写入到第一存储器30(步骤s14)。通过此,可以完成换出操作。步骤s12、步骤s13和步骤s14可以同时进行。

70.写入第一存储器30的加密的页可以被写入第一存储器30的交换区域310。另外,写入第一存储器30的生成的标签可以被写入标签表区域320。

71.也就是说,第零软件的存储器管理表可以备份在第一存储器30的存储器管理表备份区域300中。此外,用于执行第零软件的页被加密并存储在交换区域310中。此外,将当用于执行第零软件的页被加密时生成的标签存储在标签表区域320中。

72.将参考图5的流程图描述上述换出操作。

73.图5是描述根据一些示例实施例的图1的半导体系统的换出操作的示例流程图。

74.参照图1、图3和图5,将要换出的页从ram高速缓存区域122发送到加密/解密引擎140,并且将用于对要换出的页进行加密的时间戳也从时间戳表123发送到加密/解密引擎140(步骤s100)。

75.加密/解密引擎140通过使用要换出的页和用于对页加密的时间戳对要换出的页加密,并生成与要加密的每个页相对应的标签(步骤s110)。

76.dma模块150可以将加密的页和生成的标签写入到第一存储器30(步骤s120)。通过此,可以完成换出操作。如上所述,步骤s110和步骤s120可以同时进行。

77.在下文中,在图6中,将描述备份在第一存储器30的存储器管理表备份区域300中的加密的存储器管理表和写入交换区域310的加密的页被换入到ram 120中的操作。备份在存储器管理表备份区域300中的加密的存储器管理表可以通过加密/解密引擎140进行解密,并且换入到ram 120的存储器管理表121。将参考图6和图7详细描述加密的页的换入操作。

78.图6是描述根据一些示例实施例的图1的半导体系统的换入操作的示例梯形图。

79.在下文中,将通过假设要由cpu 110执行的软件所使用的页不在ram高速缓存区域122中的情况来说明换入的描述。

80.参照图1、图3和图6,通过dma模块150读取要从第一存储器30换入的加密的页和与加密的页相对应的标签(步骤s21)。dma模块150将加密的页和与加密的页相对应的标签发送给与dma模块150连接的加密/解密引擎140(步骤s22)。加密/解密引擎140对加密的页解密,并且生成标签作为解密的结果(步骤s23)。在这种情况下,在解密过程中,可以使用图4的步骤s12中使用的时间戳(不限于此,还可以使用在图4的步骤s12中使用的密钥和/或初始向量(iv)等)。不限于此,步骤s21、步骤s22和步骤s23可以同时执行。此后,加密/解密引擎140将在步骤s23中生成的标签与写入第一存储器30的标签表区域320中的标签进行比较以验证安全性(步骤s24)。当在步骤s24中验证了安全性时,要换入的页从加密/解密引擎140被读取到ram高速缓存区域122(步骤s25)。通过此,可以完成换入操作。根据一些示例实施例的步骤s24可以在步骤s25之后执行。

81.将参考图7的流程图描述上述换入操作。

82.图7是描述根据一些示例实施例的图1的半导体系统的换入操作的示例梯形图。

83.参照图1、图3和图7,通过dma模块150读取要从第一存储器30换入的加密的页和与加密的页相对应的标签(步骤s200)。dma模块150将加密的页和与加密的页相对应的标签发送到与dma模块150连接的加密/解密引擎140(步骤s210)。加密/解密引擎140对加密的页解密,并且生成标签作为解密的结果(步骤s220)。在这种情况下,在解密过程中,可以使用图5的步骤s110中使用的时间戳(不限于此,还可以使用图5的步骤s110中使用的密钥和/或初始向量(iv)等)。不限于此,步骤s200、步骤s210和步骤s220可以同时执行。此后,加密/解密引擎140将在步骤s220中生成的标签与写入第一存储器30的标签表区域320中的标签进行

比较以验证安全性(步骤s230)。例如,如果通过步骤s220生成的标签与写入标签表区域320中的标签不同(“否”),则数据的安全性未得到验证,并且对安全区域s/z的访问被阻止(失败)。如果通过步骤s220生成的标签与写入标签表区域320中的标签相同(“是”),则数据的安全性得到验证,并且将要换入的页从加密/解密引擎140发送到ram高速缓存区域122(步骤s240)。根据一些示例实施例的步骤s230可以在步骤s240之后执行。通过此,可以完成换入操作。

84.在下文中,为了描述简单,将通过省略与上述描述重叠的描述来描述其他实施例。

85.图8是示出根据一些示例实施例的包括片上系统的另一半导体系统的示例图,该片上系统包括安全处理器。图9是示出根据一些示例实施例的图8的半导体系统的操作的示例框图。

86.参照图8和图9,根据一些示例实施例的另一半导体系统2还包括设置在片上系统10外部的另一外部存储器(例如,第二存储器20)。在下文中,另一外部存储器将被描述为第二存储器20。第二存储器20可以是非易失性存储器,例如nand flash。

87.根据一些示例实施例的另一片上系统10还包括与第二存储器20通信的第二存储器接口102。

88.当执行大于ram 120的大小的软件时,ram 120除了使用参考图1至图7描述的第一存储器30之外,还可以使用第二存储器20。

89.更详细地,被换出到第一存储器30的全部的存储器管理表备份区域300、交换区域310和标签表区域320可以存储在第二存储器20的安全非易失性数据备份区域200中。相反,在将存储在第二存储器20的安全非易失性数据备份区域200中的信息读入第一存储器30之后,可以执行换入操作。这将通过图10和图11的梯形图进行描述。

90.图10和图11是根据一些示例实施例的描述图8的半导体系统的操作的示例梯形图。

91.参照图8至图10,从ram 120换出到第一存储器30的全部的交换区域310、存储器管理表备份区域300和标签表区域320可以写入安全非易失性数据备份区域200(步骤s15)。从第一存储器30写入安全非易失性数据备份区域200的信息可以统称为安全非易失性数据。

92.参照图8、图9和图11,第一存储器30可以从第二存储器20的安全非易失性数据备份区域200读取全部的交换区域310、存储器管理表备份区域300和标签表区域320(步骤s20)。此后,可以将第一存储器30的页换入到安全区域s/z。

93.图12是示出根据一些示例实施例的包括片上系统的另一半导体系统的示例图,该片上系统包括安全处理器。

94.根据一些示例实施例的另一半导体系统3还包括设置在片上系统10外部的另一外部存储器(例如,安全非易失性存储器40)。安全非易失性存储器40可以是非易失性存储器,例如nand flash。

95.安全非易失性存储器40可以通过安全通道50与安全处理器100通信。因此,安全非易失性存储器40也可以包括在安全区域s/z中。例如,安全非易失性存储器40可以利用安全处理器100和共享密钥,并且可以通过上述密码算法(例如,aes、aes-gcm、des、triple des、seed、hight、aria或lea,或者基于散列的消息认证码算法)确保在安全非易失性存储器40和安全处理器100之间传输的数据的安全性。dma 150可以被配置为通过安全通道50将主时

间戳和主标签发送到安全非易失性存储器40的安全数据信息区域。

96.安全非易失性存储器40可以将安全相关信息存储在安全数据信息区域400中,以为安全处理器100断电的情况做准备。将参考图13对此进行详细描述。

97.图13是示出根据一些示例实施例的图12的半导体系统的操作的示例框图。

98.参照图12和图13,主时间戳124和主标签125可以存储在安全非易失性存储器40中的安全数据信息区域400中。将参考图14更详细地描述安全数据信息区域400。

99.图14是描述安全数据信息区域的示例图。

100.参照图12到图14,安全数据信息区域400包括由cpu 110执行的每个软件的安全数据信息。

101.更详细地,安全数据信息区域400存储每个软件的通用唯一标识符(uuid)、活动设置(active set)信息、不同类型的主时间戳(主时间戳a和主时间戳b)以及不同类型的主标签(例如,主标签a和主标签b)。

102.每个软件具有不同的通用唯一标识符(uuid)。因此,cpu 110可以通过通用唯一标识符(uuid)来识别正在执行的软件。

103.活动设置信息可以指示每个软件的主时间戳和主标签的类型。例如,当活动设置信息激活a时,软件当前使用的主时间戳变为主时间戳a,并且软件当前使用的主标签变为主标签a。类似地,当活动设置信息激活b时,软件当前使用的主时间戳变为主时间戳b,并且软件当前使用的主标签变为主标签b。

104.在安全数据信息区域400中针对每个软件存储的主时间戳和主标签的类型不限于此,并且可以具有主时间戳c和主标签c。

105.再次参照图12和图13,ram 120的时间戳表区域123可以被加密并备份在第一存储器30的时间戳表备份区域330中。更详细地,当加密/解密引擎140对ram 120的时间戳表区域123加密时,可以使用主时间戳124来执行加密。

106.当安全处理器100和/或片上系统断电时,以及当安全处理器100和/或片上系统通电时,将参考图15和图16描述安全处理器100利用第一存储器30的操作。

107.图15和图16是描述图13的操作的示例流程图。

108.首先,参照图12、图13和图15,确定ram 120、安全处理器100和/或片上系统是否被安排断电(步骤s300)。如果没有安排ram120、安全处理器100和/或片上系统断电(“否”),则安全处理器100不执行附加操作。如果安排了ram 120、安全处理器100和/或片上系统断电(“是”),则执行参考图5描述的换出操作,并且存储在ram120中的时间戳表区域123被加密并且被发送到第一存储器30(步骤s310)。此后,将ram 120的主时间戳124和主标签125备份在安全数据信息区域400中(步骤s320)。在根据一些示例实施例的半导体系统的操作中,步骤s320和步骤s310的顺序可以互换。

109.参照图12、图13和图16,检查ram 120、安全处理器100和/或片上系统是否通电(步骤s400)。如果ram 120、安全处理器100和/或片上系统未通电(“否”),则ram 120、安全处理器100和/或片上系统不执行附加操作。如果ram 120、安全处理器100和/或片上系统通电(“是”),则ram 120的主时间戳124用于对备份在第一存储器30的时间戳表备份区域330中的加密的时间戳解密,并将在该过程中生成的标签与主标签125进行比较。此时,通过确定在解密过程中生成的标签是否与主标签125相同来验证安全性(步骤s410)。例如,当确定在

解密过程中生成的标签与主标签125相同时,识别出安全性得到验证。此后,执行从第一存储器30到ram 120的换入(步骤s420)。

110.图17是示出根据一些示例实施例的图12的半导体系统的操作的另一示例框图。

111.参照图12和图17,根据一些示例实施例的另一半导体系统3可以将换出到第一存储器30的全部的存储器管理表备份区域300、交换区域310、标签表区域320、以及时间戳备份区域330存储在第二存储器20的安全非易失性数据备份区域200中。相反,在将存储在第二存储器20的安全非易失性数据备份区域200中的信息读入第一存储器30之后,可以执行换入操作。第一存储器接口108和第二存储器接口102可以被配置为基于来自应用处理器104的命令进行通信以将第一存储器30的交换区域、标签表区域和时间戳备份区域备份在第二存储器20中。

112.例如,当安全处理器100、片上系统和/或半导体系统断电时,以及当安全处理器100、片上系统和/或半导体系统通电时,将参考图18和图19描述安全处理器100利用第一存储器30和第二存储器20的操作。在下文中,将描述半导体系统断电和/或通电的情况作为示例。

113.图18和图19是描述图17的操作的示例流程图。

114.参照图12、图13和图18,确定是否安排了半导体系统断电(步骤s500)。当没有安排半导体系统的断电时(“否”),半导体系统不执行附加操作。如果安排了半导体系统断电(“是”),则执行参考图5描述的换出操作,存储在ram 120中的时间戳表区域123被加密,并且被发送到第一存储器30(步骤s510)。此后,如参考图9所述,被换出到第一存储器30的全部的存储器管理表备份区域300、交换区域310和标签表区域320可以存储在第二存储器20的安全非易失性数据备份区域200中(步骤s520)。此后,主时间戳124和主标签125被备份在安全数据信息区域400中(步骤s530)。在根据一些示例实施例的半导体系统的操作中,步骤s520和步骤s530的顺序可以互换。

115.参照图12、图13和图19,确定半导体系统是否通电(步骤s600)。如果半导体系统未通电(“否”),则半导体系统不执行附加操作。如果半导体系统通电(“是”),则第一存储器30读取写入安全非易失性数据备份区域200的数据(步骤s610)。此后,使用ram 120的主时间戳124对备份在第一存储器30的时间戳表备份区域330中的加密的时间戳进行解密。此外,将主标签125与解密过程中生成的标签进行比较,从而通过确定它们是否彼此相同来验证安全性(步骤s620)。例如,当将解密过程中生成的标签与主标签125进行比较并且它们彼此相同时,可以确定安全性得到验证。此后,执行从第一存储器30到ram 120的换入(步骤s630)。

116.上述图12至图19中描述的安全数据信息区域400和时间戳表备份区域330不仅可以用于ram 120、安全处理器100、片上系统和/或半导体系统的通电和断电的情况,而且可以在必要时在任何情况下使用。

117.图20至图22是描述根据一些示例实施例的半导体系统的操作的示例流程图。

118.将参考图12、图13和图20示例性地描述当cpu 110执行大于ram 120的大小的软件时半导体系统的操作。

119.首先,确定由cpu 110执行的软件所使用的页是否存在于ram高速缓存区域122中(步骤s700)。在以下描述中,假设由cpu 110执行的软件所使用的页是第一页。

120.更详细地,将要访问的第一页的虚拟地址发送给存储器管理表,并对第一页的与接收到的虚拟地址相对应的物理地址进行访问尝试。如果对应的第一页存在于ram高速缓存区域122(“是”)中,即当第一页可访问时,则不执行换入和换出操作。

121.在这种情况下,例如,当由cpu 110执行的操作是对第一页的写入操作时,可以将关于图2的存储器管理表的第一页page#1的脏度信息设置为脏。

122.在步骤s700中,如果确定第一页不存在于ram高速缓存区域122(“否”)中,则可以确定第一页备份在交换区域310中。也就是说,cpu 110必须将备份在交换区域310中的第一页换入到安全区域s/z(例如,ram高速缓存区域122),以便访问第一页。此时,确定在ram高速缓存区域122中是否存在可以换入第一页的空槽(slot)(步骤s710)。

123.如果确定不存在空槽(“否”),则确定要换入的槽、或页将要被换入的槽的页是否是脏页(步骤s720)。如参考图2所述,可以通过检查存储在存储器管理表121中的每个页的脏度来确定要换入到ram高速缓存区域122的页是否为脏。

124.如果确定要换入到ram高速缓存区域122的槽、或页要被换入的槽的页为脏(“是”),则将存储在时间戳表区域123中的与要换入的页相对应的时间戳递增(步骤s740)。之后,使用通过步骤s740增加的时间戳、密钥和初始向量对要换入的页执行加密并换出(步骤s750)。可以即时执行步骤s750。

125.当通过步骤s740和步骤s750换出要换入的页或者通过步骤s720确定页不为脏(“否”)作为确定结果时,在图2的存储器管理表121中将要换入的页的有效性更新为无效。例如,通过删除指示有效性的“有效”来更新以指示页无效(步骤s730)。

126.此后,如果通过步骤s710确定要换入到ram高速缓存区域122的页是空槽(“是”),或者在通过步骤s740和步骤s750确保要换入到ram高速缓存区域122的页安全之后,换入第一页(步骤s760)。

127.在这种情况下,当通过步骤s720确定要换入的页不为脏时(“否”),则执行更新存储器管理表的步骤s730,不执行步骤s760之后的操作。如果通过步骤s720确定要换入的页不为脏(“否”),则意味着由于第一页被换入ram高速缓存区域122,因此不存在更新,并且这是因为不需要交换操作。

128.此后,如果通过步骤s710确定要换入ram高速缓存区域122的页是空槽(“是”),或者在通过步骤s740和步骤s750确保要换入ram高速缓存区域122的页安全之后,执行步骤s760,然后在步骤s770处,在图2的存储器管理表中将要换入的页的有效性更新为有效。例如,它可以被设置为指示有效性的“有效”。

129.将参考图12、图17和图21描述将在安全区域s/z中使用的软件的数据存储在第二存储器20中的方法的实施例。

130.首先,将ram高速缓存区域122的页中的所有脏页换出到交换区域310(步骤s800)。即,由安全处理器100改变的页或尚未反映在交换区域310中的改变通过换出操作反映在第一存储器30中。

131.此后,ram 120的时间戳表区域123被换出到第一存储器30的时间戳表备份区域330,并且在该过程中,可以使用主时间戳124。

132.具体地,如图14所示,检查安全数据信息区域400的活动设置信息,并检查在安全区域s/z中使用的软件的当前主时间戳(步骤s810)。

133.此后,改变在步骤s810中检查的主时间戳值(步骤s820)。例如,当在步骤s810中检查的主时间戳值是主时间戳a时,将其改变为主时间戳b。

134.此后,时间戳表区域123被加密并备份在时间戳表备份区域330中,并且在加密过程中生成的主标签125被存储在ram 120中(步骤s830)。

135.此后,将第一存储器30中换出的安全非易失性数据写入安全非易失性数据备份区域200中(步骤s840)。

136.此后,主时间戳和主标签信息被写入安全数据信息区域400(步骤s850)。例如,当安全处理器100当前执行的软件的活动设置信息为a时,将步骤s850中的主时间戳和主标签的信息写入用于主时间戳b和主标签b的区域中。这是因为在步骤s820改变了主时间戳。

137.此后,改变活动设置信息(步骤s860)。例如,当安全处理器100当前执行的软件的活动设置信息为a时,将其改变为b。

138.将参考图12、图17和图22描述从第二存储器20读取安全非易失性数据的方法的实施例。

139.首先,第一存储器30从安全非易失性数据备份区域200读取安全非易失性数据(步骤s900)。

140.此后,通过检查安全数据信息400的活动设置信息(步骤s910),获得有效的主时间戳124信息和主标签125,并且使用这些,时间戳表备份区域330被解密(步骤s920)并被存储在ram 120的时间戳表区域123中。

141.此外,通过将在解密过程中生成的标签与主标签125进行比较来验证安全性(步骤s930)。

142.此后,使用在时间戳表区域123中恢复的时间戳,交换区域310的页被解密,并且被换入到ram高速缓存区域122中。此外,可以通过将解密过程中生成的标签与标签表区域320的标签进行比较来验证安全性。

143.尽管上面已经参考附图描述了本公开的实施例,本领域普通技术人员将理解,本公开不限于此,并且可以在不背离其技术思想或基本特征的情况下以许多不同的形式实施。因此,应当理解,本文所阐述的实施例在所有方面仅是示例而非限制性的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1