存储设备及其操作方法与流程

1.本发明涉及一种电子设备,更具体地,本发明涉及一种存储设备及其操作方法。

背景技术:

2.存储设备将从主机接收的逻辑地址转换为物理地址并使用,因此,主机中的逻辑区域和存储设备的物理区域是相互关联的。因此,为了提高电子设备的性能,需要一种能够互补地控制主机和存储设备的新装置或方法。

技术实现要素:

3.(一)要解决的技术问题

4.本发明的实施例提供了一种能够根据每个数据的特性进行有效管理的存储设备及其操作方法。

5.(二)技术方案

6.根据本发明的实施例的存储设备可以包括:存储器装置,包括多个存储器管芯;以及存储器控制器,以超级块为单位控制所述存储器装置,所述超级块包括所述存储器装置中包括的两个以上的存储器块,其中超级块中的一个以上的超级块可以是包括多个小的多管芯区的超级块,所述小的多管芯区包括不同的存储器管芯中包括的每个存储器块的一部分,所述存储器控制器可以响应于从外部主机接收的垃圾收集执行请求选择牺牲超级块,并且所述垃圾收集执行请求可以包括关于所述小的多管芯区中包括的有效页面的信息。

7.根据本发明的操作方法是一种存储设备的操作方法,所述存储设备包括:存储器装置,包括多个存储器管芯;以及存储器控制器,以超级块为单位控制所述存储器装置,所述超级块包括所述存储器装置中包括的两个以上的存储器块,所述存储设备的操作方法可以包括以下步骤:从外部主机接收垃圾收集执行请求;以及基于关于所述垃圾收集执行请求中包括的有效页面的信息从所述超级块中选择牺牲超级块,其中所述超级块中的一个以上的超级块可以是包括多个小的多管芯区的超级块,所述小的多管芯区包括不同的存储器管芯中包括的每个存储器块的一部分。

8.根据本发明的实施例的控制器的操作方法可以包括以下步骤:响应于与信息一起提供的请求,选择牺牲组,所述牺牲组由区域组成,每个区域由部分包括在存储器装置中的每个管芯的每个平面中的每个存储块中的一个以上的页面构成;以及控制存储器装置以对所述牺牲组执行垃圾收集操作,所述牺牲组中的每个区域是处于准备复位(ready to reset)状态的第一区域或处于满(full)状态的第二区域,选择所述牺牲组的步骤可以包括以下步骤:根据每个组中包括的第一区域的数量计算存储器装置中包括第一区域和第二区域的每个组的成本;在包括在相应的一个组中的第二区域中,随着包括在所述信息中的有效页面的数量增加,降低成本;以及根据所述组的成本选择一个牺牲组。

9.(三)有益效果

10.本技术提供了一种能够根据每个数据的特性进行有效管理的存储设备及其操作

方法。

附图说明

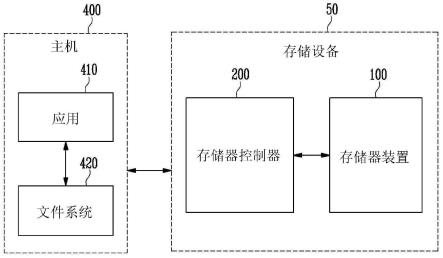

11.图1是用于说明根据本发明的一个实施例的存储设备的图。

12.图2是用于说明图1的存储器装置的图。

13.图3是用于说明图2的存储器单元阵列的图。

14.图4是用于说明根据本发明的一个实施例的存储设备的超级块分配过程的图。

15.图5是用于说明根据本发明的一个实施例的存储设备的超级块管理的图。

16.图6是用于说明由文件系统分配的分区的结构的图。

17.图7是用于说明由文件系统分配第一分区组的新的分区的过程的图。

18.图8和图9是用于说明由文件系统分配第二分区组的新的分区的过程的图。

19.图10是用于说明通过文件系统的第一分区组的复位过程的图。

20.图11是用于说明通过文件系统的第二分区组的复位过程的图。

21.图12是用于说明根据本发明的一个实施例的存储设备中的垃圾收集的图。

22.图13是用于说明根据本发明的一个实施例的选择存储设备的牺牲超级块的过程的流程图。

23.图14是用于说明根据本发明的一个实施例的在存储设备中对牺牲超级块执行垃圾收集的过程的流程图。

24.图15是示出图1的存储器控制器的另一实施例的图。

25.图16是示出应用了根据本发明的实施例的存储设备的存储卡系统的框图。

26.图17是示出应用了根据本发明的实施例的存储设备的固态硬盘(ssd)系统的框图。

27.图18是示出应用了根据本发明的实施例的存储设备的用户系统的框图。

28.附图标记说明

29.50:存储设备

30.100:存储器装置

31.200:存储器控制器

32.400:主机

具体实施方式

33.在本说明书或申请中公开的根据本发明构思的实施例的特定结构或功能说明仅是为了举例说明根据本发明构思的实施例,根据本发明构思的实施例可以以各种形式实施,并且不应被解释为限于在本说明书或申请中说明的实施例。

34.图1是用于说明根据本发明的一个实施例的电子设备的图。

35.参照图1,存储设备(storage device)50可以包括存储器装置(memory device)100和存储器控制器(memory controller)200。存储设备50可以是在主机(host)400的控制下存储数据的装置,例如手机、智能手机、mp3播放器、便携式计算机、台式计算机、游戏机、电视、平板计算机或车载信息娱乐系统(in-vehicle infotainment)。或者,存储设备50可以是在一个地方存储大容量数据的在主机400的控制下存储数据的装置,例如服务器或数

据中心。

36.根据作为与主机400的通信方式的主机接口,存储设备50可以被制造为各种类型的存储设备中的任何一种。例如,存储设备50可以被配置为各种类型的存储设备中的任何一种,例如ssd、mmc、emmc、rs-mmc、micro-mmc形式的多媒体卡(multimedia card);sd、mini-sd、micro-sd形式的安全数字卡(secure digital card);usb(通用串行总线(universal serial bus))存储设备、ufs(通用闪存(universal flash storage))装置、pcmcia(个人计算机存储卡国际协会(personal computer memory card international association))卡形式的存储设备;pci(外围组件互连(peripheral component interconnection))卡形式的存储设备;pci-e(快速的外围组件互连(pci-express))卡形式的存储设备;cf(紧凑型闪存(compact flash))卡;智能媒体卡;记忆棒(memory stick)。

37.存储设备50可以以各种类型的封装(package)形式中的任何一种来制造。例如,存储设备50可以以诸如pop(叠层封装(package on package))、sip(系统级封装(system in package))、soc(片上系统(system on chip))、mcp(多芯片封装(multi-chip package))、cob(板上芯片(chip on board))、wfp(晶圆级制造封装(wafer-level fabricated package))、wsp(晶圆级堆叠封装(wafer-level stack package))的各种类型的封装形式中的任何一种来制造。

38.存储器装置100可以存储数据。存储器装置100响应于存储器控制器200的控制而操作。存储器装置100可以包括存储器单元阵列(未示出),该存储器单元阵列包括用于存储数据的多个存储器单元。

39.每个存储器单元可以被配置为存储一个数据位的单级单元(single level cell,slc)、存储两个数据位的多级单元(multi level cell,mlc)、存储三个数据位的三级单元(triple level cell,tlc)或能够存储四个数据位的四级单元(quad level cell,qlc)。

40.存储器单元阵列(未示出)可以包括多个存储器块。每个存储器块可以包括多个存储器单元。每个存储器块可以包括多个页面。在实施例中,页面可以是用于在存储器装置100中存储数据或读取存储在存储器装置100中的数据的单位。存储器块可以是用于擦除数据的单位。

41.在实施例中,存储器装置100可以是ddr sdram(双倍数据速率同步动态随机存取存储器(double data rate synchronous dynamic random access memory))、lpddr4(低功耗双倍数据速率4(low power double data rate4))sdram、gddr(图形双倍数据速率(graphics double data rate))sdram、lpddr(低功耗ddr(low power ddr))、rdram(存储器总线式动态随机存取存储器(rambus dynamic random access memory))、nand闪存(nand flash memory)、竖直nand闪存(vertical nand)、nor闪存(nor flash memory)、rram(阻变式随机存取存储器(resistive random access memory))、pram(相变ram(phase-change ram))、mram(磁阻式随机存取存储器(magnetoresistive random access memory))、fram(铁电随机存取存储器(ferroelectric random access memory))、stt-ram(自旋转移矩随机存取存储器(spin transfer torque random access memory))等。在本说明书中,为了便于说明,假设存储器装置100是nand闪存。

42.存储器装置100被配置为从存储器控制器200接收命令和地址,并访问存储器单元阵列中的根据地址选择的区域。存储器装置100可以针对根据地址选择的区域执行命令指

示的操作。例如,存储器装置100可以执行写入操作(编程操作)、读取操作和擦除操作。在编程操作时,存储器装置100将数据编程到根据地址选择的区域中。在读取操作时,存储器装置100从根据地址选择的区域读取数据。在擦除操作时,存储器装置100擦除存储在根据地址选择的区域中的数据。

43.存储器控制器200可以控制存储设备50的整体操作。

44.在实施例中,存储器控制器200可以从主机400接收数据和逻辑地址(logical address,la),存储器控制器200可以包括能够将逻辑地址(la)转换为物理地址(pa)的固件(firmware;未示出),该物理地址(pa)指示包括在存储器装置100中的将要存储数据的存储器单元的地址。另外,存储器控制器200可以将构成逻辑地址(la)和物理地址(pa)之间的映射(mapping)关系的逻辑-物理地址映射表存储在缓冲存储器中。

45.存储器控制器200可以根据主机400的请求控制存储器装置100执行编程操作、读取操作或擦除操作等。在编程操作时,存储器控制器200可以向存储器装置100提供编程命令、物理地址和数据。在读取操作时,存储器控制器200可以向存储器装置100提供读取命令和物理地址。在擦除操作时,存储器控制器200可以向存储器装置100提供擦除命令和物理地址。或者,存储器控制器200可以根据主机400的请求打开或关闭存储器装置100中的区(zone)。打开区可以表示为对应于该区的逻辑地址组,例如为对应于由主机分配给数据的分区的逻辑地址创建映射表。关闭区可以表示在再次接收到该区的打开请求之前,不会有将数据存储在该区中的写入请求。主机400可以将这样的打开或关闭区的请求作为单独的请求提供,或者可以与诸如写入请求的其他请求一起提供。

46.在实施例中,存储器控制器200可以与来自主机400的请求无关地自己生成命令、地址和数据,并将生成的命令、地址和数据传送到存储器装置100。例如,存储器控制器200可以向存储器装置100提供用于执行在执行磨损均衡(wear leveling)、读取回收(read reclaim)、垃圾收集(garbage collection)等时所伴随的编程操作、读取操作和擦除操作的命令、地址和数据。

47.在实施例中,存储器控制器200可以包括闪存转换层(flash translation layer)。闪存转换层可以将对应于从主机400接收的请求的逻辑地址(la)转换为物理地址(pa),并将转换后的物理地址(pa)输出到存储器装置100。

48.例如,如上所述,闪存转换层可以将对应于编程请求的逻辑地址(la)转换为物理地址(pa),或者可以将对应于读取请求的逻辑地址(la)转换为物理地址(pa),或者可以将对应于擦除请求的逻辑地址(la)转换为物理地址(pa)。闪存转换层可以将转换后的物理地址(pa)输出到存储器装置100,并且存储器装置100可以对对应于物理地址(pa)的页面或存储器块执行操作。

49.在实施例中,存储器控制器200可以从文件系统(file system)420接收逻辑地址并且将接收的逻辑地址转换为连续的物理地址。当连续的物理地址被输出到存储器装置100时,存储器装置100可以执行对应于连续的物理地址的连续操作。此时,可以根据被分配的区的类型确定连续的物理地址。将参照图4和图5更详细地说明区的类型。

50.在实施例中,存储设备50可以进一步包括缓冲存储器(未示出)。存储器控制器200可以控制主机400和缓冲存储器(未示出)之间的数据交换。或者,存储器控制器200可以将用于控制存储器装置100的系统数据临时存储在缓冲存储器中。例如,存储器控制器200可

以将从主机400输入的数据临时存储在缓冲存储器中,然后将临时存储在缓冲存储器中的数据传送到存储器装置100。

51.在各种实施例中,缓冲存储器可以用作存储器控制器200的操作存储器和高速缓冲存储器。缓冲存储器可以存储由存储器控制器200执行的代码或命令。或者,缓冲存储器可以存储由存储器控制器200处理的数据。

52.在实施例中,缓冲存储器可以被实现为诸如ddr sdram(双倍数据速率同步动态随机存取存储器)、ddr4 sdram、lpddr4(低功耗双倍数据速率4)sdram、gddr(图形双倍数据速率)sdram、lpddr(低功耗ddr)、rdram(存储器总线式动态随机存取存储器)的dram(动态随机存取存储器)或sram(静态随机存取存储器)。

53.在各种实施例中,缓冲存储器可以在存储设备50的外部连接到存储设备50。在这种情况下,在存储设备50的外部连接到存储设备50的易失性存储器装置可以用作缓冲存储器。

54.在实施例中,存储器控制器200可以控制至少两个存储器装置100。在这种情况下,存储器控制器200可以根据交错方式控制存储器装置100以提高操作性能。交错方式可以是控制至少两个存储器装置100的操作重叠的方式。或者,交错方式可以是控制在一个存储器装置100中划分的多个组的操作重叠的方式。此时,组可以是一个以上的存储器管芯(memory die)单位或一个以上的存储器平面(memory plane)单位。

55.主机400可以利用诸如usb(通用串行总线(universal serial bus))、sata(串行高级技术附件(serial at attachment))、sas(串行连接scsi(serial attached scsi))、hsic(高速芯片间(high speed interchip))、scsi(小型计算机系统接口(small computer system interface))、pci(外围组件互连(peripheral component interconnection))、pcie(快速的外围组件互连(pci express))、nvme(非易失性存储器主机控制器接口规范(nonvolatile memory express))、ufs(通用闪存(universal flash storage))、sd(安全数字(secure digital))、mmc(多媒体卡(multimedia card))、emmc(嵌入式多媒体卡(embedded mmc))、dimm(双列直插式存储器模块(dual in-line memory module))、rdimm(带寄存器的双列直插式存储器模块(registered dimm))、lrdimm(低负载双列直插式存储器模块(load reduced dimm))的各种通信方式中的至少一种与存储设备50进行通信。

56.在实施例中,主机400可以包括应用(application)410。应用410也被称为应用程序(application program),并且可以是在操作系统(os)中执行的软件。应用410可以响应于用户输入来处理数据。例如,应用410可以响应于用户输入来处理数据并且将用于将处理后的数据存储在存储设备50的存储器装置100中的请求传送到文件系统420。

57.文件系统420可以响应于从应用传送的请求分配将要存储数据的逻辑地址(la)。在实施例中,文件系统420可以是日志结构文件系统(log structure file system,lfs)。日志结构文件系统(lfs)可以考虑输入数据的属性来生成日志,并且可以基于日志分配与数据对应的分区。此时,分区可以是逻辑地址集合。因此,分配分区可以表示分配与相应数据对应的逻辑地址。被分配分区的数据可以被顺序地存储在对应于分区的存储器装置100的存储区域中。例如,日志结构文件系统(lfs)可以是闪存友好文件系统(flash friendly file system,f2fs)。闪存友好文件系统(f2fs)是考虑到固态硬盘(solid state drive,ssd)的特性而设计的基于日志的文件系统,可以通过使用多头(multi-head)日志来增加

ssd内部的并行度。可以为生成不同日志的数据分配不同的分区。日志结构文件系统(lfs)无法覆盖(overwrite)数据。当修改数据时,日志结构文件系统(lfs)可以重新分配与要修改的数据对应的逻辑地址,并将数据写入对应的物理区域。

58.由应用410请求写入的数据可以存储在主机中的主机存储器(未示出)中,并且可以根据来自应用的请求通过设备接口(未示出)刷新(flush)到存储设备50。主机存储器可以包括诸如dram、sdram、ddr sdram、lpddr sdram、gram的易失性存储器或诸如fram、reram、stt-mram、pram的非易失性存储器。

59.图2是用于说明图1的存储器装置的图。

60.参照图2,存储器装置100可以包括存储器单元阵列110、电压产生部120、地址解码器130、输入/输出电路140和控制逻辑150。

61.存储器单元阵列110包括多个存储器块(blk1~blki)。多个存储器块(blk1~blki)通过行线(rl)连接到地址解码器130。多个存储器块(blk1~blki)可以通过列线(cl)连接到输入/输出电路140。在实施例中,行线(rl)可以包括字线、源极选择线和漏极选择线。在实施例中,列线(cl)可以包括位线。

62.在实施例中,存储器单元阵列110可以包括一个以上的存储器管芯(memory die),并且每个存储器管芯可以包括一个以上的平面(plane),该平面包括一个以上的存储器块。

63.另外,存储器单元阵列110中包括的多个存储器块(blk)可以被分组成两个以上的超级块(super block,sb)。超级块(sb)可以是控制逻辑150管理存储器单元阵列110中包括的多个存储器块(blk)的单位。一个超级块(sb)可以是同时或在同一时间段内执行读取操作和/或写入操作等或结合执行或相关联地执行读取操作和/或写入操作等的存储器块(blk)的集合,或者一个超级块(sb)可以是针对一个命令执行读取操作和/或写入操作等的存储器块(blk)集合,或者一个超级块(sb)可以是在存储器单元阵列110中结合执行或同时执行读取操作和/或写入操作等的存储器块(blk)的集合。此外,多个存储器块(blk)中的在管理或操作方面彼此不同的存储器块(blk)组可以被称为超级块(sb)。两个以上的超级块(sb)中的每一个的大小可以相同。即,两个以上的超级块(sb)中的每一个中包括的存储器块(blk)的数量可以相同。或者,两个以上的超级块(sb)中的至少一个可以具有与其余的超级块(sb)不同的大小。即,多个超级块(sb)中的至少一个超级块(sb)中包括的存储器块(blk)的数量可以与其余的超级块(sb)中包括的存储器块(blk)的数量不同。另外,两个以上的超级块(sb)中的每一个中包括的两个以上的存储器块(blk)可以都位于相同的一个存储器管芯上。与此不同,两个以上的超级块(sb)中的每一个中包括的两个以上的存储器块(blk)可以位于两个以上的不同的存储器管芯上。

64.多个存储器块(blk1~blki)中的每一个包括多个存储器单元。在实施例中,多个存储器单元可以是非易失性存储器单元。在多个存储器单元中,连接到相同字线的存储器单元可以被定义为一个物理页面。即,存储器单元阵列110可以包括多个物理页面。存储器装置100的每个存储器单元可以被配置为存储一个数据位的单级单元(slc)、存储两个数据位的多级单元(mlc)、存储三个数据位的三级单元(tlc)或能够存储四个数据位的四级单元(qlc)。

65.在实施例中,电压产生部120、地址解码器130和输入/输出电路140可以统称为外围电路(peripheral circuit)。外围电路可以在控制逻辑150的控制下驱动存储器单元阵

列110。外围电路可以驱动存储器单元阵列110以执行编程操作、读取操作和擦除操作。

66.电压产生部120被配置为利用供应到存储器装置100的外部电源电压产生多个操作电压。电压产生部120响应于控制逻辑150的控制而操作。

67.在实施例中,电压产生部120可以通过调节外部电源电压来产生内部电源电压。由电压产生部120产生的内部电源电压被用作存储器装置100的操作电压。

68.在实施例中,电压产生部120可以利用外部电源电压或内部电源电压产生多个操作电压。电压产生部120可以被配置为产生存储器装置100所需的各种电压。例如,电压产生部120可以产生多个擦除电压、多个编程电压、多个通过电压、多个选择读取电压和多个非选择读取电压。

69.电压产生部120包括接收内部电源电压的多个泵送电容器以产生具有不同电压电平的多个操作电压,并且电压产生部120可以响应于控制逻辑150的控制来选择性地激活多个泵送电容器以产生多个操作电压。

70.产生的多个操作电压可以通过地址解码器130被供应到存储器单元阵列110。

71.地址解码器130通过行线(rl)连接到存储器单元阵列110。地址解码器130被配置为响应于控制逻辑150的控制而操作。地址解码器130可以从控制逻辑150接收地址(addr)。地址解码器130可以对接收的地址(addr)中的块地址进行解码。地址解码器130根据解码的块地址从存储器块(blk1~blki)中选择至少一个存储器块。地址解码器130可以对接收的地址(addr)中的行地址进行解码。地址解码器130可以根据解码的行地址从选择的存储器块的字线中选择至少一条字线。在实施例中,地址解码器130可以对接收的地址(addr)中的列地址进行解码。地址解码器130可以根据解码的列地址连接输入/输出电路140和存储器单元阵列110。

72.例如,地址解码器130可以包括诸如行解码器、列解码器、地址缓冲器的组件。

73.输入/输出电路140可以包括多个页面缓冲器。多个页面缓冲器可以通过位线连接到存储器单元阵列110。在编程操作时,可以根据存储在多个页面缓冲器中的数据将数据存储在选择的存储器单元中。

74.在读取操作时,可以通过位线感测存储在选择的存储器单元中的数据,并且可以将感测的数据存储在页面缓冲器中。

75.控制逻辑150可以控制地址解码器130、电压产生部120和输入/输出电路140。控制逻辑150可以响应于从外部设备传送的命令(cmd)而操作。控制逻辑150可以响应于命令(cmd)和地址(addr)产生控制信号以控制外围电路。

76.图3是用于说明图2的存储器单元阵列的图。

77.参照图3,存储器单元阵列110可以包括一个以上的存储器管芯,并且每个存储器管芯可以包括一个以上的平面,该平面包括一个以上的存储器块。虽然在图3中示出存储器单元阵列110包括四个存储器管芯(die#0、die#1、die#2、die#3),但是存储器管芯的数量不限于此。多个存储器管芯可以通过多个通道向存储器控制器传送或从存储器控制器接收,并且每个通道可以连接到一个以上的存储器管芯。例如,如果一个通道连接到一个存储器管芯,则一个存储器管芯一次可以接收一个命令,一个存储器管芯中包括的平面可以并行处理由存储器管芯接收的命令。

78.图4是用于说明根据本发明的一个实施例的存储设备的超级块分配过程的图。

79.参照图1和图4,主机400的文件系统420基于数据的属性为应用410请求写入的数据生成日志,并且基于此,对数据进行分类并确定包括要分配给数据的分区的分区组。根据各种标准,数据可以分为被分配第一分区组421a中的第一分区422a的第一类数据和被分配第二分区组421b中的第二分区422b的第二类数据。由文件系统分配第一分区组421a中的第一分区422a的数据可以在存储器控制器200的控制下存储在存储器装置100的第一超级块111a中的小的单管芯区(small single-die zone)112a中,并且由文件系统分配第二分区组421b中的第二分区422b的数据可以存储在存储器装置100的第二超级块111b中的小的多管芯区(small multi-die zone)112b中。第一分区组421a对应于第一超级块111a,因此,第一分区422a对应于小的单管芯区112a。可以与分区组中的分区顺序无关地被分配为新的分区的第一分区422a的特性符合以每个存储器管芯管理的小的单管芯区112a的特性,并且第一分区422a和小的单管芯区112a具有相同的特性,即第一分区422a和小的单管芯区112a都能够以一个分区或区为单位执行复位或擦除操作。另外,根据分区组中的分区顺序被分配为新的分区的第二分区422b的特性符合跨多个存储器管芯形成的小的多管芯区112b的特性,并且第二分区422b和小的多管芯区112b具有相同的特性,即第二分区422b和小的多管芯区112b都不能以一个分区或区为单位执行复位或擦除操作,在其各自所属的第二分区组421b和第二超级块111b都处于能够复位或擦除的状态之后以分区组和超级块为单位执行复位或擦除操作。将参照图6至图11更详细地说明第一分区422a和第二分区422b的分配和复位,并且将参照图5更详细地说明小的单管芯区112a和小的多管芯区112b的形态。

80.可以与分区顺序无关地分配第一分区组421a中的第一分区422a,并且可以响应于来自主机400的将要存储被分配分区的数据的区分配请求,存储器控制器200可以分配形成为一个存储器管芯中的区域的小的单管芯区112a。可以根据分区顺序分配第二分区组422b中的第二分区422b,并且可以响应于来自主机400的将要存储被分配分区的数据的区分配请求,存储器控制器200可以分配形成为包括多个存储器管芯中的存储器块的一部分的区域的小的多管芯区112b。针对主机400的区分配请求,当存储器控制器200回复当前使用的超级块中不存在额外的可被分配的区的信息时,文件系统420可以在分配新的分区组之后分配新的分区组中的分区,作为响应,存储器控制器200可以在分配新的超级块和包括在其中的新的区之后存储被分配新的分区的数据。或者,文件系统420不从存储器控制器200接收关于超级块和区的信息,可以自行分配新的分区组和包括在其中的分区。

81.图5是用于说明根据本发明的一个实施例的存储设备的超级块管理的图。

82.参照图1、图4和图5,存储器单元阵列110可以包括多个存储器管芯,例如,可以包括四个存储器管芯(die#0~die#3)。另外,每个存储器管芯可以包括多个平面,每个平面包括多个存储器块,例如,可以包括四个平面plane#0~plane#3。存储器控制器200可以通过将存储器装置100的存储器单元阵列110划分为多个超级块来控制存储器单元阵列110。超级块可以包括存储器单元阵列110中包括的两个以上的存储器块。超级块可以包括多个区(zone)。可以跨多个存储器管芯形成超级块,并且如图5所示,可以跨所有存储器管芯形成超级块。超级块可以根据包括在其中的区的形态分为第一超级块111a和第二超级块111b。在根据本发明的一个实施例的存储设备中,作为存储器控制器200控制存储器装置100的单位的超级块可以仅由包括小的多管芯区112b的第二超级块111b组成,或者可以包括包括小的多管芯区112b的第二超级块111b和包括小的单管芯区112a的第一超级块111a。

83.第一超级块111a中包括的小的单管芯区112a可以包括一个存储器管芯中的一个以上的块。例如,如图5所示,对于每个存储器管芯,包括平面0至平面3中包括的一个存储器块的区域可以被指定为一个区(zone),因此,第一超级块111a可以包括四个小的单管芯区112a,每个存储器管芯形成一个小的单管芯区112a。

84.第二超级块111b中包括的小的多管芯区112b可以包括不同的存储器管芯中包括的每个块的一部分。例如,如图5所示,小的多管芯区112b可以跨所有四个存储器管芯(die#0~die#3)形成,并且可以仅包括每个平面中包括的每个存储器块的一部分。例如,如图5所示,可以仅包括每个平面中包括的每个存储器块的页面中的1/4页面。因此,第二超级块111b可以跨所有存储器管芯形成,并且可以包括形成为仅包括每个存储器块的一部分页面的四个小的多管芯区112b。

85.在一个实施例中,第一超级块111a和第二超级块111b的大小可以相同。即,第一超级块111a和第二超级块111b可以包括相同数量的存储器块。另外,小的单管芯区112a和小的多管芯区112b的大小可以相同。即,小的单管芯区112a和小的多管芯区112b中包括的页面数量可以相同。小的单管芯区112a可以形成在一个存储器管芯中,而小的多管芯区112b可以跨多个存储器管芯形成。因此,在小的多管芯区112b的情况下,可以以管芯交错方式操作,特别地,如图5所示,当小的多管芯区112b跨所有存储器管芯形成时,可以以全管芯(full-die)交错方式操作。然而,不能同时分配和编程不同的小的多管芯区112b。另外,由于小的多管芯区仅包括每个存储器块的一部分,因此当要擦除特定的区时无法立即擦除,当可以擦除部分包括在该区中的每个存储器块的所有页面时,即,当可以擦除包括该区的超级块的所有区时,可以擦除该区。因此,在小的多管芯区的情况下,虽然具有可以以存储器管芯为单位以交错方式操作的优点,但考虑到编程和擦除时的限制,可能不适合存储输入/输出频率高的数据。因此,通过同时使用第一超级块和第二超级块,可以在第一超级块的小的单管芯区中存储容量相对较小或输入/输出频率高的数据,并且可以在第二超级块的小的多管芯区中存储容量相对较大或输入/输出频率低的数据,从而可以提高存储设备的性能。

86.表示超级块中包括的物理区域的区(zone),例如小的单管芯区或小的多管芯区可以被划分为满(full)状态、空(empty)状态和激活(active)状态。满状态可以表示数据存储在区(zone)中的所有区域中而区中不存在空区域的状态。空状态可以表示没有数据存储在区中的区域中而区为空的状态。激活状态可以表示数据仅存储在区中的一部分区域中的状态,并且可以是打开(open)状态或关闭(close)状态。打开状态可以表示在数据仅存储在区中的一部分区域的区中当前数据正在被编程的区,关闭状态可以表示在数据仅存储在区中的一部分区域的区中当前数据没有正在被编程的区域。

87.另外,在小的多管芯区的情况下,可以进一步具有准备复位(ready to reset)状态。区的复位操作可以表示通过擦除区来使该区变成空状态的操作。擦除可以以存储器块为单位执行,如图5所示,在小的多管芯区112b的情况下,仅包括多个存储器块中的每一个的一部分。另一方面,在小的单管芯区112a的情况下,可以包括一个以上的整个存储器块。因此,当要复位特定的小的单管芯区112a时,可以立即擦除该区。另一方面,当要复位特定的小的多管芯区112b时,当可以擦除部分包括在该区中的每个存储器块的所有页面时,即,当可以擦除包括该区的超级块的所有区时,可以擦除该区。因此,当对小的多管芯区112b执

行复位操作时,该区不会被立即擦除,而是转换为准备复位状态,当包括小的多管芯区112b的第二超级块111b中的所有小的多管芯区112b转换为准备复位状态时,该超级块中的所有小的多管芯区112b可以被一次性擦除以转换为空状态。

88.图6是用于说明由文件系统分配的分区的结构的图。

89.参照图6,分区可以包括多个逻辑地址。一个分区中包括的逻辑地址可以是连续地址或非连续地址。为数据分配分区可以表示分配了分区中的逻辑地址。关于每个分区中包括的地址的信息可以包括在主机中的存储器或存储设备中的存储器中。可以根据请求写入的数据的大小顺序地分配逻辑地址。例如,当有特定大小的数据d1和d2的写入请求并且图5的分区被分配给数据d1和d2时,la1至la3的逻辑地址可以被分配给d1,la4和la5的逻辑地址可以被分配给d2。

90.图7是用于说明由文件系统分配第一分区组的新的分区的过程的图。

91.参照图7,可以与分区组中的分区顺序无关地分配新的分区的分区组可以被定义为第一分区组421a。此时,包括在分区组中的分区中的逻辑地址可以彼此连续,并且随着分区组中的分区号增加,逻辑地址可以增加。因此,分区顺序可以表示分区组中的分区号顺序,这可以表示逻辑地址增加的方向上的顺序。或者,包括在分区组中的分区中的逻辑地址可以彼此不连续。在这种情况下,可以基于存储在单独的存储器中的分区和关于包括在每个分区组中的逻辑地址的信息来确定分区顺序。在第一分区组421a的情况下,由于可以与分区顺序无关地分配分区并分配逻辑地址,因此第三分区(分区#3)可以先被分配并且第三分区中的所有逻辑地址被分配,从而可以在变成满分区(full section)之后分配第一分区(分区#1)并且可以分配新的数据的逻辑地址。当作为打开分区(open section)的第一分区的所有逻辑地址被分配给数据并且第一分区变成满分区时,文件系统420可以分配作为空分区(empty section)的第零分区(分区#0)和第二分区中的任何一个作为新的分区,并且可以将包括在其中的逻辑地址分配给数据。

92.图8和图9是用于说明由文件系统分配第二分区组的新的分区的过程的图。

93.参照图8和图9,可以根据分区组中的分区顺序分配新的分区的分区组可以被定义为第二分区组421b。如图8所示,在第二分区组中,第零分区(分区#0)可以最先被打开并将包括在其中的逻辑地址分配给数据,当第零分区变成满分区时,可以分配作为下一个顺序的分区的第一分区(分区#1)作为新的分区以存储数据。如图9所示,当第二分区组421b中的所有分区都是满分区时,文件系统420可以在分配新的第二分区组421b之后,分配作为新的第二分区组中的第一个分区的第零分区(分区#0)作为新的分区,并且可以将包括在其中的逻辑地址分配给数据。此时,在第二分区组421b的情况下,可以根据分区组中的分区顺序分配分区,当作为最后一个分区的第三分区(分区#3)是满分区时,在其之前的分区中不可能存在空分区。因此,在第二分区组421b的情况下,无需在分区组中寻找空分区,如果第二分区组421b中不存在下一个顺序的分区,则文件系统420分配新的第二分区组421b。

94.图10是用于说明通过文件系统的第一分区组的复位过程的图。

95.参照图10,在第一分区组421a中,1)当第零分区(分区#0)被复位时,2)通过丢弃(discard)与第零分区中的逻辑地址对应的所有数据,第零分区变成空(empty)分区,从而完成复位操作。另外,3)复位当第一分区(分区#1)时,4)通过丢弃与第一分区中的逻辑地址对应的所有数据,第一分区变成空分区,从而完成复位操作。另外,5)当第二分区(分区#2)

被复位时,6)通过丢弃与第二分区中的逻辑地址对应的所有数据,第二分区变成空分区,从而完成复位操作。即,当对第一分区组421a中包括的一个分区执行复位操作时,作为响应,与该分区中的逻辑地址对应的数据被丢弃,从而该分区可以立即变成空分区,因此,可以完成复位操作。此时,在对分区执行复位操作时丢弃与逻辑地址对应的数据可以表示解除逻辑地址和数据之间的映射关系。当与特定的分区中的逻辑地址对应的数据全部无效时执行复位操作,如果存在有效数据,则将其映射到另一分区的逻辑地址,并且可以在将与相应逻辑地址对应的数据处理为无效后执行复位操作。完成复位的分区中包括的逻辑地址可以重新被分配给新数据。这样的复位操作可以由文件系统执行。

96.图11是用于说明通过文件系统的第二分区组的复位过程的图。

97.参照图5和图11,在第二分区组421b中,1)当第零分区(分区#0)被复位时,2)与第零分区中的逻辑地址对应的数据不会被立即丢弃,并且指示第零分区准备复位的信息存储在位图中。另外,3)当第一分区(分区#1)被复位时,4)与第一分区中的逻辑地址对应的数据不会被立即丢弃,并且指示第一分区准备复位的信息存储在位图中。另外,5)当第二分区(分区#2)被复位时,6)与第二分区中的逻辑地址对应的数据不会被立即丢弃,并且指示第二分区准备复位的信息存储在位图中。另外,7)当第三分区(分区#3)被复位时,8)与第三分区中的逻辑地址对应的数据不会被立即丢弃,并且指示第三分区准备复位的信息存储在位图中。9)因此,当指示第二分区组421b的所有分区准备复位的信息存储在位图中时,与所有所述分区中的所有逻辑地址对应的所有数据都被丢弃,并且第二分区组421b中的所有分区一次性地变成空分区,从而可以完成复位操作。即,在第二分区组421b的情况下,当仅一部分分区被复位时,数据不会被立即丢弃,因此分区不会变成空分区,在对第二分区组421b中的所有分区执行复位操作之后,即在存储了指示所有分区准备复位的信息之后,与包括在第二分区组421b中的所有分区的逻辑地址对应的数据被丢弃,从而第二分区组421b中的所有分区可以同时变成空分区。当复位操作完成时,指示第二分区组421b中的所有分区准备复位的信息可以被删除。此时,存储指示准备复位的信息的位图可以包括在存储设备中的任意位置中。此时,在分区的复位操作中丢弃与逻辑地址对应的数据可以表示解除逻辑地址和数据之间的映射关系。当与特定的分区中的逻辑地址对应的数据全部无效(invalid)时,执行复位操作,如果存在有效数据,则将其映射到另一分区的逻辑地址,并且在与该逻辑地址对应的数据被处理为无效后,可以执行复位操作。完成复位的分区中包括的逻辑地址可以重新分配给新的数据。这样的复位操作可以由文件系统执行。即,这样的第二分区的复位操作对应于图5的第二超级块111b中的小的多管芯区112b的复位操作。即,当对第二分区422b执行复位操作时,第二分区处于准备复位状态,因此,对应于第二分区422b的小的多管芯区112b不会被立即擦除,而是被转换为准备复位状态。随后,当包括第二分区422b的第二分区组421b中的所有第二分区422b都被转换为准备复位状态时,即,当包括小的多管芯区112b的第二超级块111b中的所有小的多管芯区112b被转换为准备复位状态时,与第二分区组421b中的所有第二分区422b的逻辑地址对应的数据被丢弃,从而第二分区组421b中的所有分区同时变成空分区,对应的第二超级块111b中的所有小的多管芯区112b被擦除并变成空状态。

98.图12是用于说明根据本发明的一个实施例的存储设备的垃圾收集的图。

99.参照图1、图4和图12,主机400包括主机垃圾收集控制部430。主机垃圾收集控制部

430可以包括在文件系统420中,或者可以作为与文件系统420分开的配置包括在主机400中。主机垃圾收集控制部430可以包括关于由文件系统420分配的分区和分区组的信息以及关于对应的超级块和区(zone)的信息。另外,主机垃圾收集控制部430可以包括关于区中包括的每个页面的信息。例如,可以包括关于存储在每个页面中的数据的有效(valid)或无效(invalid)的信息。

100.主机垃圾收集控制部430可以向存储设备50提供垃圾收集执行请求。垃圾收集执行请求可以包括关于区中包括的每个页面的信息,在实施例中,垃圾收集执行请求可以包括关于小的多管芯区中包括的有效页面的信息。更详细地,垃圾收集执行请求可以包括关于处于满状态的小的多管芯区中包括的有效页面的信息,例如,垃圾收集执行请求可以包括处于满状态的小的多管芯区中包括的有效页面的数量、包括预定数量以上的有效页面的小的多管芯区的列表等。

101.存储设备50中的存储器控制器200可以包括区管理部210和设备垃圾收集控制部220。区管理部210可以分配和管理对应于由主机分配的分区和分区组的区和超级块。对应于第一分区组421a中的第一分区422a,可以分配和映射第一超级块111a中的小的单管芯区112a,对应于第二分区组421b中的第二分区422b,可以分配和映射第二超级块111b中的小的多管芯区112b。设备垃圾收集控制部220可以响应于存储设备50从主机400接收的垃圾收集执行请求来执行垃圾收集。设备垃圾收集控制部220可以从区管理部210接收关于分配的超级块和区的信息,并且基于接收的信息选择牺牲超级块。牺牲超级块可以从包括小的多管芯区112b的第二超级块111b中选择。设备垃圾收集控制部220可以从仅由处于满状态和准备复位状态的区组成的超级块中选择牺牲超级块。设备垃圾收集控制部220可以考虑处于准备复位状态的区的数量来选择牺牲超级块。可以从区管理部210或主机垃圾收集控制部430接收关于处于准备复位状态的区的数量的信息。例如,越是准备复位状态的区的数量多的超级块,被选为牺牲超级块的可能性会越高。另外,设备垃圾收集控制部220可以考虑关于处于满状态的区中包括的有效页面的信息来选择牺牲超级块。可以从主机垃圾收集控制部430接收关于处于满状态的区中包括的有效页面的信息,这样的信息可以与垃圾收集执行请求一起被接收。例如,处于满状态的区中包括的有效页面的数量越多,被选为牺牲超级块的可能性会越高。区管理部210可以不管理关于区中包括的页面是有效还是无效的信息,因此,可以从主机垃圾收集控制部430接收与其相关的信息。当设备垃圾收集控制部220选择牺牲超级块时,区管理部210可以复制存储在牺牲超级块中的处于满状态的区中的数据并将其存储在另一个超级块中。当牺牲超级块是包括小的多管芯区112b的第二超级块111b时,复制并存储牺牲超级块中的处于满状态的区的数据的另一超级块也可以是第二超级块111b。另外,此时,区管理单元210可以不管理关于区中包括的页面是有效还是无效的信息,因此可以以区为单位复制和存储数据。或者,可以基于从主机垃圾收集控制部430接收的关于有效页面的信息以页面为单位复制和存储数据。即,可以仅复制存储在牺牲超级块中的处于满状态的区中的有效页面中的数据并将其存储在另一个超级块中。

102.图13是用于说明根据本发明的一个实施例的选择存储设备的牺牲超级块的过程的流程图。

103.参照图12和图13,在步骤s1301中,存储设备50可以从主机400接收垃圾收集执行请求。作为响应,在步骤s1303中,存储器控制器200可以选择候选超级块。候选超级块可以

是包括多个小的多管芯区的超级块。在实施例中,可以选择仅由处于满状态和准备复位状态的小的多管芯区组成的超级块作为候选超级块。

104.在步骤s1305中,可以计算每个候选超级块的垃圾收集成本。此时,可以考虑超级块中的处于准备复位状态的小的多管芯区的数量来计算垃圾收集成本。

105.在步骤s1307中,可以基于每个候选超级块中包括的处于满状态的小的多管芯区中包括的有效页面的数量来修改每个候选超级块的成本。例如,处于满状态的小的多管芯区中包括的有效页面的数量越多,赋予权重以降低成本,从而可以增加被选为牺牲超级块的可能性。此时,关于有效页面的数量的信息可以包括在垃圾收集执行请求中。例如,关于有效页面的信息可以包括处于满状态的小的多管芯区中包括的有效页面的数量和包括预定数量以上的有效页面的小的多管芯区的列表。首先,确认候选超级块中包括的区是否在包括预定数量以上的有效页面的小的多管芯区的列表中,如果在该列表中,则可以通过基于有效页面的数量赋予权重来降低候选超级块的成本。

106.在步骤s1309中,可以比较在步骤s1307中修改并确定的每个候选超级块的成本。因此,在步骤s1311中可以选择具有最低成本的候选超级块作为牺牲超级块。

107.图14是用于说明根据本发明的一个实施例的对牺牲超级块执行垃圾收集的过程的流程图。

108.参照图13和图14,在步骤s1401中可以复制存储在通过根据图13的过程选择的牺牲超级块中的处于满状态的区中的数据并将其存储在另一超级块中。当牺牲超级块是包括小的多管芯区的第二超级块时,数据移动的另一超级块也可以是第二超级块。此时,可以以区为单位或以页面为单位复制数据。

109.在步骤s1403中,可以对数据移动完成的超级块执行擦除。因此,牺牲者超级块中包括的所有区都可以转换为空状态。

110.图15是示出图1的存储器控制器的另一实施例的图。

111.参照图15,存储器控制器1000可以包括处理器1010、内部存储器1020、纠错码电路1030、主机接口1040、缓冲存储器接口1050和存储器接口1060。

112.处理器1010可以执行用于控制存储器装置100的各种运算或者可以生成各种命令。当处理器1010从主机400接收到请求时,处理器1010可以根据接收的请求生成命令并将生成的命令传送到队列控制器(未示出)。另外,处理器1010可以响应于来自主机400的区分配请求,分配将要存储从主机接收的数据的存储器装置中的超级块和包括在其中的区,并且可以管理分配的超级块和区。另外,处理器1010可以响应于来自主机400的垃圾收集执行请求来执行垃圾收集。

113.内部存储器1020可以存储存储器控制器1000的操作所需的各种信息。例如,内部存储器1020可以包括逻辑和物理地址映射表。内部存储器1020可以被配置为ram(随机存取存储器)、动态ram(dram)、静态ram(sram)、高速缓存(cache)和紧耦合存储器(tightly coupled memory,tcm)中的至少一种。

114.纠错码电路1030被配置为利用纠错码(ecc)检测并纠正从存储器装置100接收的数据中的错误。处理器1010可以控制存储器装置100以根据纠错码电路1030的错误检测结果调整读取电压并执行重新读取。在示例性实施例中,可以提供纠错块作为存储器控制器1000的组件。

115.主机接口1040可以在存储器控制器1000和主机400之间交换命令、地址和数据等。例如,主机接口1040可以从主机400接收请求、地址、数据等,并且可以将从存储器装置100读取的数据输出到主机400。主机接口1040可以使用诸如usb(通用串行总线(universal serial bus))、sata(串行高级技术附件(serial at attachment))、sas(串行连接scsi(serial attached scsi))、hsic(高速芯片间(high speed interchip))、scsi(小型计算机系统接口(small computer system interface))、pci(外围组件互连(peripheral component interconnection))、pcie(快速的外围组件互连(pci express))、nvme(非易失性存储器主机控制器接口规范(nonvolatile memory express))、ufs(通用闪存(universal flash storage))、sd(安全数字(secure digital))、mmc(多媒体卡(multimedia card))、emmc(嵌入式多媒体卡(embedded mmc))、dimm(双列直插式存储器模块(dual in-line memory module))、rdimm(带寄存器的双列直插式存储器模块(registered dimm))、lrdimm(低负载双列直插式存储器模块(load reduced dimm))、esdi(增强型小型磁盘机接口(enhanced small disk interface))或ide(电子集成驱动器(integrated drive electronics))的协议来与主机400进行通信。主机接口1040可以接收分配对应于由主机400分配给数据的分区的区的请求。主机接口1040可以从主机400接收执行垃圾收集的请求,此时,可以一起接收关于存储器装置100的小的多管芯区中包括的有效页面的信息。

116.缓冲存储器接口1050可以在处理器1010和缓冲存储器之间传送数据。缓冲存储器可以用作存储器控制器1000的操作存储器或高速缓冲存储器,并且可以存储在存储设备50中使用的数据。通过处理器1010,缓冲存储器接口1050可以将缓冲存储器用作读取缓冲器、写入缓冲器、映射缓冲器等。根据实施例,缓冲存储器可以包括ddr sdram(双倍数据速率同步动态随机存取存储器)、ddr4 sdram、lpddr4(低功耗双倍数据速率4)sdram、gddr(图形双倍数据速率)sdram、lpddr(低功耗ddr)或rdram(存储器总线式动态随机存取存储器)。当缓冲存储器包括在存储器控制器1000内部时,可以省略缓冲存储器接口1050。

117.存储器接口1060可以在存储器控制器1000和存储器装置100之间交换命令、地址和数据。例如,存储器接口1060可以通过通道(channel)将命令、地址、数据等传送到存储器装置100,并且可以从存储器装置100接收数据等。存储器接口1060可以基于由处理器1010分配和管理的超级块和区向存储器装置100传送命令、地址和数据或从存储器装置100接收命令、地址和数据等。另外,当执行垃圾收集时,被选为牺牲超级块的超级块中的一部分数据可以被移动到另一超级块,并且可以对牺牲超级块执行擦除操作。

118.图16是示出应用了根据本发明的实施例的存储设备的存储卡系统的框图。

119.参照图16,存储卡系统2000包括存储器控制器2100、存储器装置2200和连接器2300。

120.存储器控制器2100连接到存储器装置2200。存储器控制器2100被配置为访问存储器装置2200。例如,存储器控制器2100可以被配置为控制存储器装置2200的读取、编程、擦除和后台(background)操作。存储器控制器2100被配置为提供存储器装置2200和主机之间的接口。存储器控制器2100被配置为驱动用于控制存储器装置2200的固件(firmware)。存储器控制器2100可以以与参照图1描述的存储器控制器200相同的方式实现。例如,存储器控制器2100可以在存储器装置2200中分配区和包括该区的超级块,并可以以区域和超级块

为单位控制存储器装置2200。

121.例如,存储器控制器2100可以包括诸如ram(随机存取存储器)、处理单元、主机接口、存储器接口、纠错部的组件。

122.存储器控制器2100可以通过连接器2300与外部设备进行通信。存储器控制器2100可以根据特定的通信标准与外部设备(例如,主机)进行通信。例如,存储器控制器2100可以被配置为通过诸如usb(通用串行总线(universal serial bus))、mmc(多媒体卡(multimedia card))、emmc(嵌入式多媒体卡(embedded mmc))、pci(外围组件互连(peripheral component interconnection))、pci-e(快速的外围组件互连(pci express))、ata(高级技术附件(advanced technology attachment))、serial-ata(串行ata)、parallel-ata(并行ata)、scsi(小型计算机系统接口(small computer system interface))、esdi(增强型小型磁盘机接口(enhanced small disk interface))、ide(电子集成驱动器(integrated drive electronics))、firewire(火线)、ufs(通用闪存(universal flash storage))、wifi、蓝牙(bluetooth)、nvme的各种通信标准中的至少一种与外部设备进行通信。例如,连接器2300可以由上述各种通信标准中的至少一种来定义。

123.例如,存储器装置2200可以被配置为诸如eeprom(电可擦除可编程rom(electrically erasable and programmable rom))、nand闪存、nor闪存、pram(相变ram(phase-change ram))、reram(电阻ram(resistive ram))、fram(铁电ram(ferroelectric ram))、stt-mram(自旋转移矩ram(spin transfer torque magnetic ram))的各种非易失性存储设备。

124.存储器控制器2100和存储器装置2200可以集成到一个半导体器件中以构成存储卡。例如,存储器控制器2100和存储器装置2200可以集成到一个半导体器件中以构成诸如pc卡(个人计算机存储卡国际协会(personal computer memory card international association,pcmcia))、cf卡、智能媒体卡(sm、smc)、记忆棒、多媒体卡(mmc、rs-mmc、mmcmicro、emmc)、sd卡(sd、minisd、microsd、sdhc)、通用闪存(ufs)的存储卡。

125.图17是示出应用了根据本发明的实施例的存储设备的固态硬盘(solid state drive,ssd)系统的框图。

126.参照图17,ssd系统3000包括主机3100和ssd 3200。ssd 3200通过信号连接器3001向主机3100传送信号和从主机3100接收信号,并且通过电源连接器3002接收电力。ssd 3200包括ssd控制器3210、多个闪存3221~322n、辅助电源装置3230和缓冲存储器3240。

127.根据本发明的实施例,ssd控制器3210可以执行参照图1说明的存储器控制器200的功能。

128.ssd控制器3210可以响应于从主机3100接收的信号来控制多个闪存3221~322n。ssd控制器3210可以通过多个通道ch1~chn控制多个闪存。一个以上的存储器管芯可以连接到每个通道。例如,信号可以是基于主机3100和ssd 3200的接口的信号。例如,信号可以是由诸如usb(通用串行总线(universal serial bus))、mmc(多媒体卡(multimedia card))、emmc(嵌入式多媒体卡(embedded mmc))、pci(外围组件互连(peripheral component interconnection))、pci-e(快速的外围组件互连(pci express))、ata(高级技术附件(advanced technology attachment))、serial-ata(串行ata)、parallel-ata(并行ata)、scsi(小型计算机系统接口(small computer system interface))、esdi(增强型小

型磁盘机接口(enhanced small disk interface))、ide(电子集成驱动器(integrated drive electronics))、firewire(火线)、ufs(通用闪存(universal flash storage))、wifi、蓝牙(bluetooth)、nvme的接口中的至少一种定义的信号。ssd控制器3210可以根据从主机3100接收的垃圾收集执行请求来执行垃圾收集。

129.辅助电源装置3230通过电源连接器3002连接到主机3100。辅助电源装置3230可以从主机3100接收电力并进行充电。当来自主机3100的电力供应不顺畅时,辅助电源装置3230可以向ssd 3200供应电力。例如,辅助电源装置3230可以位于ssd 3200内或可以位于ssd 3200外部。例如,辅助电源装置3230可以位于主板上以向ssd3200供应辅助电力。

130.缓冲存储器3240作为ssd 3200的缓冲存储器操作。例如,缓冲存储器3240可以临时存储从主机3100接收的数据或从多个闪存3221~322n接收的数据,或者缓冲存储器3240可以临时存储闪存3221~322n的元数据(例如,映射表)。缓冲存储器3240可以包括诸如dram、sdram、ddr sdram、lpddr sdram和gram的易失性存储器或诸如fram、reram、stt-mram、pram的非易失性存储器。

131.图18是示出应用了根据本发明的实施例的存储设备的用户系统的框图。

132.参照图18,用户系统4000包括应用处理器(application processor)4100、存储器模块(memory module)4200、网络模块(network module)4300、存储模块(storage module)4400和用户界面(user interface)4500。

133.应用处理器4100可以驱动包括在用户系统4000中的组件、操作系统(os)、用户程序或文件系统等。例如,应用处理器4100可以包括控制包括在用户系统4000中的组件的控制器、接口和图形引擎等。应用处理器4100可以被提供为片上系统(soc)。应用处理器4100可以为用户请求写入的数据生成日志,基于该日志分配分区组和分区,并且将分区被分配到的数据提供给存储模块4400。

134.存储器模块4200可以作为用户系统4000的主存储器、操作存储器、缓冲存储器或高速缓冲存储器来操作。存储器模块4200可以包括诸如dram、sdram、ddr sdram、ddr2 sdram、ddr3sdram、lpddr sdarm、lpddr2 sdram、lpddr3 sdram的易失性随机存取存储器或诸如pram、reram、mram、fram的非易失性随机存取存储器。例如,应用处理器4100和存储器模块4200可以基于pop(叠层封装(package on package))封装并且可以被提供为单个半导体封装。

135.网络模块4300可以与外部设备进行通信。例如,网络模块4300可以支持诸如cdma(码分多址(code division multiple access))、gsm(全球移动通信系统(global system for mobile communication))、wcdma(宽带cdma(wideband cdma))、cdma-2000、tdma(时分多址(time division multiple access))、lte(长期演进(long term evolution))、wimax、wlan、uwb、蓝牙、wi-fi的无线通信。例如,网络模块4300可以包括在应用处理器4100中。

136.存储模块4400可以存储数据。例如,存储模块4400可以存储从应用处理器4100接收的数据。或者,存储模块4400可以将存储在存储模块4400中的数据传送到应用处理器4100。例如,存储模块4400可以实现为诸如pram(相变ram(phase-change ram))、mram(磁性ram(magnetic ram))、rram(电阻ram(resistive ram))、nand闪存、nor闪存、三维结构的nand闪存的非易失性半导体存储器器件。例如,存储模块4400可以被提供为诸如用户系统

4000的存储卡或外部驱动器的可移动驱动器(removable drive)。

137.例如,存储模块4400可以包括多个非易失性存储器装置,并且多个非易失性存储器装置可以以与参照图1说明的存储器装置100相同的方式操作。存储模块4400可以以与参照图1说明的存储设备50相同的方式操作。

138.用户界面4500可以包括用于将数据或命令输入到应用处理器4100或者将数据输出到外部设备的界面。例如,用户界面4500可以包括诸如键盘、小键盘、按钮、触摸面板、触摸屏、触摸板、触摸球、摄像头、麦克风、陀螺仪传感器、振动传感器、压电元件的用户输入界面。用户界面4500可以包括诸如lcd(液晶显示器(liquid crystal display))、oled(有机发光二极管(organic light emitting diode))显示器、amoled(有源矩阵oled(active matrix oled))显示器、led、扬声器和监视器的用户输出界面。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1