一种内存通信方法、系统、设备及介质与流程

1.本发明属于计算机领域,具体涉及一种内存通信方法、系统、设备及介质。

背景技术:

2.目前,数字经济概念的提出推动了大数据产业的快速发展,服务器行业竞争日益激烈,各大厂商对服务器的性能要求越来越高。

3.随着处理器性能的快速提升,服务器需要大量的内存来临时保存cpu(central processing unit,中央处理器central processing unit,中央处理器)上需要读取的数据。内存作为服务器上的重要部件,其可靠性和稳定性直接关系到服务器的可靠性和稳定性。基于内存制定的spd(serial presence detect,串行存在检测,本发明指cpu与内存之间通信的链路)协议定义了内存的特性,在bios开机自检的post(power on self test,上电自检)过程中cpu内部的内存控制器会读取内存的spd寄存器,进行内存初始化及训练;post完成后cpu会通过spd总线轮询内存温度,以实现内存温度监控及降频保护机制。而在实际的服务器的使用中由于主板电路上的链路串阻等一些原因导致在bios开机自检的post过程中出现异常卡死的情况,而这种情况只能通过调试记录日志的方式进行发现,但由于通常的使用很少接入调试接口获取日开机自检的日志,导致在一些情况下服务器卡死时运维人员无法发现卡死原因等一些问题。并且在内存spd信息出错时也无法补救只能重启服务器,很大程度上影响了服务器的运维效率。

4.因此spd链路通信的稳定性直接影响内存识别及异常监控,其链路通信稳定性尤为重要。

技术实现要素:

5.为解决以上问题,本发明提出一种内存通信方法,包括:

6.通过第一控制器的第一接口与cpu的内存通信接口相连,以及通过所述第一控制器的第二接口与内存模块的内存通信接口相连;

7.将所述第一接口和所述第二接口对应的电位变化进行同步或异步,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控。

8.在本发明的一些实施方式中,将所述第一接口和所述第二接口对应的电位变化进行同步或异步包括:

9.根据所述cpu和所述内存模块的内存通信接口的电压规范调整所述第一接口和所述第二接口的电压。

10.在本发明的一些实施方式中,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控包括:

11.根据内存通信通信协议对所述第一接口和/或所述第二接口的数据进行解析,并将解析结果保存到所述第一控制器的第一区域同时将所述解析结果发送到第二控制器上。

12.在本发明的一些实施方式中,方法还包括:

13.响应于再次解析到与保存在第一区域的相同类型的数据,判断再次解析到的数据与保存在所述第一区域的数据是否相同;

14.响应于再次解析到的数据与保存在所述第一区域的数据不同,则将再次解析到的数据发送到所述第二控制器并向所述第二控制器发出内存数据错误警告。

15.在本发明的一些实施方式中,方法还包括:

16.通过所述第二接口向所述内存模块发送查询指令以获取对应的内存信息;

17.将所述内存信息发送到第二控制器,并通过所述第二控制器获取所述内存模块的参数信息,同时将所述参数信息保存到所述第一控制器的第一区域。

18.在本发明的一些实施方式中,方法还包括:

19.响应于所述内存模块接收到所述cpu发出的查询内存参数的查询指令,所述内存模块将查询内存参数发送至所述cpu;

20.获取所述查询内存参数并将所述查询内存参数与所述第一区域的内存参数进行比对;

21.响应于比对结果为查询内存参数出现异常,将所述查询内存参数保存到第二区域,并向所述第二控制器上报异常情况。

22.在本发明的一些实施方式中,方法还包括:

23.响应于比对结果为内存参数出现异常,通过所述第一控制器再次向所述内存模块发出查询内存参数的查询指令,并获取对应的查询内存参数;

24.将所述查询内存参数再次与所述第一区域和/或第二区域的内存参数进行比对;

25.响应于所述查询内存参数与第二区域保存的内存参数相同,则将所述查询内存参数由所述第一控制器通过所述第一接口发送到所述cpu。

26.本发明的另一方面还提出一种内存通信系统,包括:

27.连接模块,所述连接模块配置用于通过第一控制器的第一接口与cpu的内存通信接口相连,以及通过第一控制器的第二接口与内存的内存通信接口相连;

28.解析模块,所述解析模块配置用于将所述第一控制器的第一接口和第二接口的中对应的信号引脚的电位变化进行同步或异步,同时获取所述第一接口和第二接口的数据内容并根据所述数据内容对所述cpu与内存的内存通信进行监控。

29.本发明的再一方面还提出一种计算机设备,包括:

30.至少一个处理器;以及

31.存储器,所述存储器存储有可在所述处理器上运行的计算机指令,所述指令由所述处理器执行时实现上述实施方式中任意一项所述方法的步骤。

32.本发明的又一方面还提出一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现上述实施方式中任意一项所述方法的步骤。

33.通过本发明提出的一种内存通信方法,通过服务器上其他逻辑芯片上的空闲的通信接口,实现cpu与内存的数据通信,并借助其他逻辑芯片的实现对cpu与内存在post过程中的数据监控及分析以生成对应的日志数据。方便工程师查找详细的日志数据,加快问题定位。同时可以为服务器的开机自检时提供冗余的数据校验手段,以降低数据异常对服务

器的开机自检的影响。

附图说明

34.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

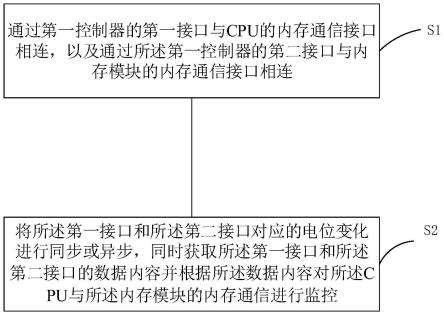

35.图1为本发明一实施例提出的一种内存通信方法的方法流程图;

36.图2为现有技术中内存通信链路的结构示意图;

37.图3为本发明一实施例提出的一种内存通信方法的通信链路的结构示意图;

38.图4为本发明一实施例提供的一种内存通信系统的结构示意图;

39.图5为本发明一实施例提供的一种计算机设备的结构示意图;

40.图6为本发明一实施例提供的一种计算机可读存储介质的结构示意图。

具体实施方式

41.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明实施例进一步详细说明。

42.需要说明的是,本发明实施例中所有使用“第一”和“第二”的表述均是为了区分两个相同名称非相同的实体或者非相同的参量,可见“第一”“第二”仅为了表述的方便,不应理解为对本发明实施例的限定,后续实施例对此不再一一说明。

43.本发明所要解决的是cpu在获取内存配置信息时的异常问题,主要是指在服务器bios的post过程中对内存的三次校验时三次数据不一致引起的校验失败情况,在传统方式的实现上难以有效定位出问题的原因,例如在服务器主板的设计完成后进行运行测试时,若因设计缺陷导致内存三次校验失败,由于bios程序以及主板设计问题无法对内存与cpu之间的数据传输进行检测,无法确认是内存问题还是传输链路上存在“链路串阻”等设计缺陷导致的问题。并且由于“链路串阻”等设计缺陷可能存在偶然性难以通过一次测试或多次测试检测到,因此即便存在这些问题,可能也无法通过服务器主板的成型测试检测到。这种偶然性的故障问题会随着服务器的使用伴随终身,严重的是当这种偶然性出现在客户的使用过程中时则会带来严重的质量问题或服务问题,影响客户的体验甚至会给客户带来“这家的服务器几乎全是垃圾,动不动就出现问题”的负面影响。

44.另外,随着服务器的使用,服务器主板上的电路老化更会加剧这种偶然性异常的产生,在使用一定时间后再次重启服务器时出现上述问题的概率急剧增加。

45.如图1所示,为解决上述问题,本发明的提出一种内存通信方法,包括:

46.步骤s1、通过第一控制器的第一接口与cpu的内存通信接口相连,以及通过所述第一控制器的第二接口与内存模块的内存通信接口相连;

47.步骤s2、将所述第一接口和所述第二接口对应的电位变化进行同步或异步,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控。

48.在实际中,cpu与内存的通信方式是采用spd链路的方式进行通信,而由于cpu与内

存的工作电压不同,而导致spd链路无法直接实现cpu与内存的互连。在实际中,传统的实现方式如图2所示,spd线路设计线路如图1所示。cpu与ddr4之间的spd实际为一路i2c,cpu端电平类型为1.0v的gtl电平,dimm(dual-inline-memory-modules,双重内嵌式内存模块)端的电平类型为2.5v的cmos电平,因此cpu与内存间通过一个gtl2014芯片做电平转换,可实现主从正常通信。8根内存以菊花链的拓扑挂在cpu一路spd总线下面,并按照要求通过外部的地址管脚配置各个内存为不同的i2c地址,从而实现一个i2c master与8个slave间的通信。spd总线在开机post过程中用于内存初始化及训练,完成内存正确识别;另外post完成后按照bios配置cpu会通过spd总线对内存温度进行轮询,以实现内存温度监控和过热保护机制,防止内存过温导致数据损坏甚至系统异常。spd的连接在当前技术中包括通过i2c(ddr4)和i3c(ddr5)的两种实现方式。

49.在步骤s1中,第一控制器可以是任意的嵌入式设备或具有一定数量通信接口可进行逻辑编程的设备,例如mcu、cpld、bmc、fpga等嵌入式设备,第一接口和第二接口可以是i2c或i3c,因此第一控制器可至少提供2路i2c或i3c用于实现cpu和内存的连接。即第一路独立连接cpu,第二路i2c或i3c独立连接内存(至少连接1个内存)。

50.在步骤s2中,在实现cpu与内存的通信时,第一控制器可以通过将第一接口和第二接口上对应的引脚的电位实现同步变化的方式实现cpu与内存的通信,或者建立两个完全独立的连接。即可以通过对第一控制器进行逻辑编程实现第一接口和第二接口上的引脚一一对应绑定,并当对应的引脚电位变化时使两者对应的引脚同步变化,或者是通过两个接口分别与对应的cpu或内存建立两个独立的连接,由第一控制器中转其数据通信。

51.进一步,第一控制器可以对第一接口和第二接口上的数据进行监控及解析,即对i2c或i3c数据进行解析,获取cpu与内存的通信数据,并根据数据内容进行分析以实现对cpu与内存之间的数据通信的监控。

52.在本发明的一些实施方式中,将所述第一接口和所述第二接口对应的电位变化进行同步或异步包括:

53.根据所述cpu和所述内存模块的内存通信接口的电压规范调整所述第一接口和所述第二接口的电压。

54.在本实施例中,基于cpu与内存的工作电压的不同,第一控制器还需要根据cpu的工作电压和内存的工作电压进行设置第一接口和第二接口的电压。例如,与cpu相连的第一接口电压可设置为1.0v,与内存相连的第二接口的电压可以是2.5v。根据不同的cpu型号和内存工作电压进行设定。若cpu与内存的工作电压相同时则完全设置相同的电压。

55.在本发明的一些实施方式中,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控包括:

56.根据内存通信通信协议对所述第一接口和/或所述第二接口的数据进行解析,并将解析结果保存到所述第一控制器的第一区域同时将所述解析结果发送到第二控制器上。

57.在本实施例中,第一控制器根据第一接口和第二接口的传输协议对第一接口和第二接口的数据进行解析,提取出第一接口和第二接口中传输的数据,同时将解析到的数据保存到第一控制器的指定区域,进一步将解析到的数据发送到第二控制器。

58.具体的,以图3所示为例,在本实施例中,采用cpld作为第一控制器,并由cpld的两路i2c作为连接cpu于内存的spd线路。在服务器开机自检时,cpu中运行的对应的bios程序

会向内存查询3次spd寄存器信息。由cpld在实现cpu与内存的spd通信电路电压转换的同时,cpld中实现相应的编程逻辑,根据i2c协议对cpu与内存的通信进行解析,获取由cpu发送到内存的查询指令等一切信息,以及获取从内存返回cpu的响应信息,响应信息包括spd寄存器中的具体值。

59.特别地,cpld将从内存获取到的spd寄存器的值保存到cpld上的ufm(cpld内部提供给用户使用的非易失性存储区域)某一区域。为服务器上每一个内存条建立一个spd保存区域,在获取到对应的内存的spd寄存器的值之后,便将spd寄存器的值保存到对应内存的对应区域。另外,将保存的spd寄存的发送到bmc上。在本发明的一些实施方式中,方法还包括:

60.响应于再次解析到与保存在第一区域的相同类型的数据,判断再次解析到的数据与保存在所述第一区域的数据是否相同;

61.响应于再次解析到的数据与保存在所述第一区域的数据不同,则将再次解析到的数据发送到所述第二控制器并向所述第二控制器发出内存数据错误警告。

62.在本实施例中,如前所述,在服务器开机自检时,会对内存的spd信息进行检测,共有3次获取内存参数的情况,并通过三次获取的数据对内存的状态进行冗余性状态检测,即通过3次数据的对比来确认内存是否正常。因此在本实施例中,如果是服务器第一次启动,则第一次的内存spd寄存器的值会保存到cpld的ufm区域,当cpu向内存发出第二次内存校验时,cpld便可解析到内存通过spd线路发送到cpu的内存的spd参数信息即对应的各个spd的值。另外,当服务器非第一次重启cpld的ufm区域中存在对应的内存的spd寄存器的值时,当服务器开机自检,cpu第一次向内存获取对应spd寄存器值时,cpld在解析到内存返回给cpu的数据中包含对应得spd寄存器值时,便可在第一次post的内存检测阶段对第一次获取的内存的spd参数进行校验。

63.具体地,当cpld再次从第一接口或第二接口所形成的spd线路中解析并获取到对应的保存到ufm区域的数据时,则判断新获取到的数据是否与保存到ufm上对应区域的数据相同。如果相同则说明内存状态正常,如果不同则说明存在对应的内存的spd出现异常,或者是内存故障。则将故障内存的信息发送到bmc,即将服务器上对应内存的位置、型号、spd寄存器信息发送到bmc,由bmc通过带外网络发送到运维系统。

64.需要说明的是,当cpld获取的内存spd寄存器的值与保存在ufm区域的对应的值不同时,bios的post过程可能仍然通过。例如服务器非第一次启动,cpld的ufm区域保存的服务器上所有内存的spd的值,当服务器重启进入post自检过程后,cpu向内存发送查询内存spd信息指令,内存向cpu第一次返回的spd寄存器值,假如存在某个spd寄存器的值与保存在ufm区域的值不同,则cpld通过bmc上报的运维系统。cpld不会干涉返回向cpu的spd寄存器的值,cpu接收到之后便会临时保存并再次向内存获取spd的值,如果内存在后续两次发送的spd寄存器均与第一次相同,则bios开机自检通过,服务器加载后续流程。但由于存在某个内存的spd的值与预先保存在ufm区域的值不同。因此服务器在运行时可能会存在相应的风险,而cpld通过bmc将对应的内存异常上报的运维系统之后便可由运维人员对内存异常的服务器进行处理。

65.在本发明的一些实施方式中,方法还包括:

66.通过所述第二接口向所述内存模块发送查询指令以获取对应的内存信息;

67.将所述内存信息发送到第二控制器,并通过所述第二控制器获取所述内存模块的参数信息,同时将所述参数信息保存到所述第一控制器的第一区域。

68.在本实施例中,通过cpld实现两路spd通信链路,即将cpu与内存的通信以“异步”的方式实现,由cpld以第一接口和cpu建立一个spd链路,在改链路中,cpld模拟内存与cpu进行通信,同时由cpld通过第二接口模拟cpu与内存进行通信。当cpu发出查询内存信息请求时,cpld模拟内存向cpu发送对应的链路信号,具体地,如果cpu与内存建立的链接是通过i2c或i3c建立,则根据i2c或i3c的协议规范,cpld模拟内存与cpu建立第一链接,同时cpld模拟cpu再与内存建立第二链接。

69.进一步,在服务器启动后,且bios还没有进入到post过程时,cpld通过上述第二链路以模拟cpu的方式向内存发送查询指令,获取内存中所有内存条的型号等信息,再讲型号信息发送到bmc上,由bmc通过带外网络向运维系统查询上述型号的内存的参数信息,即spd寄存器值等信息。bmc在从运维系统获取到对应的内存的参数信息后,则将获取到的参数信息发送给cpld,由cpld将参数信息保存到对应得ufm区域。

70.进一步,在bios进入到post过程后,在cpu第一次获取内存信息时便可由cpld对通过第一接口获取到的内存的spd寄存器的值与由bmc获取并保存到ufm区域的spd寄存器的值进行对比。

71.在本发明的一些实施方式中,方法还包括:

72.响应于所述内存模块接收到所述cpu发出的查询内存参数的查询指令,所述内存模块将查询内存参数发送至所述cpu;

73.获取所述查询内存参数并将所述查询内存参数与所述第一区域的内存参数进行比对;

74.响应于比对结果为查询内存参数出现异常,将所述查询内存参数保存到第二区域,并向所述第二控制器上报异常情况。

75.在本实施例中,在cpld的ufm区域保存有对应的内存参数即各个内存spd的寄存器的值情况下,当服务器进入post过程,如果三次内存校验中第一次内存校验的值与ufm区域的值不同时,则先临时将第一次的spd寄存器的值保存到ufm中的第二区域,即区别于之前保存的spd寄存器的值。通过第二区域对当前服务器重启的post过程的三次校验进行对比,以判断是否三次校验的值是否相同。即临时保存本次校验的三个寄存器的值(指同一个spd寄存器,三次的值)。同样,当第一次的值与ufm中的第一区域的值不同时,则向bmc上报,由bmc上传值运维系统。

76.具体地,当监控到内存向cpu返回对应的spd寄存器的数据时,cpld则将返回cpu的spd寄存器的值与ufm区域的值进行对比。如果此次返回cpu的spd寄存器的值与ufm区域中保存的值不相同,则将此次的spd寄存器的值临时保存到ufm区域中的第二区域。同时将数据上传到bmc。

77.需要说明的时,第一区域和第二区域同样在ufm区域内,不同的是第一区域保存有服务器上所有的内存的spd寄存器,第二区域中只保存异常的spd寄存器的值。例如,现有的内存的spd寄存器,包括256个通用spd寄存器,以及由生产商自定义的其他寄存器,以服务器16个dimm插槽计算,则第一区域至少有4096个寄存器,而第二区域只保存对应的与第一区域不同的寄存器,假如第一个内存条的第2个spd寄存器与第一区域的不同,则第二区域

值保存该spd寄存器三次的值。

78.在本发明的一些实施方式中,方法还包括:

79.响应于比对结果为内存参数出现异常,通过所述第一控制器再次向所述内存模块发出查询内存参数的查询指令,并获取对应的查询内存参数;

80.将所述查询内存参数再次与所述第一区域和/或第二区域的内存参数进行比对;

81.响应于所述查询内存参数与第二区域保存的内存参数相同,则将所述查询内存参数由所述第一控制器通过所述第一接口发送到所述cpu。

82.在本实施例中,如前所述,在通过第一控制器在cpu与内存之间建立“异步”的通信链路时,以cpld建立两个spd链路为例。且在服务器bios进入post过程中,对内存进行三次检测时,cpld发现内存返回的spd寄存器的值与保存在ufm区域的第一区域中对应的spd寄存器的值不同时,则由cpld通过建立的第二链路向内存再次发起查询spd寄存器参数的指令,并接收内存返回的对应的内存的spd的值,将接收到的spd的值与保存在ufm中的第一区域和第二区域中的spd的值进行再次对比,如果该值与第一区域的值一样,则说明之前收到的spd寄存器的值出现错误,由cpld再次补查的这一次spd寄存器的值恢复正常,则将补查的正常的spd的值由cpld与cpu建立的第一链路发送到cpu,同时将正常的spd寄存器的值保存到第二区域替换原先错误的值,用于post过程的后续校验,即防止后续第二次校验以及第三次校验时出现spd寄存器值异常的情况。可有效避免在服务器重启bios进入post过程中spd寄存器的数据在链路传输时数据而无法及时纠正的情况。

83.通过本发明提出的一种内存通信方法,通过服务器上其他逻辑芯片上的空闲的通信接口,实现cpu与内存的数据通信,并借助其他逻辑芯片的实现对cpu与内存在post过程中的数据监控及分析以生成对应的日志数据。方便工程师查找详细的日志数据,加快问题定位。同时可以为服务器的开机自检时提供冗余的数据校验手段,以降低数据异常对服务器的开机自检的影响。

84.如图4所示,本发明的另一方面还提出一种内存通信系统,包括:

85.连接模块1,所述连接模块1配置用于通过第一控制器的第一接口与cpu的内存通信接口相连,以及通过第一控制器的第二接口与内存的内存通信接口相连;

86.解析模块2,所述解析模块2配置用于将所述第一控制器的第一接口和第二接口的中对应的信号引脚的电位变化进行同步或异步,同时获取所述第一接口和第二接口的数据内容并根据所述数据内容对所述cpu与内存的内存通信进行监控。

87.如图5所示,本发明的再一方面还提出一种计算机设备,包括:

88.至少一个处理器21;以及

89.存储器22,所述存储器22存储有可在所述处理器21上运行的计算机指令23,所述指令23由所述处理器执行时实现一种内存通信方法,包括:

90.通过第一控制器的第一接口与cpu的内存通信接口相连,以及通过所述第一控制器的第二接口与内存模块的内存通信接口相连;

91.将所述第一接口和所述第二接口对应的电位变化进行同步或异步,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控。

92.在本发明的一些实施方式中,将所述第一接口和所述第二接口对应的电位变化进

行同步或异步包括:

93.根据所述cpu和所述内存模块的内存通信接口的电压规范调整所述第一接口和所述第二接口的电压。

94.在本发明的一些实施方式中,同时获取所述第一接口和所述第二接口的数据内容并根据所述数据内容对所述cpu与所述内存模块的内存通信进行监控包括:

95.根据内存通信通信协议对所述第一接口和/或所述第二接口的数据进行解析,并将解析结果保存到所述第一控制器的第一区域同时将所述解析结果发送到第二控制器上。

96.在本发明的一些实施方式中,方法还包括:

97.响应于再次解析到与保存在第一区域的相同类型的数据,判断再次解析到的数据与保存在所述第一区域的数据是否相同;

98.响应于再次解析到的数据与保存在所述第一区域的数据不同,则将再次解析到的数据发送到所述第二控制器并向所述第二控制器发出内存数据错误警告。

99.在本发明的一些实施方式中,方法还包括:

100.通过所述第二接口向所述内存模块发送查询指令以获取对应的内存信息;

101.将所述内存信息发送到第二控制器,并通过所述第二控制器获取所述内存模块的参数信息,同时将所述参数信息保存到所述第一控制器的第一区域。

102.在本发明的一些实施方式中,方法还包括:

103.响应于所述内存模块接收到所述cpu发出的查询内存参数的查询指令,所述内存模块将查询内存参数发送至所述cpu;

104.获取所述查询内存参数并将所述查询内存参数与所述第一区域的内存参数进行比对;

105.响应于比对结果为查询内存参数出现异常,将所述查询内存参数保存到第二区域,并向所述第二控制器上报异常情况。

106.在本发明的一些实施方式中,方法还包括:

107.响应于比对结果为内存参数出现异常,通过所述第一控制器再次向所述内存模块发出查询内存参数的查询指令,并获取对应的查询内存参数;

108.将所述查询内存参数再次与所述第一区域和/或第二区域的内存参数进行比对;

109.响应于所述查询内存参数与第二区域保存的内存参数相同,则将所述查询内存参数由所述第一控制器通过所述第一接口发送到所述cpu。

110.如图6所示,本发明的又一方面还提出一种计算机可读存储介质401,所述计算机可读存储介质401存储有计算机程序402,其特征在于,所述计算机程序402被处理器执行时实现上述实施方式中任意一项所述方法的步骤。

111.以上是本发明公开的示例性实施例,但是应当注意,在不背离权利要求限定的本发明实施例公开的范围的前提下,可以进行多种改变和修改。根据这里描述的公开实施例的方法权利要求的功能、步骤和/或动作不需以任何特定顺序执行。此外,尽管本发明实施例公开的元素可以以个体形式描述或要求,但除非明确限制为单数,也可以理解为多个。

112.应当理解的是,在本文中使用的,除非上下文清楚地支持例外情况,单数形式“一个”旨在也包括复数形式。还应当理解的是,在本文中使用的“和/或”是指包括一个或者一个以上相关联地列出的项目的任意和所有可能组合。

113.上述本发明实施例公开实施例序号仅仅为了描述,不代表实施例的优劣。

114.本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

115.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本发明实施例公开的范围(包括权利要求)被限于这些例子;在本发明实施例的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,并存在如上所述的本发明实施例的不同方面的许多其它变化,为了简明它们没有在细节中提供。因此,凡在本发明实施例的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明实施例的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1