量子比特系统及量子计算的方法

1.本技术涉及量子计算技术领域,尤其涉及一种量子比特系统及使用其进行量子计算的方法。

背景技术:

2.拓扑量子计算方案是将量子信息非局域地存储于空间分离的马约拉纳零能模中,进而实现对局域微扰和噪声的免疫,因此具有内禀的容错性,从而在根本的物理层面上解决量子退相干问题,为构建容错量子计算机奠定坚实基础。在该领域,“超导-半导体纳米线”复合体系是最受关注也是目前为止最成功的理想材料体系,具有理论图像清晰且易于精细参数调控等优势。简单来讲,对于具有强自旋轨道耦合的一维半导体纳米线,通过常规超导近邻构建复合器件,便可在磁场驱动下人工制备出拓扑超导态,在边界处会出现马约拉纳零能模,这是构建拓扑量子比特的基础载体。

3.现有技术中,有利用超导共面波导谐振腔(coplanar superconducting waveguide,cpw)和量子比特耦合,进行量子信息读取和操控的方案。该方案利用超导材料,例如铌钛氮(nbtin)构成的共面波导谐振腔,一旦施加驱动“超导-半导体纳米线”体系进入拓扑相所需的大磁场,谐振腔的品质因子便会迅速降低,以致无法进行信号读取。也就是说,当下所有基于超导共面波导谐振腔的方案难以与量子比特进入拓扑相所需的大磁场兼容,故而无法直接用于构建拓扑量子比特。

4.若使用打孔钉扎磁通的技术去改善超导共面波导谐振腔的磁场兼容性,又会引入设计仿真复杂、加工制备样品效率低、良品率低的问题,同时该设计方案也会使得量子比特的周遭环境变得更加复杂,退相干时间会因此受到抑制。

技术实现要素:

5.有鉴于现有技术的至少一个缺陷,本发明提供了一种量子比特系统,包括量子比特芯片和用于量子比特耦合的谐振腔,其中,所述谐振腔包括:

6.第一半腔,为顶面具有开口的中空结构,所述顶面上设置有槽,用于放置所述量子比特芯片;

7.第二半腔,为底面具有开口的中空结构,配置成与所述第一半腔拼接,形成内部为长方体的空腔,所述量子比特芯片位于所述长方体的空腔的中心区域,

8.其中所述第一半腔与所述第二半腔采用无氧铜材料制成。

9.根据本发明的一个方面,其中所述第一半腔具有第一侧面,所述第二半腔具有第二侧面,所述第一侧面与所述第二侧面拼接,形成边墙结构,所述边墙结构的厚度大于预设值。

10.根据本发明的一个方面,其中所述量子比特位于所述量子比特芯片上,所述量子比特包括:

11.至少一个约瑟夫森结,每个约瑟夫森结包括通过纳米线连接的两个超导体,用于

产生二能级系统;

12.电容,与所述至少一个约瑟夫森结并联,其中:

13.所述至少一个约瑟夫森结的部分或全部位于所述边墙结构之内。

14.根据本发明的一个方面,其中所述第一侧面上设置有第一sma接头,用于接入外部电压源,所述外部电压源通过所述第一sma接头的金属芯引线与所述至少一个约瑟夫森结的栅极连接,用于调控所述二能级系统的跃迁频率,其中:

15.所述第一sma接头的金属芯引线位于所述边墙结构之内。

16.根据本发明的一个方面,其中,所述约瑟夫森结的栅极位于所述约瑟夫森结的两个超导体的顶部或底部,或与所述两个超导体共面,处于所述两个超导体旁形成边栅。

17.根据本发明的一个方面,其中所述第二侧面上设置有第二sma接头和第三sma接头,分别作为微波信号的输入端和输出端,所述第二sma接头和所述第三sma接头的金属芯引线深入所述谐振腔内部的长度可调。

18.根据本发明的一个方面,其中所述长方体的空腔的尺寸为:长60-80mm,深20-40mm,宽2-8mm。

19.根据本发明的一个方面,其中所述长方体的空腔的尺寸为:长70mm,深30mm,宽5mm。

20.本发明还提供一种使用如上文所述的量子比特系统进行量子计算的方法,其中,所述第二半腔具有第二侧面,所述第二侧面上设置有第二sma接头和第三sma接头,分别作为微波信号的输入端和输出端,所述方法包括:

21.通过所述第二sma接头接收向所述谐振腔输入的第一微波信号;

22.通过所述第一微波信号在所述谐振腔中形成谐振,并与所述量子比特发生耦合;

23.通过所述第三sma接头输出来自所述谐振腔的第二微波信号。

24.根据本发明的一个方面,其中所述量子比特位于所述量子比特芯片上,所述量子比特包括:至少一个约瑟夫森结,每个约瑟夫森结包括通过纳米线连接的两个超导体,用于产生二能级系统;所述第一半腔具有第一侧面,所述第一侧面上设置有第一sma接头,用于接入外部电压源,所述外部电压源通过所述第一sma接头的金属芯引线与所述约瑟夫森结的栅极连接,所述方法进一步包括:

25.通过调节所述外部电压源的输入电压,来调节所述二能级系统的跃迁频率。

26.根据本发明的一个方面,所述方法进一步包括:

27.通过调节所述第二sma接头和所述第三sma接头的金属芯引线深入所述谐振腔内部的长度,来调节所述谐振腔与所述输入端和输出端的耦合强度。

28.本发明所提供的量子比特系统及量子计算方法,其中三维设计的无氧铜谐振腔作为量子比特的读取谐振腔,因为铜腔在强磁场下仍可保持一定的品质因子,从而解决了共面波导谐振腔在强磁场下失去超导电性的磁场兼容问题,减弱了相应的电流加热效应;加厚的边墙结构,降低了金属部件引入的耗散,提高了谐振腔的品质因数和量子比特的寿命;可调的输入输出引线长度,实现了谐振腔与输入输出端的耦合强度可调。本发明所提供的三维谐振腔加工更为简便,易于规模化,且可以反复使用,对于不同的量子比特芯片具有普适性。同时,该谐振腔封闭的结构为量子比特提供了更好的保护,使其免受外部电磁环境的干扰,不需要进行额外的封装,简化了器件制备工艺,有利于延长量子比特的退相干时间,

同时也给研究半导体纳米线体系中潜在的安德烈夫机制等物理问题提供了新的技术手段。

附图说明

29.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图,而并不超出本技术要求保护的范围。

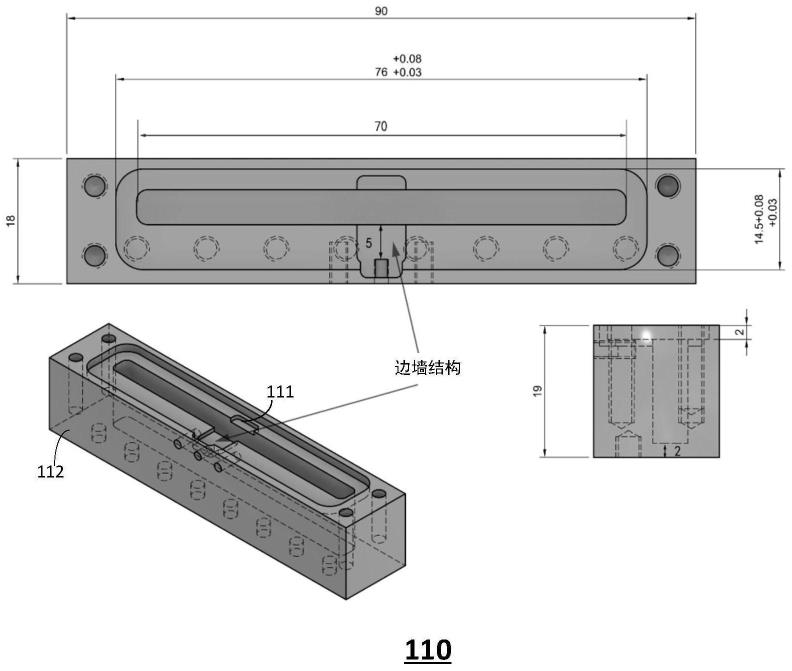

30.图1a示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的第一半腔;

31.图1b示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的第二半腔;

32.图2示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的透视图;

33.图3示出了本发明的一个实施例所提供的量子比特系统中的约瑟夫森结;

34.图4示出了本发明的一个实施例所提供的量子比特系统中的量子比特芯片;

35.图5示出了本发明的一个实施例所提供的量子比特系统中的量子比特芯片部分位于边墙结构之中;

36.图6a示出了本发明的一个实施例所提供的量子比特系统中的谐振腔上的第一sma接头;

37.图6b示出了本发明的一个实施例所提供的量子比特系统中的谐振腔上的第二sma接头和第三sma接头;

38.图7a示出了本发明的一个实施例所提供的量子比特系统中的谐振腔在te101本征模式下的电场强度分布;

39.图7b示出了本发明的一个实施例所提供的量子比特系统中的谐振腔在te102本征模式下的电场强度分布;

40.图7c示出了本发明的一个实施例所提供的量子比特系统中的谐振腔在te103本征模式下的电场强度分布;

41.图7d示出了本发明的一个实施例所提供的量子比特系统中的谐振腔在te104本征模式下的电场强度分布;

42.图8a示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的谐振频率随超导电流变化的曲线;

43.图8b示出了本发明的一个实施例所提供的量子比特系统中的谐振腔与量子比特的耦合强度随超导电流变化的曲线;

44.图8c示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的充电能随超导电流变化的曲线;

45.图8d示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的色散位移随超导电流变化的曲线;

46.图8e示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的谐振频率随量子比特芯片位于边墙结构中的位置变化的曲线;

47.图8f示出了本发明的一个实施例所提供的量子比特系统中的谐振腔与量子比特的耦合强度随量子比特芯片位于边墙结构中的位置变化的曲线;

48.图8g示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的充电能随

量子比特芯片位于边墙结构中的位置变化的曲线;

49.图8h示出了本发明的一个实施例所提供的量子比特系统中的谐振腔的色散位移随量子比特芯片位于边墙结构中的位置变化的曲线;

50.图9示出了本发明的一个实施例所提供的量子计算方法;

51.图10a示出了本发明的一个实施例所提供的与量子比特耦合的谐振腔的传输特性随微波功率变化的二维图;

52.图10b示出了本发明的一个实施例所提供的与量子比特耦合的谐振腔的传输特性随栅门电压变化的二维图;

53.图10c示出了本发明的一个实施例所提供的量子比特的跃迁频率随栅门电压变化的二维图。

具体实施方式

54.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

55.以上对本技术实施例进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明仅用于帮助理解本技术的方法及其核心思想。同时,本领域技术人员依据本技术的思想,基于本技术的具体实施方式及应用范围上做出的改变或变形之处,都属于本技术保护的范围。综上所述,本说明书内容不应理解为对本技术的限制。

56.本发明提供一种量子比特系统,包括量子比特和用于量子比特耦合的谐振腔,所述谐振腔为量子比特提供了封闭的空间局域环境,有效减少了量子比特与外界环境噪声的耦合,同时所述谐振腔的三维结构设计及材料选择,解决了矢量高磁场的兼容问题,有望在实验上完成拓扑量子比特的构建。

57.根据本发明的一个实施例,如图1a、图1b所示,本发明提供一种量子比特系统,包括量子比特和用于量子比特耦合的谐振腔100。其中,谐振腔100包括:第一半腔110和第二半腔120。其中:

58.如图1a所示(图1a分别示出了第一半腔110的立体图、俯视图和侧视图),第一半腔110为顶面具有开口的中空结构,所述顶面上设置有槽111,用于放置量子比特芯片。

59.如图1b所示(图1b分别示出了第二半腔120的立体图、俯视图和侧视图),第二半腔120为底面具有开口的中空结构,配置成能够与第一半腔110拼接,形成内部为长方体的空腔,所述量子比特芯片位于所述长方体的空腔的中心区域,以实现与谐振腔100最大程度的电容耦合。

60.可选地,如图1a、图1b所示,第一半腔110的顶面具有凹陷部分,第一半腔110的开口位于凹陷部分之内;第二半腔120的底面具有凸起部分,第二半腔120的开口位于凸起部分之内。第一半腔110的凹陷部分与第二半腔120的凸起部分卡接,以固定谐振腔100。可选地,第一半腔110与第二半腔120进一步通过螺纹连接进行固定。

61.图2示出了第一半腔110与第二半腔120拼接后,形成谐振腔100的透视图,其中量

子比特芯片位于谐振腔100内部长方体空腔的中心区域。第一半腔110与第二半腔120拼接,形成内部为长方体的空腔,使输入微波信号在谐振腔100的内部形成驻波,谐振腔100具有预设值对应的谐振频率。

62.第一半腔110与第二半腔120采用无氧铜材料制成。现有技术中的共面波导谐振腔通常采用超导材料制成,以提高腔本身的品质因子。然而超导材料具有完全抗磁性,一旦施加驱动量子比特系统进入拓扑相所需的大磁场,谐振腔的品质因子便会迅速降低,以致无法进行信号读取。本发明的上述实施例将无氧铜作为谐振腔的材料,可以外加高磁场偏置并保证良好的热传导性。

63.根据本发明的一个实施例,如图1a、图1b所示,第一半腔110用于与第二半腔120拼接的顶面为矩形,长为90mm,宽为18mm。顶面具有大致矩形的凹陷部分,凹陷部分长度为76mm,加工时可增加0.03-0.08mm,宽度为14.5mm,加工时可增加0.03-0.08mm,凹陷深度为2mm。矩形开口位于凹陷部分之内,长度为60-80mmm,优选为70mm,宽度为2-8mm,优选为5mm,中空结构的内部深度为10-20mm,优选为15mm。第二半腔120用于与第一半腔拼接的底面为矩形,长为90mm,宽为18mm。底面具有大致矩形的凸起部分,凸起部分长度为76mm,加工时可减少0.03-0.08mm,宽度为14.5mm,加工时可减少0.03-0.08mm,凸起高度为2mm。矩形开口位于凸起部分之内,拼接后与第一半腔110的矩形开口对齐,长度为60-80mm,优选为70mm,宽度为2-8mm,优选为5mm,中空结构的内部深度为10-20mm,优选为15mm。

64.根据本发明的一个实施例,如图1a、图1b所示,本发明所提供的量子比特系统中,谐振腔100中的第一半腔110具有第一侧面112,第二半腔120具有第二侧面121,第一侧面112与第二侧面121拼接,形成边墙结构,所述边墙结构的厚度大于预设值。

65.本发明所提供的用于量子比特耦合的谐振腔100,通过设计厚度大于预设值的边墙结构,可以将容易产生耗散的部件(如金属芯引线等),藏于边墙结构之中,降低其对谐振腔100的品质因子的影响。

66.根据本发明的一个实施例,如图3所示,本发明所提供的量子比特系统中,所述量子比特包括:

67.至少一个约瑟夫森结,每个约瑟夫森结包括通过纳米线连接的两个超导体,用于产生二能级系统。所述两个超导体分别作为约瑟夫森结的源极和漏极,每个约瑟夫森结的栅极与所述两个超导体位于同一平面(边栅设计),或者,所述约瑟夫森结的栅极位于所述两个超导体的顶部(顶栅设计)或背部(背栅设计),在顶栅设计或背栅设计中,在所述栅极与所述两个超导体之间加入绝缘层,构成平行板电容。

68.所述两个超导体包括厚度为100nm的nbtin薄膜,所述纳米线以inas材料制成,外延生长al膜。

69.所述量子比特还包括电容,与所述约瑟夫森结并联。

70.根据本发明的一个实施例,如图4所示,本发明还提供一种包括上述量子比特的量子比特芯片(图4分别示出了该量子比特芯片的整体图和局部放大图)。将量子比特制备于衬底之上,衬底材料包括高阻硅或蓝宝石,所述衬底上具有接触点,用于加工和固定约瑟夫森结。图4中所示的条形为大容值电容,与所述量子比特电连接,用于抑制电荷噪声,延长所述量子比特退相干的时间。图4中引线引出的部分为nbtin接触电极,用于连接约瑟夫森结的栅极,外部电压源通过接触电极为约瑟夫森结的栅极提供栅门电压。

71.根据本发明的一个实施例,如图4所示,本发明所提供的量子比特系统中,量子比特芯片的尺寸为11.3mm*5.0mm,用于加工和固定约瑟夫森结的接触点所占面积为0.28mm*0.28mm,大容值电容所占面积为4.0mm*0.2mm、0.3mm*0.2mm,其他器件的尺寸、引线长度、距离等微纳加工参数如图中所示。

72.根据本发明的一个实施例,如图5所示,将包括量子比特的量子比特芯片放置在上文中所述的第一半腔110的槽111中,则图中所示实线框中的部分位于边墙结构以内,其中虚线框的部分包括如图3所示的约瑟夫森结。通过设置边墙结构,使量子比特芯片上的至少一个约瑟夫森结的核心部分位于所述边墙结构之内。

73.根据本发明的一个实施例,如图6a所示,本发明所提供的量子比特系统中,第一半腔110的第一侧面112上设置第一sma接头113(sma接头即小型螺纹同轴连接器,subminiature version a)。具体地,第一侧面112上设置端口与分别位于端口两侧的螺钉孔,将第一sma接头113放入端口中,并通过端口两侧旋入螺钉进行固定。第一sma接头113用于接入外部电压源,所述外部电压源通过所述第一sma接头113的金属芯引线连接到接触电极上,从而与所述至少一个约瑟夫森结的栅极连接,用于提供栅门电压,通过调节栅门电压调控所述二能级系统的跃迁频率,其中:

74.所述第一sma接头113的金属芯引线位于所述边墙结构之内。

75.在本征模式下,对谐振腔100频率最低的前四个本征模式的谐振频率和电场分布进行求解,仿真结果如图7a至图7d所示。将sma金属芯引线和基于半导体纳米线的约瑟夫森结的核心部分藏于边墙之中,可以有效降低其对谐振腔品质因子的影响。从图7a至图7d(对应四个本征态的谐振频率)可以得知,在边墙结构内的电场强度明显较小,则对应的电场分布占比较小,引入的耗散也相应较小。

76.根据本发明的一个实施例,如图6b所示,本发明所提供的量子比特系统中,第二半腔120的第二侧面121上设置第二sma接头122和第三sma接头123。具体地,第二侧面121上设置两个端口及分别位于两个端口两侧的四个螺钉孔,将第二sma接头122和第三sma接头123分别放入两个端口,并通过在两个端口两侧旋入四个螺钉进行固定。第二sma接头122和第三sma接头123分别作为微波信号的输入端和输出端,第二sma接头122和第三sma接头123的金属芯引线深入谐振腔100内部的长度可调。

77.通过改变第二sma接头122和第三sma接头123的金属芯引线伸入谐振腔100内部的长度,可以对谐振腔100与输入输出端的耦合强度进行调节。

78.结合量子比特芯片设计进行仿真验证,在图1a、图1b所示的谐振腔100中的槽111上置入长宽比为11.25mm*5.5mm的量子比特芯片,对量子比特系统进行电磁场模拟仿真,仿真结果如图8a至图8h所示。图8a为谐振腔的谐振频率随电感变化的曲线,改变电感进而能改变超导电流达到调控量子比特频率的目的,图8b为谐振腔与量子比特的耦合强度随电感变化的曲线,图8c为谐振腔的充电能随电感变化的曲线,图8d为谐振腔的色散位移随电感变化的曲线,图8e为谐振腔的谐振频率和量子比特的跃迁频率随量子比特芯片位于边墙结构中的位置变化的曲线,图8f为谐振腔与量子比特的耦合强度随量子比特芯片位于边墙结构中的位置变化的曲线,图8g为谐振腔的充电能随量子比特芯片位于边墙结构中的位置变化的曲线,图8h为谐振腔的色散位移随量子比特芯片位于边墙结构中的位置变化的曲线。从图8a-图8h可以得知,对于跃迁频率不同的量子比特芯片,谐振腔100与之耦合强度均约

为100mhz,充电能对应的非谐性大小约为200mhz,色散位移随着量子比特跃迁频率的不同而变化明显。

79.本发明所提供的量子比特系统,其中三维设计的无氧铜谐振腔作为量子比特的读取谐振腔,解决了共面波导谐振腔的磁场兼容问题,减弱了相应的电流加热效应;加厚的边墙结构,降低了金属部件引入的耗散,提高了谐振腔的品质因子;可调的输入输出引线长度,实现了谐振腔与输入输出端的耦合强度可调。本发明所提供的三维谐振腔加工更为简便,易于规模化,且可以反复使用,对于不同的量子比特芯片具有普适性。同时,该谐振腔封闭的结构为量子比特提供了更好的保护,使其免受外部电磁环境的干扰,不需要进行额外的封装,简化了器件制备工艺,有利于延长量子比特的退相干时间,同时也给研究半导体纳米线体系中潜在的安德烈夫机制等物理问题提供了新的技术手段。

80.根据本发明的一个实施例,如图9所示,本发明还提供一种使用如上文所述的量子比特系统进行量子计算的方法10,其中,所述第二半腔具有第二侧面,所述第二侧面上设置第二sma接头和第三sma接头,分别作为微波信号的输入端和输出端,进行量子计算的方法10包括步骤s101至步骤s103。其中:

81.在步骤s101中,通过所述第二sma接头向所述谐振腔输入第一微波信号;

82.在步骤s102中,所述第一微波信号在所述谐振腔中形成谐振,并与所述量子比特发生耦合;

83.在步骤s103中,通过所述第三sma接头读取所述谐振腔输出的第二微波信号。

84.根据本发明的一个实施例,其中所述量子比特包括:至少一个约瑟夫森结,每个约瑟夫森结包括通过纳米线连接的两个超导体,用于产生二能级系统;所述第一半腔具有第一侧面,所述第一侧面上设置第一sma接头,用于接入外部电压源,所述外部电压源通过所述第一sma接头的金属芯引线与所述约瑟夫森结的栅极连接,方法10进一步包括:

85.通过调节所述外部电压源的输入电压,来调节所述二能级系统的跃迁频率。

86.根据本发明的一个实施例,方法10进一步包括:

87.通过调节所述第二sma接头和所述第三sma接头的金属芯引线深入所述谐振腔内部的长度,来调节所述谐振腔与输入输出端的耦合强度。

88.通过实验构建基于半导体inas纳米线的量子比特器件,观察与量子比特耦合的谐振腔传输特性随测量微波功率的变化,如图10a所示,当微波功率较高时,谐振腔显示出其裸腔状态下的本征谐振频率5.343ghz,当微波功率逐渐降低到单光子水平时,量子比特对谐振腔的作用显现出来,整个系统的谐振频率逐渐偏移到色散区谐振点5.3457ghz,偏移量为2.7mhz。同时,通过栅门电压调节量子比特的跃迁频率,观察到真空拉比劈裂效应,得到量子比特和谐振腔的耦合强度因子约为58mhz。图10b示出了与量子比特耦合的谐振腔的传输特性随栅门电压的变化。图10c示出了量子比特的跃迁频率随栅门电压的变化。

89.本发明所提供的量子比特系统及量子计算方法,有利于抑制传统transmon量子比特由于磁场调控带来的串扰,也减弱了相应的电流加热效应,使得其更易于规模化,同时也给研究半导体纳米线体系中潜在的安德烈夫机制等物理问题提供了新的技术手段。

90.本发明中所涉及的量子比特包括具有0态、1态和叠加态的信息载体。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1