轻量级片上学习FPGA硬件架构及其设计方法

轻量级片上学习fpga硬件架构及其设计方法

技术领域

1.本发明属于人工智能和类脑智能芯片技术领域,具体涉及一种轻量级片上学习fpga硬件架构及其设计方法。

背景技术:

2.最早开始对人类大脑计算能力建模的是人工神经网络(ann),多年以来,ann取得了显著的成果。但近年来对人类大脑的研究表明,信息在大脑神经元中是通过动作电位的形式传递的。基于此wolfgang maass等人提出了更符合实际生物神经元模型的脉冲神经网络。脉冲神经网络相较于人工神经网络而言,其输入脉冲在时空上是稀疏的,神经元只需要在输入脉冲到达时才进行计算,并且神经元只在达到特定的阈值时才发射脉冲。因此与传统的人工神经网络相比,脉冲神经网络(snn)具有的能耗更低。并且近年来的前馈型脉冲神经网络,不像人工神经网络那样需要全局反向传播,有利于实现片上学习。冯

˙

诺依曼体系架构即传统计算机体系对于实现snn具有局限性。即cpu只能以串行的方式执行程序,而snn涉及大量的并行计算,从而导致snn计算效率低。而gpu(图形处理器)虽然可以并行执行程序,但snn的稀疏特性无法在上面实现。因此,人们提出了在fpga(现场可编程逻辑门阵列)和asic(专用集成电路)上实现snn。如带有交叉开关和支持任意大规模snn拓扑的truenorth处理器以及利用arm核实现可编程snn模型的spinnaker处理器。但是它们主要是针对神经科学领域的研究,且芯片面积消耗大,不适用于嵌入式边缘或移动计算场景。

3.因此,有必要开发一种新的轻量级片上学习fpga硬件架构及其设计方法。

技术实现要素:

4.本发明的目的在于提供一种轻量级片上学习fpga硬件架构及其设计方法,能提高计算速度,降低硬件资源消耗。

5.第一方面,本发明所述的一种轻量级片上学习fpga硬件架构的设计方法,包括以下步骤:

6.步骤一、设计compressive-tempotron两层脉冲神经网络架构、软件定点模拟,具体包括:

7.步骤1-1.确定对输入图像的编码方式:

8.输入层采用多脉冲时间编码将图像的像素转换为脉冲序列,其中,多脉冲时间编码采用泄漏累积发射神经元模型:

[0009]vm

(t)=vm(t-1)+β

×

x

ꢀꢀꢀꢀꢀꢀ

(1)

[0010]

其中:t是当前时间步,t-1是上一个时间步,vm是神经元膜电位,x是单个像素点的像素值,β是像素随时间线性增长的增长率;

[0011]

当膜电位累加到预先设定好的阈值时,神经元发射脉冲,并立即回到0,随后再次随着时间线性增长;

[0012]

步骤1-2.确定脉冲特征提取规则,改进特征提取层:

[0013]

压缩感知层从输入层送入的脉冲中提取具有时空信息的脉冲特征,在一幅图中,随机选择两个正极性patches,以及两个负极性patches;每个patch由位置、大小和极性三个属性确定,其中,位置和大小为随机选择;压缩感知层和tempotron层均基于事件驱动;

[0014]

压缩感知层采用具有生物似然性的泄漏累积发射神经元模型,其膜电位以事件驱动的形式描述为:

[0015][0016]

其中:τm是第一时间衰减常数,t

p

是突触前脉冲到达第p个patch的时间,t

prev

是在当前时间之前突触前脉冲到达任一突触的时间,v是突触后神经元的膜电位,patch的极性值由+1/-1表示,即+1表示patch极性为正,-1表示patch极性为负,s

p

为第p个patch的面积与其极性的乘积;

[0017]

步骤1-3.确定学习层算法,改进tempotron层;

[0018]

对传统tempotron学习规则进行了改进,具体为:

[0019]

基于事件驱动的突触后神经元膜电位描述为:

[0020][0021]

其中:ti是突触前脉冲到达第i个突触的时间,ωi为第i个突触的权重,v为突触后神经元的膜电位;当神经元膜电位超过预先设定的阈值时,复位至原来的α倍,0≤α《1,随后神经元膜电位继续累加-发射-复位;

[0022]

使用单核psp进行权重更新,其中,单核psp为:

[0023][0024]

其中:τ为第二时间衰减常数,t

max

为在时间窗口内突触后神经元膜电位达到最大值的时间,ti是突触前脉冲到达第i个突触的时间;

[0025]

权重更新时,ti应小于等于t

max

,权重更新描述为:

[0026][0027]

其中:λ是学习率;

[0028]

步骤1-4、软件定点模拟:通过定点软件仿真,评估compressive-tempotron神经网络在mnist数据集的正确率。

[0029]

步骤二、设计硬件架构:将compressive-tempotron神经网络部署在fpga中。

[0030]

可选地,将式(5)中的累加项改写为事件驱动的突触trace更新方式,即将公式(5)中的替换为公式(6),具体为:

[0031]

[0032]

其中:τ为第二时间衰减常数,t

max

为在时间窗口内神经元膜电位达到最大值的时间,t

prev

是在当前时间之前突触前脉冲到达任一突触的时间,qi是第i个突触的突触trace;

[0033]

当神经元接收到一个突触前脉冲时,它的膜电位根据式(3)进行更新,并将突触trace(qi(t))乘上exp(-δti/τ),然后增加1;如果更新后的膜电位大于最大膜电位,则用神经元的当前膜电位更新其最大膜电位,并备份当前的突触trace;当突触后神经元发射脉冲,突触trace与突触后神经元膜电位协同复位至原来的α倍;当处理完一张图的所有事件后,将-λqi(t

max

)或λqi(t

max

)加到突触权重以完成式(5)中。

[0034]

第二方面,本发明所述的一种轻量级片上学习fpga硬件架构,包括全局控制器、压缩感知层和tempotron层;

[0035]

所述全局控制器分别与压缩感知层和tempotron层连接,全局控制器用于控制压缩感知层和tempotron层;

[0036]

所述压缩感知层包括m1个第一tile单元,其中,每个第一tile单元以时间复用的方式对k1个第一神经元进行处理;其中,1≤m1≤64,1≤k1≤8;其中,所述第一tile单元包括第一局部控制器,以及分别与第一局部控制器连接的第一膜电位存储器、第一发射管理模块、第一膜电位更新模块、patch存储器、第一指数查找表存储器和第一前一个事件存储器,所述第一膜电位存储器还分别与第一发射管理模块、第一膜电位更新模块连接,第一发射管理模块与第一膜电位更新模块连接,第一膜电位更新模块分别与patch存储器、第一指数查找表存储器和第一前一个事件存储器连接;

[0037]

所述tempotron层包括m2个第二tile单元,其中,每个第二tile单元以时间复用的方式对k2个第二神经元进行处理;其中,1≤m2≤64,1≤k2≤4;其中,所述第二tile单元包括第二局部控制器,以及分别与第二局部控制器连接的学习模块、备份trace存储器、最大膜电位管理模块、第二发射管理模块、权重存储器、第二膜电位存储器、trace存储器、trace更新模块、第二膜电位更新模块、最大膜电位存储器、第二前一个事件存储器和第二指数查表存储器;所述学习模块还分别与权重存储器、第二发射管理模块和备份trace存储器连接;第二膜电位更新模块还分别与权重存储器、第二膜电位存储器、trace更新模块和第二指数查表存储器连接;第二膜电位存储器还与第二发射管理模块连接;trace更新模块还分别与第二指数查表存储器、第二前一个事件存储器和trace存储器连接;trace存储器还与第二发射管理模块连接;最大膜电位管理模块还分别与最大膜电位存储器、第二发射管理模块和备份trace存储器连接。

[0038]

可选地,所述第二膜电位更新模块包括第一乘法器和第一加法器,第一乘法器和第一加法器连接;

[0039]

当有脉冲到来时触发膜电位的更新,首先从第二前一个事件存储器中读出t

prev

,将当前时间t减去t

prev

得到时间差δt,通过δt查存储在第二指数查表存储器中的指数查找表得到指数衰减系数,查找到的指数衰减系数和从第二膜电位存储器读取的当前神经元的膜电位,作为第一乘法器的输入,得到第一乘法器的输出,即经过衰减的膜电位,衰减后的膜电位和从权重存储器中读取的当前神经元的脉冲到达的突触的权重作为第一加法器的输入,得到第一加法器的输出,即更新后的膜电位v(t),并将更新后的膜电位写回第二膜电位存储器。

[0040]

可选地,所述学习模块采用8bit随机数生成电路;

[0041]

所述8bit随机数生成电路包括第一寄存器至第八寄存器,第一选择器至第八选择器,以及第一异或门至第四异或门;

[0042]

第一选择器的第一输入端与初始化种子相连,第一选择器的第二输入端与第一寄存器的输出端相连,第一选择器的控制端与是否下载初始化种子相连,第一选择器的输出连接到第八寄存器的输入端,第八寄存器的输出和第一寄存器的输出通过第一异或门连接到第二选择器的第二输入端,第二选择器的第一输入端与初始化种子连接,第二选择器的控制端与是否下载初始化种子(来自tile的复位信号)相连,第二选择器的输出端连接到第七寄存器的输入端,第七寄存器的输出端连接到第三选择器的第二输入端,第三选择器的第一输入端与初始化种子相连,第三选择器的控制端与是否下载初始化种子相连,第三选择器的输出端连接到第六寄存器的输入端,第六寄存器的输出端与第一寄存器的输入端通过第二异或门与第四选择器的第二输入端相连,第四选择器的第一输入端与初始化种子相连,第四选择器的控制端与是否下载初始化种子相连,第四选择器的输出端连接到第五寄存器的输入端,第五寄存器的输出端与第一寄存器的输出端通过第三异或门与第五选择器的第二输入端相连,第五选择器的第一输入端与初始化种子相连,第五选择器的控制端与是否下载初始化种子相连,第五选择器的输出端与第四寄存器的输入端相连,第四寄存器的输出端与第一寄存器的输出端通过第四异或门与第六选择器的第二输入端相连,第六选择器的第一输入端与初始化种子相连,第六选择器的控制端与是否下载初始化种子相连,第六选择器的输出端与第三寄存器相连,第三寄存器的输出端与第七选择器的第二输入端相连,第一输入端与初始化种子相连,第七选择器的控制端与是否下载初始化种子相连,第七选择器的输出端与第二寄存器的输入端相连,第二寄存器的输出端与第八选择器的第二输入端相连,第八选择器的第一输入端与初始化种子相连,第八选择器的控制端与是否下载初始化种子相连,第八选择器的输出端与第一寄存器的输入端相连;每个寄存器的输出端将会生成1bit数据,8个寄存器的输出端即生成8bit的随机数r。

[0043]

可续地,所述tempotron层的权重的更新采用低8bit随机权重更新,根据权重更新公式计算得到16bit的δω,将其超出8bit更新精度的部分作为概率p,再用8bit随机数生成电路生成8bit的随机数r,若p≥0且p≥r,则将超出8bit更新精度的部分进位为1,若p≥0且p《r,则将超出8bit更新精度的部分舍去;若p≤0且|p|≥r,则将超出8bit更新精度的部分进位为-1,若p≤0且p《r,则将超出8bit更新精度的部分舍去;

[0044]

其中,权重更新公式如下:

[0045][0046]

其中:λ是学习率,ti是突触前脉冲到达第i个突触的时间,t

max

是突触后神经元膜电位达到最大值的时间,k(t

max-ti)表示psp核。

[0047]

本发明具有以下优点:

[0048]

(1)对压缩感知层和tempotron算法的改进,网络识别率有着明显的提升,提高了计算效率,易于硬件实现。

[0049]

(2)提出的片上学习的轻量级snn网络的高效fpga硬件框架,能够在资源消耗最

少、成本最低的同时,最大限度提高并行处理速度,适用于成本低、功耗低、实时性要求高的边缘和移动终端场景。

[0050]

(3)所提出的硬件系统架构能够根据需求,对该硬件框架每层的神经元数量等参数进行配置。

附图说明

[0051]

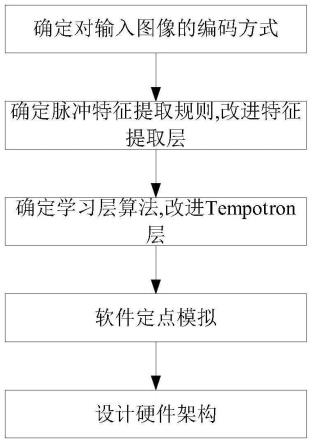

图1是本实施例的流程图;

[0052]

图2是本实施例中compressive-tempotron模型的示意图;

[0053]

图3是本实施例中轻量级片上学习fpga硬件架构示意图;

[0054]

图4是本实施例中第二膜电位更新模块的电路图;

[0055]

图5是本实施例中8bit随机数生成电路的电路图。

具体实施方式

[0056]

以下将结合附图对本发明进行详细的说明。

[0057]

本实施例中,一种轻量级片上学习fpga硬件架构的设计方法,以脉冲神经网络结构为基础,结合压缩感知规则和tempotron算法,构建轻量级脉冲神经网络,压缩感知层直接发射脉冲,并在传统的tempotron算法中加入膜电位和trace协同复位机制,并以事件驱动的方式进行,提高了计算效率,易于硬件实现。针对我们所提出的两层snn网络,设计了采用并行的基于事件驱动的片上学习fpga硬件架构。

[0058]

如图1所示,本实施例中,一种轻量级片上学习fpga硬件架构的设计方法,具体包括以下步骤:

[0059]

步骤一,设计compressive-tempotron两层脉冲神经网络架构、软件定点模拟。

[0060]

步骤1-1,确定对输入图像的编码方式:

[0061]

输入层采用多脉冲时间编码方案将图像的像素转换为脉冲序列。多脉冲时间编码方案采用泄漏累积发射(lif)神经元模型:

[0062]vm

(t)=vm(t-1)+β

×

x

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0063]

其中:t是当前时间步,t-1是上一个时间步,vm是神经元膜电位,x是单个像素点的像素值,β是像素随时间线性增长的增长率。当膜电位累加到预先设定好的阈值时,神经元发射脉冲,并立即回到0,随后再次随着时间线性增长。

[0064]

步骤1-2.确定脉冲特征提取规则,改进特征提取层:

[0065]

压缩感知层从输入层送入的脉冲中提取具有时空信息的脉冲特征。如图(2)所示,在一幅图中,随机选择两个正极性patches,以及两个负极性patches。对于每个patch而言,它由位置、大小和极性三个属性确定。对于一个patch而言,其位置和大小是随机选择的。出于硬件友好型网络,压缩感知层和tempotron层均基于事件驱动。压缩感知层采用具有生物似然性的泄漏累积发射(lif)神经元模型,其膜电位以事件驱动的形式描述为:

[0066][0067]

其中:τm是第一时间衰减常数,t

p

是突触前脉冲到达第p个patch的时间,t

prev

是在当前时间t之前突触前脉冲到达与神经元连接的任一突触的时间,v是突触后神经元的膜电

位,patch的极性值由+1/-1表示,即+1表示patch极性为正,-1表示patch极性为负,s

p

为第p个patch的面积与其极性的乘积。本实施例中相较于以往加入压缩感知层的网络而言,其改进在于,当神经元膜电位的绝对值超过预先设定好的阈值,立即发射脉冲,并恢复至静息值,而不需要在时间窗口内,一直对神经元膜电位进行累加,再对其进行编码,有利于硬件实现。如图(2)所示,根据神经元膜电位的极性,脉冲从未偏移或偏移的地址发射,并以事件驱动(aer)的形式送到下一层。

[0068]

步骤1-3.确定学习层算法,改进tempotron层;

[0069]

在传统的tempotron学习规则中,应用lif神经元模型,突触后神经元的膜电位(v(t))描述为:

[0070][0071]

其中:ti表示突触前脉冲到达第i个突触的时间,ωi为第i个突触的权重,v

rest

是静息值。k(t-ti)是输入脉冲作用于突触后神经元时,归一化的突触后膜电位(psp),即psp核,其定义为:

[0072][0073]

其中:τ为第二时间衰减常数,τs为突触电流时间衰减常数,v0将psp核归一化为1,由此突触后膜电位(psp)的振幅仅仅取决于有输入脉冲的突触的权重ωi。当v(t)超过预先设定的阈值时,突触后神经元发射一个脉冲,之后神经元不再接收任何输入脉冲,膜电位逐渐复位至静息值v

rest

。为使输出神经元可以根据其标签与输入图像标签是否对应而发射脉冲或不发射脉冲,tempotron的学习规则规定为:如果输出神经元的标签与输入图像标签对应,却没有发射脉冲,则增加在t

max

(t

max

是突触后神经元膜电位到达最大值的时间)之前有输入脉冲的突触的权重;如果输出神经元的标签与输入图像标签不对应,却发射了脉冲,则减小在t

max

之前有输入脉冲的突触的权重。权重更新描述为:

[0074][0075]

其中:λ是学习率,ti是第i个输入脉冲到达突触的时间,t

max

是突触后神经元膜电位到达最大值的时间。这意味着在发射脉冲时刻之后的输入脉冲将不再对权重更新有影响。

[0076]

改进tempotron层:

[0077]

在传统tempotron中,突触后神经元仅发射一次脉冲,而stdp学习规则中,突触后神经元可以发射多次脉冲。两种算法的权重更新方式,除了tempotron的权重更新在处理完一张图像的所有输入脉冲后才进行更新外,还有显著的区别。tempotron学习规则中,膜电位达到最大膜电位之后的输入脉冲将不会对权重更新产生影响。而stdp学习规则中,输入脉冲对权重更新始终有着影响,即在突触后神经元发射脉冲,其膜电位复位前的输入脉冲仍然作用于下一次权重更新。

[0078]

然而膜电位复位之前的脉冲,对下一次权重更新的影响,应当与发射脉冲时刻的

膜电位对复位之后的膜电位影响相同,即膜电位与trace的复位协同。基于此,对传统tempotron学习规则进行了改进。在改进的算法中,基于事件驱动的突触后神经元膜电位描述为:

[0079][0080]

其中:τm是时间衰减常数,ti是突触前脉冲到达第i个突触的时间,t

prev

是当前时间t之前到达与突触后神经元相连的任一突触的时间,ωi为第i个突触的权重,v为突触后神经元的膜电位。当神经元膜电位超过预先设定的阈值时,复位至原来的α倍(0≤α《1),随后神经元膜电位继续累加-发射-复位。

[0081]

本实施例中,权重更新方式与传统tempotron相似,不同之处在于我们使用单核psp进行权重更新。本实施例中使用的单核psp描述为:

[0082][0083]

其中:τ为第二时间衰减常数,t

max

为在时间窗口内神经元膜电位达到最大值的时间,ti是第i个输入脉冲到达突触的时间。式(5)中,膜电位达到最大值时的输入脉冲也对权重更新有影响,但由于式(5)中为双核psp,当ti=t

max

时,k(t

max

–

ti)=0。因此ti=t

max

时刻的输入脉冲对权重更新没有影响。而在单核psp中,k(t

max

–

ti)=1,因此ti=t

max

时刻的输入脉冲对权重更新有影响。因此权重更新时,ti应该小于等于t

max

,权重更新描述为:

[0084][0085]

其中:λ是学习率,ti是第i个输入脉冲到达突触的时间,t

max

是突触后神经元膜电位达到最大值的时间。上式会消耗很大的内存空间来存储和访问突触前脉冲时间ti。因此,为了节约硬件资源和提高计算速度,式(8)中的累加项改写为事件驱动的突触trace更新方式:

[0086][0087]

其中:τ为第二时间衰减常数,t

max

为在时间窗口内神经元膜电位达到最大值的时间,t

prev

是当前时间t之前到达与突触后神经元相连的任一突触的时间,qi是第i个突触的突触trace。当神经元接收到一个突触前脉冲时,它的膜电位根据式(6)进行更新,并将突触trace(qi(t))乘上exp(-δti/τ),然后增加1。如果更新后的膜电位大于最大膜电位,则用神经元的当前膜电位更新其最大膜电位,并备份当前的突触trace。当突触后神经元发射脉冲,突触trace与突触后神经元膜电位协同复位至原来的α倍。当处理完一张图的所有事件后,将-λqi(t

max

)或λqi(t

max

)加到突触权重以完成式(8)。

[0088]

将设计好的网络经过训练后,根据发射脉冲数最多的一类神经元组对应的标签来推测测试样本的标签。如果有两类以上的神经元组发射的脉冲数相同,则认为输入样本的

标签未知。

[0089]

步骤1-4、软件定点模拟:通过定点软件仿真,评估compressive-tempotron神经网络在mnist数据集的正确率为95.36%。

[0090]

步骤二、设计硬件架构:将compressive-tempotron神经网络部署在fpga中。

[0091]

如图3所示,本实施例中,一种轻量级片上学习fpga硬件架构,包括全局控制器、压缩感知层和tempotron层;

[0092]

所述全局控制器分别与压缩感知层和tempotron层连接,全局控制器用于控制压缩感知层和tempotron层;

[0093]

所述压缩感知层包括m1个第一tile单元,其中,每个第一tile单元以时间复用的方式对k1个第一神经元进行处理;其中,1≤m1≤64,1≤k1≤8;其中,所述第一tile单元包括第一局部控制器,以及分别与第一局部控制器连接的第一膜电位存储器、第一发射管理模块、第一膜电位更新模块、patch存储器、第一指数查找表存储器和第一前一个事件存储器,所述第一膜电位存储器还分别与第一发射管理模块、第一膜电位更新模块连接,第一发射管理模块与第一膜电位更新模块连接,第一膜电位更新模块分别与patch存储器、第一指数查找表存储器和第一前一个事件存储器连接;

[0094]

所述tempotron层包括m2个第二tile单元,其中,每个第二tile单元以时间复用的方式对k2个第二神经元进行处理;其中,1≤m2≤64,1≤k2≤4;其中,所述第二tile单元包括第二局部控制器,以及分别与第二局部控制器连接的学习模块、备份trace存储器、最大膜电位管理模块、第二发射管理模块、权重存储器、第二膜电位存储器、trace存储器、trace更新模块、第二膜电位更新模块、最大膜电位存储器、第二前一个事件存储器和第二指数查表存储器;所述学习模块还分别与权重存储器、第二发射管理模块和备份trace存储器连接;第二膜电位更新模块还分别与权重存储器、第二膜电位存储器、trace更新模块和第二指数查表存储器连接;第二膜电位存储器还与第二发射管理模块连接;trace更新模块还分别与第二指数查表存储器、第二前一个事件存储器和trace存储器连接;trace存储器与还与第二发射管理模块连接;最大膜电位管理模块还分别与最大膜电位存储器、第二发射管理模块和备份trace存储器连接。

[0095]

本轻量级片上学习fpga硬件架构可以实现对不同网络规模和参数的配置,即压缩感知层的神经元数量、学习率、阈值以及tempotron层的神经元数量、膜电位和trace的复位率、学习率、阈值可以根据不同的需求灵活配置。

[0096]

本实施例中,为了节约硬件资源,对于tempotron层而言,所述tempotron层的权重的更新采用低8bit随机权重更新,根据权重更新公式(8)计算得到16bit的δω,将其超出8bit更新精度的部分作为概率p,再用8bit随机数生成电路生成8bit的随机数r,若p≥0且p≥r,则将超出8bit更新精度的部分进位为1,若p≥0且p《r,则将超出8bit更新精度的部分舍去;若p≤0且|p|≥r,则将超出8bit更新精度的部分进位为-1,若p≤0且p《r,则将超出8bit更新精度的部分舍去。

[0097]

如图4所示,本实施例中,所述第二膜电位更新模块第一乘法器1和第一加法器2,第一乘法器1和第一加法器2连接。当有脉冲到来时触发膜电位的更新,首先从第二前一个事件存储器中读出t

prev

,将当前时间t减去t

prev

得到时间差δt,通过δt查存储在第二指数查表存储器中的指数查找表得到指数衰减系数,查找到的指数衰减系数和从第二膜电位存

储器读取的当前神经元的膜电位,作为第一乘法器1的输入,得到第一乘法器1的输出,即经过衰减的膜电位,衰减后的膜电位和从权重存储器中读取的当前神经元的脉冲到达的突触的权重作为第一加法器2的输入,得到第一加法器2的输出,即更新后的膜电位v(t),并将更新后的膜电位写回第二膜电位存储器。

[0098]

本实施例中,对于压缩感知层中各第一tile单元的第一膜电位更新模块而言,与第二膜电位更新模块的硬件电路不同之处在于需要根据事件是否在神经元patch内,决定是否执行膜电位更新。

[0099]

如图5所示,本实施例中,所述学习模块采用8bit随机数生成电路;

[0100]

所述8bit随机数生成电路包括第一寄存器至第八寄存器,第一选择器至第八选择器,以及第一异或门至第四异或门;

[0101]

第一选择器3的第一输入端与初始化种子(初始化种子直接给的值1)相连,第一选择器3的第二输入端与第一寄存器15的输出端相连,第一选择器3的控制端与是否下载初始化种子相连,第一选择器3的输出连接到第八寄存器22的输入端,第八寄存器22的输出和第一寄存器15的输出通过第一异或门4连接到第二选择器5的第二输入端,第二选择器5的第一输入端与初始化种子连接,第二选择器5的控制端与是否下载初始化种子(来自tile的复位信号)相连,第二选择器5的输出端连接到第七寄存器21的输入端,第七寄存器21的输出端连接到第三选择器6的第二输入端,第三选择器6的第一输入端与初始化种子相连,第三选择器6的控制端与是否下载初始化种子相连,第三选择器6的输出端连接到第六寄存器20的输入端,第六寄存器20的输出端与第一寄存器15的输入端通过第二异或门7与第四选择器8的第二输入端相连,第四选择器8的第一输入端与初始化种子相连,第四选择器8的控制端与是否下载初始化种子相连,第四选择器8的输出端连接到第五寄存器19的输入端,第五寄存器19的输出端与第一寄存器15的输出端通过第三异或门9与第五选择器10的第二输入端相连,第五选择器10的第一输入端与初始化种子相连,第五选择器10的控制端与是否下载初始化种子相连,第五选择器10的输出端与第四寄存器18的输入端相连,第四寄存器18的输出端与第一寄存器15的输出端通过第四异或门11与第六选择器12的第二输入端相连,第六选择器12的第一输入端与初始化种子相连,第六选择器12的控制端与是否下载初始化种子相连,第六选择器12的输出端与第三寄存器17相连,第三寄存器17的输出端与第七选择器13的第二输入端相连,第一输入端与初始化种子相连,第七选择器13的控制端与是否下载初始化种子相连,第七选择器13的输出端与第二寄存器16的输入端相连,第二寄存器16的输出端与第八选择器14的第二输入端相连,第八选择器14的第一输入端与初始化种子相连,第八选择器14的控制端与是否下载初始化种子相连,第八选择器14的输出端与第一寄存器15的输入端相连;每个寄存器的输出端将会生成1bit数据,8个寄存器的输出端即生成8bit的随机数r。

[0102]

在基于对以往压缩感知规则和传统tempotron算法的改进上,提出了片上学习的轻量级snn网络的高效fpga硬件框架和电路。其中,硬件系统采用基于事件驱动的流水线架构,显著提高了计算速度,并加入了低8bit随机权重更新以及突触trace更新机制,大大降低了硬件资源消耗。基于以上特点,该硬件系统易于集成到成本和功耗有限的边缘或移动终端设备中。

[0103]

上述实施例为本发明较佳的实施方式,但本发明的实施方式并不受上述实施例的

限制,其他的任何未背离本发明的精神实质与原理下所作的改变、修饰、替代、组合、简化,均应为等效的置换方式,都包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1