一种处理器内部存储访问结构及访问方法与流程

1.本发明属于处理器内部结构技术领域,具体地说,是涉及一种处理器内部存储访问结构及访问方法。

背景技术:

2.对处理器内部存储的访问,现有技术中通常使用冯诺依曼结构或哈弗结构对处理器内部存储进行访问。

3.冯诺依曼结构下,使用单总线对内部存储进行访问,整个过程不能并行进行,效率不高;哈弗结构下,使用指令总线和数据总线并行对指令区和数据区进行访问,但对数据区的访问不能并行进行,且内存不能直接被外部设备访问。

4.而对处理器内部存储访问的效率直接影响soc的系统性能。

技术实现要素:

5.本发明提出一种处理器内部存储访问结构及访问方法,在多总线结构的基础上对处理器的内部存储进行分区以减少访问冲突的发生,同时配合仲裁,实现提高访问效率的技术效果。

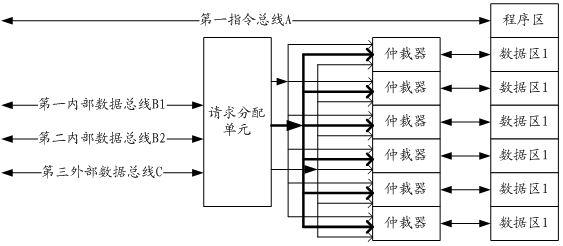

6.本发明采用以下技术方案予以实现:提出一种处理器内部存储访问结构,包括:程序区,处理器的内部取指单元通过第一指令总线对其进行访问;多个数据区,可由处理器的执行单元和外部设备共同访问;请求分配单元,对第一内部数据总线、第二内部数据总线和第三外部数据总线的访问请求的地址信息进行译码,将访问请求映射到对应的数据区;其中,第一内部数据总线和第二内部数据总线为处理器执行指令过程中,内部执行单元访问数据区时使用的总线;第三外部数据总线为外部设备访问数据区时使用的总线;多个仲裁器,一个仲裁器位于所述请求分配单元与一个数据区之间,对第一内部数据总线、第二内部数据总线和第三外部数据总线对同一数据区的访问请求进行仲裁,获得仲裁权的访问优先对数据区进行访问;其中,仲裁器的仲裁规则包括:第一内部数据总线和第二内部数据总线同时访问同一数据区时,第一内部数据总线获得优先权发出请求,在第一内部数据总线请求完成后,第二内部数据总线获得优先权;在第一内部数据总线和第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第一内部数据总线获得优先权;在第二内部数据总线和第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第二内部数据总线获得优先权;

在第一内部数据总线、第二内部数据总线、第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第一内部数据总线获得优先权发出请求,在第一内部数据总线请求完成后,第二内部数据总线获得优先权。

7.提出一种处理器内部存储访问方法,应用于如上所述的处理器内部存储访问结构中,包括:请求分配单元对来自于第一内部数据总线、第二内部数据总线和第三外部数据总线的访问请求的地址信息进行译码,根据译码结果将访问请求映射到对应的数据区;当对同一数据区的访问请求多于一个时,数据区对应的仲裁器对访问请求进行仲裁,获得仲裁权的访问优先对数据区进行访问;其中,所述仲裁器的仲裁规则包括:第一内部数据总线和第二内部数据总线同时访问同一数据区时,第一内部数据总线获得优先权发出请求,在第一内部数据总线请求完成后,第二内部数据总线获得优先权;在第一内部数据总线和第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第一内部数据总线获得优先权;在第二内部数据总线和第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第二内部数据总线获得优先权;在第一内部数据总线、第二内部数据总线、第三外部数据总线同时访问同一数据区时,第三外部数据总线获得优先权发出请求,在第三外部数据总线请求完成后,第一内部数据总线获得优先权发出请求,在第一内部数据总线请求完成后,第二内部数据总线获得优先权。

8.与现有技术相比,本发明的优点和积极效果是:本发明提出的处理器内部存储访问结构及访问方法中,根据访问内部存储的主控单元的需求,利用多总线结构对处理器的内部存储进行访问,不同主控单元的访问使用不同类型的总线,当不同主控单元访问不同区域时可并行完成访问,当相同主控单元访问不同区域时可并行完成访问,只有当不同主控单元访问相同区域时根据仲裁结构进行访问,可以显著提升存储单元的访问效率,减少访问冲突发生的概率。

9.结合附图阅读本发明实施方式的详细描述后,本发明的其他特点和优点将变得更加清楚。

附图说明

10.图1 为本发明提出的处理器内部存储访问结构的示意;图2为本发明提出的处理器内部存储访问方法的示意。

具体实施方式

11.下面结合附图对本发明的具体实施方式作进一步详细的说明。

12.如图1所示,本发明提出的处理器内部存储访问结构,包括:存储区,处理器的内部取指单元通过第一指令总线a对其进行访问。

13.多个数据区(图示以6个为例),可由处理器的执行单元和外部设备共同访问。

14.请求分配单元,对第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c的访问请求的地址信息进行译码,将访问请求映射到对应的数据区;其中,第一内部数据总线b1和第二内部数据总线b2为处理器执行指令过程中,内部执行单元访问数据区时使用的总线,为内部总线;第三外部数据总线c为外部设备访问数据区时使用的总线,为外部总线。

15.多个仲裁器,一个仲裁器位于请求分配单元与一个数据区之间,对第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c对同一数据区的访问请求进行仲裁,获得仲裁权的访问优先对数据区进行访问。

16.上述,仲裁器的仲裁规则包括:1、第一内部数据总线b1和第二内部数据总线b2同时访问同一数据区时,按照第一内部数据总线b1的优先权高于第二内部数据总线b2的原则,先由第一内部数据总线b1发出请求,第二内部数据总线b2暂停,在第一内部数据总线b1请求完成后,第二内部数据总线b2获得优先权;期间,新到高优先级请求不影响第二内部数据总线b2的请求,新请求将进行下一轮仲裁。

17.2、在第一内部数据总线b1和第三外部数据总线c同时访问同一数据区时,按照第三外部数据总线c的优先权高于第一内部数据总线b1的原则,先由第三外部数据总线c发出请求,第一内部数据总线b1暂停,在第三外部数据总线c请求完成后,第一内部数据总线b1获得优先权;期间,新到高优先级请求不影响第一内部数据总线b1的请求,新请求将进行下一轮仲裁。

18.3、在第二内部数据总线b2和第三外部数据总线c同时访问同一数据区时,按照第三外部数据总线c的优先权高于第二内部数据总线b2的原则,先由第三外部数据总线c发出请求,第二内部数据总线b2暂停,在第三外部数据总线c请求完成后,第二内部数据总线b2获得优先权;期间,新到高优先级请求不影响第二内部数据总线b2的请求,新请求将进行下一轮仲裁。

19.4、在第一内部数据总线b1、第二内部数据总线b2、第三外部数据总线c同时访问同一数据区时,按照第三外部数据总线c的优先权高于第一内部数据总线b1和第二内部数据总线b2的原则,先将第三外部数据总线c的请求发出,第一内部数据总线b1和第二内部数据总线b2暂停,在第三外部数据总线c请求完成后,第一内部数据总线b1获得优先权发出请求,暂停第二内部数据总线b2,在第一内部数据总线b1请求完成后,第二内部数据总线b2获得优先权;在第一内部数据总线b1、第二内部数据总线b2、第三外部数据总线c的请求全部完成之前,新到高优先级请求不影响本轮仲裁结果,新请求将进行下一轮仲裁。

20.上述本发明提出的处理器内部存储访问结构,1)处理器的内部取指单元通过单独的第一指令总线对其进行访问,三条数据总线可实现对数据的并行访问,从而可保证指令访问、数据访问的并行化;2)三条数据总线中,处理器的执行单元可通过两条数据总线对不同数据区进行访问,外部设备可通过第三外部数据总线对数据区进行访问,从而可实现内部总线、外部总线对不同数据区访问的并行化;3)处理器的执行单元可通过第一内部数据总线和第二内部数据总线对不同数据区访问的并行化;4)多个数据区的划分可以进一步减少发生仲裁的概率;5)仲裁器的结构相同,使得硬件设计可以进行复制,减小设计的复杂

度。

21.基于上述本发明提出的处理器内部存储访问结构,本发明提出相应的处理器内部存储访问方法,如图2所示,包括:s1、请求分配单元对来自于第一内部数据总线、第二内部数据总线和第三外部数据总线的访问请求的地址信息进行译码,根据译码结果将访问请求映射到对应的数据区。

22.s2、当对同一数据区的访问请求多于一个时,数据区对应的仲裁器对访问请求进行仲裁,获得仲裁权的访问优先对数据区进行访问。

23.分为以下情况:1、第一内部数据总线b1和第三外部数据总线c同时发起对内部存储中相同数据区的访问,第二内部数据总线b2访问其他数据区,此时,第一内部数据总线b1、第三外部数据总线c按照仲裁规则进行仲裁,获得优先权的访问优先进行,第二内部数据总线b2和第一指令总线a的访问不受影响。

24.2、第二内部数据总线b2和第三外部数据总线c同时发起对内部存储中相同数据区的访问,第一内部数据总线c1访问其他数据区,此时,第二内部数据总线b2、第三外部数据总线c按照仲裁规则进行仲裁,获得优先权的访问优先进行,第一内部数据总线b1和第一指令总线a的访问不受影响。

25.3、第一内部数据总线b1和第二内部数据总线b2同时发起对内部存储中相同数据区的访问,第三外部数据总线c访问其他数据区,此时,第一内部数据总线b1、第二内部数据总线b2按照仲裁规则进行仲裁,获得优先权的访问优先进行,第三外部数据总线c和第一指令总线a的访问不受影响。

26.4、第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c同时发起访问,且第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c访问相同数据区,此时,第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c按照仲裁规则进行仲裁,获得优先权的访问优先进行,此时,第一指令总线a的访问不受影响。

27.处于需要仲裁的数据访问情况,基于本发明给出的处理器内部存储访问结构,并行化访问的情况包括:1、第一指令总线a和第一内部数据总线b1同时发起对内部存储的访问,此时,第一指令总线a、第一内部数据总线b1互不影响,访问并行进行。

28.2、第一指令总线a和第二内部数据总线b2同时发起对内部存储的访问,此时,第一指令总线a、第二内部数据总线b2互不影响,访问并行进行。

29.3、第一指令总线a和第三外部数据总线c同时发起对内部存储的访问,此时,第一指令总线a、第三外部数据总线c互不影响,访问并行进行。

30.4、第一内部数据总线b1和第三外部数据总线c同时发起对内部存储的访问,此时,第一内部数据总线b1、第三外部数据总线c互不影响,访问并行进行。

31.5、第二内部数据总线b2和第三外部数据总线c同时发起对内部存储的访问,此时,第二内部数据总线b2、第三外部数据总线c互不影响,访问并行进行。

32.6、第一内部数据总线b1和第二内部数据总线b2同时发起对内部存储的访问,此时,第一内部数据总线b1、第二内部数据总线b2互不影响,访问并行进行。

33.7、第一指令总线a、第一内部数据总线b1、第二内部数据总线b2同时发起访问,且

第一内部数据总线b1和第二内部数据总线b2访问不同数据区时,第一指令总线a、第一内部数据总线b1和第二内部数据总线b2互不影响,访问并行进行。

34.8、第一指令总线a、第一内部数据总线b1、第三外部数据总线c同时发起访问,且第一内部数据总线b1和第三外部数据总线c访问不同数据区时,第一指令总线a、第一内部数据总线b1和第三外部数据总线c互不影响,访问并行进行。

35.9、第一指令总线a、第二内部数据总线b2、第三外部数据总线c同时发起访问,且第二内部数据总线b2和第三外部数据总线c访问不同数据区时,第一指令总线a、第二内部数据总线b2和第三外部数据总线c互不影响,访问并行进行。

36.10、第一指令总线a、第一内部数据总线b1、第二内部数据总线b2、第三外部数据总线c同时发起访问,且第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c访问不同数据区时,第一指令总线a、第一内部数据总线b1、第二内部数据总线b2和第三外部数据总线c互不影响,访问并行进行。

37.综上所述,第一指令总线a的访问始终独立进行不受影响;处理器内部总线:第一内部数据总线b1和第二内部数据总线b2,以及外部总线:第三外部数据总线c,只有同时访问同一数据区或其中两条总线同时访问同一数据区时,才会发生仲裁,因此,基于本发明给出的处理器内部存储访问结构的多总线访问结构,可以提升内存的访问效率,减少访问冲突发生的概率。

38.应该指出的是,上述说明并非是对本发明的限制,本发明也并不仅限于上述举例,本技术领域的普通技术人员在本发明的实质范围内所做出的变化、改型、添加或替换,也应属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1