一种基于VPX标准的动态可重构多核心异构数字信号处理硬件系统

一种基于vpx标准的动态可重构多核心异构数字信号处理硬件系统

技术领域

1.本发明涉及高速高可靠数字信号处理系统设计领域。

背景技术:

2.现代机载数字信号处理系统的典型特点是输入数据多、工作模式复杂、信号处理量大。因此在一个实时数字信号处理系统中,要多个处理器并行工作,且同时进行高速数据分配和大数据量的交互,上一代的信号处理硬件系统难以满足实时处理、以及空天机载环境下电子系统高可靠性和故障容错故障自修复的要求。随着大规模集成电路技术、高速并行处理及各种先进算法的飞速发展,利用高速dsp和fpga芯片来构建一个并行处理系统已成为趋势。而设计高性能的信号处理系统具有一定的难度,需要较长的研发周期及相当的开发经费。所以,缩短开发周期、降低成本的最佳途径是研发标准模块、建立通用、可拓展、支持动态重构的高可靠性信号处理平台。

技术实现要素:

3.针对上一代的信号处理模块数据传输效率低、通用性低、扩展性不足、容错能力低等问题,本发明以当前机载数字信号处理系统为应用背景设计出一款基于vpx标准的动态可重构多核心异构数字信号处理硬件系统,该系统相对于其他系统具有运算能力高、存储空间大、外部高速接口丰富、兼容性强、易于开发、抗恶劣环境性和可靠性高等特点。该硬件系统主要用于对基于vpx总线标准的背板传输过来的数据进行接收,经过运算得到实时处理的结果并进行输出。并且该硬件系统支持在线动态重构、远程加载、故障状态监控及故障自修复功能。

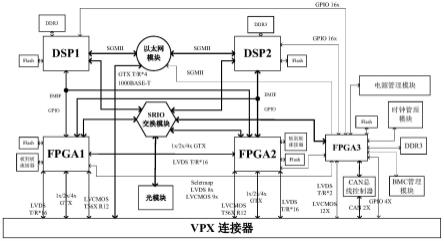

4.本发明涉及一种基于vpx标准的多核心异构数字信号处理硬件系统,该系统主要包括fpga处理器模块、dsp处理器模块、vpx连接器、srio交换模块、以太网模块、光模块、电源管理模块、时钟管理模块、存储模块、bmc管理模块、can总线控制器、板到板连接模块;其中fpga处理器模块包含3个fpga:fpga1、fpga2、fpga3;dsp处理器模块包含两个dsp:dsp1、dsp2;存储模块包含flash模块、ddr3模块;所述vpx连接器分别连接:fpga1、以太网模块、fpga2、fpga3、can总线控制器;fpga1、fpga2、dsp1之间相互连接,fpga1、fpga2之间相互连接,fpga1、fpga2、dsp2之间相互连接,fpga1、fpga2、fpga3、dsp1、dsp2都连接srio交换模块;dsp1、dsp2都与以太网模块连接,fpga3还要单独连接以太网模块、can总线控制器、bmc管理模块、时钟管理模块、电源管理模块、dsp1、dsp2、fpga1、fpga2;所述dsp1、dsp2、fpga3都设置有对应的flash模块、ddr3模块,fpga1、fpga2都设置有对应的flash模块、板到板连接器。

5.进一步的,所述fpga1、fpga2分别通过lvds、gtx、lvcmos连接vpx连接器,以太网模块通过gtx连接vpx连接器,fpga3通过lvcmos、can、gpio连接vpx连接器;

6.dsp1通过emif总线分别与fpga1、fpga2互连;

7.dsp2通过emif总线分别与fpga1、fpga2互连;

8.fpga1与fpga2之间通过16组lvds接口收发互连,和1组4x gtx高速传输接口互联;

9.fpcga1、fpca2均对vpx接口提供16组lvds接口收发、1组4x gtx接口高速传输、56发12收lvcmos接口相连;

10.fpga1通过12对lvds接口和36位lvcmos接口与板到板连接器相连;

11.fpga2通过12对lvds接口和36位lvcmos接口与板到板连接器相连;

12.fpga1、fpga2、fpga3分别通过两组4x接口接入srio交换模块;

13.dsp1、dsp2分别以1组4x srio接口接入srio交换模块;

14.srio交换芯片提供4组4x srio接口与光模块连接;

15.fpga3通过一组sgmii接口接入以太网模块;

16.dsp1、dsp2分别1组sgmii接口接入以太网模块;

17.以太网模块提供1组1000base-t接口和4组sgmii对外接口连接vpx接口模块;

18.can总线控制器与fpga3和vpx连接器相连;

19.时钟管理模块为系统各模块提供时钟,并受fpga3控制时钟分配;

20.电源管理模块受fpga3控制电源开断;

21.fpga3以selectmap接口、8对lvds接口和9个lvcoms接口与fpga1、fpga2相连;

22.fpga3通过gpio接口与spi接口与dsp1、dsp2相连;

23.fpga1、fpga2、fpga3、dsp1、dsp2分别连接一flash模块;dsp1、dsp2和fpga3分别连接一ddr3模块;

24.fpga1、fpga2接口相同,管脚分配一致;dsp1、dsp2接口相同,管脚分配一致。

25.本发明实现异构并行信号运算及处理,外部数据可通过vpx连接器,以太网模块或光模块传输至fpga处理器模块、dsp处理器模块进行运算,针对算力要求高的应用数据可使用dsp进行运算,针对具有算法硬件可编程的应用数据可使用fpga进行运算,同时板到板连接模块可支持板载扩展。本发明为现代机载高速数字信号处理系统提供一种设计方案。

附图说明

26.图1为本发明系统连接结构图。

具体实施方式

27.本发明涉及一种基于vpx标准的多核心异构数字信号处理硬件系统,该系统主要包括fpga处理器模块、dsp处理器模块、vpx连接器、srio交换模块、以太网模块、光模块、电源管理模块、时钟管理模块、存储模块、bmc管理模块、can控制器模块、板到板连接模块。其中fpga处理器模块包含3个fpga:fpga1、fpga2、fpga3;dsp处理器模块包含两个dsp:dsp1、dsp2;存储模块包含flash模块、ddr3模块。外部主机可通过vpx连接器、以太网模块、光模块对fpga处理器模块、dsp处理器模块进行访问。fpga处理器模块和dsp处理器模块之间可通过srio交换模块进行串行高速数据通信。该系统可实现异构并行信号运算及处理,外部数据可通过vpx连接器,以太网模块或光模块传输至fpga处理器模块、dsp处理器模块进行运算,针对算力要求高的应用数据可使用dsp进行运算,针对具有算法硬件可编程的应用数据可使用fpga进行运算,同时板到板连接模块可支持板载扩展。本发明为现代机载高速数字

信号处理系统提供一种设计方案。

28.主要功能特征:

29.(1)在线升级功能

30.a)fpga1及fpga2具备经srio总线完成程序的在线升级功能:

31.b)dsp1及dsp2具备经srio总线完成程序的在线升级功能;

32.c)fpga3具备通过以太网接收fpga1、fpga2、fpga3的在线升级程序,并能完成三个fpga的在线升级功能;

33.d)dsp1和dsp2通过以太网接收各自芯片的在线升级程序,并完成各自芯片的在线升级功能。

34.(2)远程加载功能

35.a)fpga3具备通过以太网接收fpga1、fpga2的运行文件程序,并能完成fpga1、fpga2的远程加载;

36.b)dsp1和dsp2通过以太网接收各自芯片的运行文件程序,完成各自芯片的远程加载。

37.(3)srio交换功能

38.系统具备rio交换功能,rapidio互联标准为v2.1,速率5gbps,模块采用4x交换,

39.具体连接如下:

40.a)fpga1、fpga2、fpga3分别两组4x srio接口接入交换芯片;

41.b)dsp1、dsp2分别1组4x srio接口接入交换芯片;

42.c)交换芯片提供4组4x srio对外光交换接口;

43.d)fpga1、2和dsp1、2及交换芯片具备rio动态入网能力。

44.(4)以太网交换功能

45.模块具备以太网交换功能,具有100/1000base mbps自适应功能,具体连接如下:

46.a)fpga3一组sgmii接口接入交换芯片;

47.b)dsp1、dsp2分别1组sgmii接口接入交换芯片;

48.c)交换芯片提供1组1000base-t对外接口;

49.d)交换芯片提供4组sgmii对外接口。

50.(5)低功耗模式可配置功能

51.fpga3收到can总线下发的控制命令后,可对板内芯片进行功耗控制,可以使其分别处于休眠模式,以节约功耗。具体操作如下:

52.a)在低功耗模式下,fpga3通过控制时钟分配电路对fpga1、fpga2切断工作时钟;

[0053][0054]

b)在低功耗模式下,fpga3通过控制时钟分配电路对dsp1、dsp2切断工作时钟;

[0055]

c)在低功耗模式下,fpga3对dsp1、dsp2复位;

[0056]

d)在低功耗模式下,fpga3对rio交换芯片复位。

[0057]

(6)复位功能

[0058]

a)模块具有硬复位接口,复位接口采用地/开信号,当fpga3接收到外部超过500ms

[0059]

低电平信号时,对整板进行硬复位,地/开信号需要进行去抖处理;

[0060]

b)fpga3能够接收到can总线的复位指令,对dsp1、dsp2、fpga1、fpga2、分别或者统

一进行复位;

[0061]

c)dsp1、dsp2提供软复位接口,用于软件实现软复位。

[0062]

(7)时钟关断功能:

[0063]

a)fpga3能够通过控制时钟管理模块对fpga1、fpga2的100mhz时钟分别关断;分别关断;

[0064]

b)fpga3能够通过控制时钟管理模块对fpga1、fpga2的32.512mhz时钟分别关断。

[0065]

c)fpga3能够通过控制时钟管理模块对dsp1、dsp2的50mhz时钟分别关关断。

[0066]

(8)时钟切换功能要求

[0067]

a)模块上电启动时,模块全部时钟默认使用内部本地时钟;

[0068]

b)fpga3能接收到外部地/开信号,当接收到外部超过500ms低电平信号时,时钟管理模块使系统的100mhz内部时钟切换为外部时钟,地/开信号需做去抖处理;

[0069]

(9)健康管理功能

[0070]

a)bmc模块自身能够采集温度、电压等信息,并能通过can总线进行上报;

[0071]

b)bmc模块具备过温保护功能,模块的各温度点门限可设,当超过门限值时,模块能提示告警,并对过温芯片进行保护;

[0072]

c)bmc模块具备过压保护功能,模块的各电压点门限可设,当超过门限值时,模块能提示告警,并对过压芯片进行保护:

[0073]

d)bmc模块自身具备上电自检、周期自检、维护自检、状态信息、故障日志等上报和记录功能。

[0074]

芯片及接口实现:

[0075]

(1)dsp选型及技术指标

[0076]

a)型号:tms320c6678,兼容国产化芯片ft-m6678;

[0077]

b)主频:1ghz;

[0078]

c)运算模式:32bit、默认为big endian模式,可配置为little endian模式;

[0079]

d)输入时钟:50mhz;

[0080]

e)ddr3:≥4gb,位宽64bit;工作频率不低于533mhz;

[0081]

f)flash:不小于64mb,最大支持8个程序版本存储,每个程序空间8mb,flash

[0082]

高位3根地址线连接至fpga3用于程序切换,硬件设计兼容128m容量flash。

[0083]

(2)fpga1和fpga2选型及技术指标

[0084]

a)型号:xc7k325t-2ffg900,兼容国产化芯片jfm7k325t;

[0085]

b)bpi flash:2256mb,16bit位宽,支持8个程序版本存储,每个程序空间16mb,将bpi flash的高3位地址线,连接至fpga3,用于程序切换,程序加载方式采用异步加载模式。

[0086]

(3)fpga3选型及技术指标

[0087]

a)型号:xc7z045-2ffg900i,兼容国产化芯片fmql45t900;

[0088]

b)qspi flash:2128mb,支持8个程序版本存储,每个程序空间16mb.

[0089]

(4)rio交换芯片选型及设计要求

[0090]

a)型号:80hcps1848,兼容国产化芯片nms1800;

[0091]

b)模式:4x;

[0092]

c)传输速率:线速率5gbps;

[0093]

(4)光电转换模块要求

[0094]

a)工作波长:850nm;

[0095]

b)单通道传输速率:10.3125gbps;

[0096]

c)型号:htg8503-mh-t001yy。

[0097]

(5)时钟设计

[0098]

模块时钟分为内部本地时钟和外部输入时钟,具体时钟设计要求如下:

[0099]

外部输入时钟:

[0100]

a)时钟分配电路接收外部32.512mhz高稳定度mlvds时钟,并能将该时钟通过lvds分发给fpga1、fpga2;

[0101]

b)时钟分配电路接收外部100mhz高稳定度mlvds时钟,并能将该时钟通过lvds分发给fpga1、fpga2、fpga3、dsp1、dsp2;

[0102]

内部本地时钟:

[0103]

a)模块内部具备50mhz时钟,直接分发给fpga3;

[0104]

b)模块内部具备100mhz时钟,通过时钟分配电路分发给fpga1、fpga2;

[0105]

c)模块内部具备100mhz时钟,通过时钟分配电路转化为50mhz时钟,分发给dsp1、dsp2、can总线控制器;

[0106]

d)模块内部的fpga1、fpga2、dsp1、dsp2的rio端口以及rio交换芯片时钟统一采用156.25mhz高精度时钟,时钟稳定度不少于30ppm;

[0107]

e)以太网交换心斤米用25mhz高精度时钟,时钟稳足度个少于30ppm;

[0108]

接口设计:

[0109]

(1)光模块光纤接口:

[0110]

a)传输速率:线速率5gbps;

[0111]

b)模式:4x;

[0112]

c)总线协议标准:rapidio互连规范v2.1;

[0113]

d)数量:交换芯片对外提供4路4x rapidio光纤接口;

[0114]

e)光波长:850nm;.

[0115]

f)光纤类型:多模光纤;

[0116]

g)有效传输带宽:单路4x不少于14gbps;双路4x同时传输不少于28gbpsi

[0117]

(2)gtx接口

[0118]

a)传输速率:线速率2.5gbps,5gbps可配,5gbps默认速率;

[0119]

b)模式:1x,2x,4x可配;

[0120]

c)传输协议:aurora;.

[0121]

d)数量:4,fpga1、fpga2分别对外出1组;fpga1、fpga2互联1组;

[0122]

(3)1000base-t接口

[0123]

a)传输速率:100/1000mbps自适应;

[0124]

b)数量:1组;

[0125]

c)总线协议标准:ieee 802.3标准。

[0126]

(4)sgmii接口

[0127]

a)传输速率:线速率1.25gbps;

[0128]

b)数量:4组;

[0129]

c)总线协议标准:ieee 802.3标准。

[0130]

(5)lvds接口

[0131]

a)接口电气特性遵循:tiaeia-644lvds规范;

[0132]

b)芯片选型:与max9122、9123兼容的国产化芯片;

[0133]

c)传输内容:异步串口以及离散接口;

[0134]

d)速率:≤500mbps;

[0135]

e)lrm连接器定义的lvds差分信号经buffer后以单端形式连接到fpga;

[0136]

(6)lvcmos离散控制线接口

[0137]

a)信号电平:lvcmos电平3.3v;

[0138]

b)驱动能力:212ma;

[0139]

c)传输内容:高实时要求控制信号;

[0140]

d)对输入的lvcmos信号,需要预留上下拉电阻,硬件上按上拉装配:。

[0141]

(7)rs232接口

[0142]

a)连接芯片:dsp1、dsp2、fpga3;

[0143]

b)数量:4组,每组分叉至调试连接器和背板连接器;

[0144]

c)芯片选型:与max3232兼容的国产化芯片sm3232;

[0145]

d)传输内容:调试串口。

[0146]

(8)can总线

[0147]

a)总线协议标准:can总线2.0通用设计规范,兼容iso11898 can总线标准;

[0148]

b)数量:2路;

[0149]

c)芯片选型:与sn65hvd230兼容的国产化芯片sm65hvd230d;

[0150]

d)速率:≤1mbps.

[0151]

(9)jtag接口

[0152]

a)接口类型:调试接口;

[0153]

b)数量:5(fpga1、fpga2、fpga3、dsp1、dsp2各一组)。

[0154]

(10)rapidio接口

[0155]

a)传输速率:线速率5gbps;

[0156]

b)模式:4x;

[0157]

c)总线协议标准:rapidio互连规范v2.1;

[0158]

d)数量:6组;

[0159]

e)dsp有效传输带宽:不少于12gbps;fpga有效传输带宽:单路4x不少于14gbps;双路4xx同时传输不少于28gbps.

[0160]

(11)emif接口

[0161]

a)总线位宽:16bit;

[0162]

b)工作模式:bigendian模式,支持异步与同步两种工作模式,dma通信保证不低于100mbps;

[0163]

c)互连关系:dsp1的emif总线分别与fpga1、fpga2相连;dsp2的emif总线分别与fpga1、fpga2相连。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1