高层次综合的流程布局方法

1.本发明涉及电路仿真技术领域,尤其涉及一种高层次综合的流程布局方法。

背景技术:

2.高层次综合(high-level synthesis,hls),指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。hls工具具有高效快速的特点,能够减少硬件工程师设计的时间,同时也让软件工程师完成硬件设计。

3.但是,在相关技术方案中,hls设计与手工设计的质量存在差距的一大原因是难以在hls层面上准确地估计互联延迟,难以得到较好的全局物理布局。特别是在现场可编程逻辑门阵列(field programmable gate array,fpga)布局布线中,物理综合器往往会使用距离较近的资源,带来布局布线的拥塞,增加整体的布线长度,进而降低电路的吞吐量。此外,fpga的资源以可编程逻辑块(configurable logic block,clb)的形式排布,不同block的资源情况可能不同,当忽略边界跨越block进行互联时,容易带来更长的布线和延时。

技术实现要素:

4.有鉴于此,为至少部分解决上述技术问题或者缺陷之一,本发明实施例的目的在于提供一种能够有效减少布线布局拥塞,降低时延的高层次综合的流程布局方法。

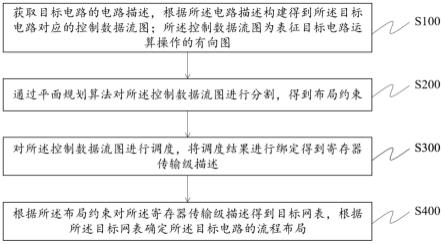

5.本技术技术方案提供了高层次综合的流程布局方法,包括以下步骤:

6.获取目标电路的电路描述,根据所述电路描述构建得到所述目标电路对应的控制数据流图;所述控制数据流图为表征目标电路运算操作的有向图;

7.通过平面规划算法对所述控制数据流图进行分割,得到布局约束;

8.对所述控制数据流图进行调度,将调度结果进行绑定得到寄存器传输级描述;

9.根据所述布局约束对所述寄存器传输级描述得到目标网表,根据所述目标网表确定所述目标电路的流程布局。

10.在本技术方案的一种可行的实施例中,所述通过平面规划算法对所述控制数据流图进行分割,得到布局约束,包括:

11.获取所述电路描述中所述目标电路的fpga架构;

12.根据所述控制数据流图中数据流进程对应的函数,进行编译得到寄存器转换级的电路模块;

13.根据所述电路模块对所述fpga架构进行分区,确定分区结果的成本函数;

14.通过对所述fpga架构的分区结果进行分割迭代,确定所述成本函数为最小值或者分区中的资源到达资源约束的临界值,输出得到所述布局约束。

15.在本技术方案的一种可行的实施例中,所述对所述控制数据流图进行调度,将调度结果进行绑定得到寄存器传输级描述,包括:

16.对所述控制数据流图的子图进行调度;

17.对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡;

18.将调度结果以及延迟平衡后的结果进行数学整合,根据数学整合后的结果与所述目标电路进行绑定,得到所述寄存器传输级描述。

19.在本技术方案的一种可行的实施例中,所述布局约束包括时序约束或物理约束中的至少之一;所述目标网表包括综合网表或布局布线网表中的至少之一;所述根据所述布局约束对所述寄存器传输级描述得到目标网表,根据所述目标网表确定所述目标电路的流程布局,包括:

20.根据所述时序约束和/或所述物理约束构建得到第一输入;

21.根据所述寄存器传输级描述构建得到第二输入;

22.通过fpga物理综合器,将所述第一输入以及所述第二输入进行整合处理输出得到综合网表;

23.通过fpga物理综合器,根据所述第一输入以及所述第二输入进行布局布线处理输出得到布局布线网表;

24.根据所述综合网表以及所述布局布线网表确定所述目标电路的流程布局。

25.在本技术方案的一种可行的实施例中,所述成本函数用于表征所述fpga架构的分区边界的导线数量;所述成本函数为:

[0026][0027]

其中,c为成本值,vi以及vj表征所述控制数据流图中的节点,i=1,2,3,

…

n,j=1,2,3,

…

n,n为正整数,e表征节点间fifo通道的集合,e

ij

为vi和vj之间的连接线,row表示行数,col表示列数,width表示数据位宽。

[0028]

在本技术方案的一种可行的实施例中,所述资源约束的表达式如下:

[0029][0030]

其中,vd表示节点v分配的分区空间,v

area

表示节点的所需资源,rv表示当前分区r所容纳的节点集合,(r

child

)

area

表示每个分区中的资源数量。

[0031]

在本技术方案的一种可行的实施例中,所述通过对所述fpga架构的分区结果进行分割迭代,确定所述成本函数为最小值或者分区中的资源到达资源约束的临界值,输出得到所述布局约束,包括:

[0032]

获取所述控制数据流图中节点在分割迭代之前的第一坐标,根据分割方式确定坐标变换关系,根据所述坐标变换关系将所述第一坐标变换得到第二坐标;

[0033]

所述分割方式包括水平方向分割或竖直方向分割。

[0034]

在本技术方案的一种可行的实施例中,所述坐标变换关系的表达式如下:

[0035][0036][0037]

其中,v.row表示第二坐标中的行坐标,v.col表示第二坐标中的列坐标,(v.row)

prev

表示第一坐标中的行坐标,(v.col)

prev

表示第一坐标中的列坐标,vd表示节点v

分配的分区空间,vertical partition表示水平方向分割,horizontal partition表示竖直方向分割。

[0038]

在本技术方案的一种可行的实施例中,所述对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡中,延迟平衡的表达式如下:

[0039]eij.balance

=(s

i-s

j-e

ij.lat

)

[0040]

其中,si表示节点vi的时间步,sj表示节点vj的时间步,s

i-sj表示节点vi和节点vj之间的所有路径之间的最大延迟;e

ij.lat

表示插入流水线之前存在的额外时延;e

ij.balance

表示插入流水线后产生的平衡时延。

[0041]

在本技术方案的一种可行的实施例中,所述对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡这一步骤,包括:

[0042]

根据所述平衡时延构建面积开销的目标函数,所述目标函数为:

[0043][0044]

其中,e

ij.width

为流水线在节点vi与节点vj之间最大数据位宽。

[0045]

本发明的优点和有益效果将在下面的描述中部分给出,其他部分可以通过本发明的具体实施方式了解得到:

[0046]

本技术技术方案提出了一种基于平面规划算法的高层次综合指导fpga物理布局约束的全流程布局方法,方法通过目标电路的电路描述构建得到控制数据流图,并通过平面规划算法对所述控制数据流图进行分割,得到布局约束;在布局约束的基础上进行目标电路对应资源的调度和绑定得到寄存器传输级描述,进一步进行综合处理、布局布线得到目标电路的网表;通过高层次综合减少布局布线的拥塞情况,同时也能够减少布线过程中跨fpga block边界带来的延迟增加。

附图说明

[0047]

为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0048]

图1为本技术技术方案中所提供的高层次综合的流程布局方法的步骤流程图;

[0049]

图2为本技术技术方案中控制数据流图的示意图;

[0050]

图3为本技术技术方案中迭代分区过程示意图;

[0051]

图4(a)为本技术技术方案中平衡延迟示意图之一;

[0052]

图4(b)为本技术技术方案中平衡延迟示意图之二;

[0053]

图5为本技术技术方案中fifo流水线示意图。

具体实施方式

[0054]

下面详细描述本发明的实施例,实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。对于以下实施

例中的步骤编号,其仅为了便于阐述说明而设置,对步骤之间的顺序不做任何限定,实施例中的各步骤的执行顺序均可根据本领域技术人员的理解来进行适应性调整。

[0055]

基于目前相关技术方案中,特别是在fpga布局布线中,物理综合器往往会使用距离较近的资源,从而容易带来布局布线的拥塞,增加整体的布线长度,进而降低电路的吞吐量。针对相关技术方案中所存在的技术缺陷,本技术技术方案提出了一种基于平面规划算法的高层次综合工具指导fpga物理布局约束的全流程布局方法。

[0056]

在第一方面,如图1所示,本技术技术方案提供了高层次综合的流程布局方法;方法包括步骤s100-s400:

[0057]

s100、获取目标电路的电路描述,根据所述电路描述构建得到所述目标电路对应的控制数据流图;

[0058]

其中,如图2所示,控制数据流图为表征目标电路运算操作的有向图,在图2中的实线表示数据依赖关系,虚线表示控制依赖关系,三角形符号表示分支操作。实施例中电路描述包括但不限于通过vhdl语言或者verilog语言,对目标电路中的信号输入,元器件以及元器件所执行的逻辑操作进行描述的内容;目标电路可以是指真实场景中硬件电路。具体在实施例中,首先获取输入的电路描述,构建控制数据流图,在实施例中,控制数据流图(control data flow graph,cdfg)是一种有向图g=《v,e》,其中v表示控制数据流图中所有节点的集合,控制数据流图中的每一个节点代表目标电路中的一个运算操作;e表示控制数据流图中全部有向连接线的集合,控制数据流图中每一条连接两个节点的有向边代表这两个相应运算操作之间存在的数据或控制依赖关系。控制数据流图的控制关系依赖边体现电路描述的控制依赖性,数据关系依赖边体现电路描述的数据依赖性。基于控制数据流图的性质,在实施例中构建得到控制数据流图的过程中,首先,实施例通过编译器前端,根据源代码将电路描述中的行为级描述的高级语言代码生成中间码;然后实施例通过编译器后端将电路描述中变量映射为节点,将控制和数据依赖性映射为有向边,构建控制流数据流图。

[0059]

s200、通过平面规划算法对所述控制数据流图进行分割,得到布局约束;

[0060]

其中,实施例中的平面规划算法可以采用割平面算法进行求解规划;实施例中的布局可以定义为一组物理约束,用于控制逻辑在模型中的放置方式。具体在实施例中,首先根据目标电路对应的fpga架构,确定目标电路对应的分区数量、资源以及资源最大利用率;然后,将控制数据流图中数据流进程对应的函数编译为一个寄存器转换级电路(register transfer level,rtl)模块,放置在初始分区;基于割平面算法,将当前分区水平地或竖直地一分为二,计算并选择成本函数最小的方案,基于所得到的方案,确定目标电路对应在fpga架构中布局约束。

[0061]

在一些可行的实施方式中,通过平面规划算法对所述控制数据流图进行分割,得到布局约束这一步骤s200,可以包括步骤s210-s240:

[0062]

s210、获取所述电路描述中所述目标电路的fpga架构;

[0063]

s220、根据所述控制数据流图中数据流进程对应的函数,进行编译得到寄存器转换级的电路模块;

[0064]

s230、根据所述电路模块对所述fpga架构进行分区,确定分区结果的成本函数;

[0065]

s240、通过对所述fpga架构的分区结果进行分割迭代,确定所述成本函数为最小

值或者分区中的资源到达资源约束的临界值,输出得到所述布局约束;

[0066]

具体在实施例中,fpga架构中有多个block,不同block的资源可能会不同。良好的布局有助于减少布线拥塞,并提高设计中可实现的时序结果(qor)质量;而实施例中,布局约束使用到了pblock指令以实现对资源分区的指定,pblock边界允许利用时钟区域边界来定义pblock的大小,而不是使用slice、bram、dsp等范围,有助于限制时钟偏斜,并有助于设计的整体时钟放置。并且基于控制数据流图,实施例对hls设计进行分区的基础是数据流编程样式,即hls设计是流式的,设计结构被描述成一张有向图;在有向图中节点表示需要进行运算处理的单元,节点之间的连接线描述了数据传输路径;在有向图中,相邻节点通过量接线传输数据,节点消耗数据进行计算,并将产生的数据输出到输入输出序列作为下一个计算单元的输入。

[0067]

示例性地,实例中hls设计采用了一个数据流编程模型,其中每个函数对应一个数据流进程,每个函数对应一个rtl模块,模块之间使用fifo进行通信。则构建出图g=《v,e》,其中v表示数据流的集合,每一个节点代表一个函数;e表示顶点之间fifo通道的集合。

[0068]

s300、对所述控制数据流图进行调度,将调度结果进行绑定得到寄存器传输级描述;

[0069]

具体在实施例中,需要针对控制数据流图的子图进行相应的调度;对控制数据流图进行延迟平衡;进而,在一些可行的实施方案中,步骤s300可以包括步骤s310-s330:

[0070]

s310、对所述控制数据流图的子图进行调度;

[0071]

s320、对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡;

[0072]

s330、将调度结果以及延迟平衡后的结果进行数学整合,根据数学整合后的结果与所述目标电路进行绑定,得到所述寄存器传输级描述。

[0073]

具体在实施例中,对控制数据流图的子图采用高层次综合工具的默认方式进行调度;然后,对控制数据流图的割边插入流水线,进行平衡延迟;将步骤s310-s320中得到的调度结果进行数学整合后,获得综合调度结果;对综合调度结果对目标电路对应的fpga架构中的资源进行绑定,获得寄存器传输级描述。

[0074]

s400、根据所述布局约束对所述寄存器传输级描述得到目标网表,根据所述目标网表确定所述目标电路的流程布局;

[0075]

具体在实施例中,根据步骤s200中所得到布局约束以及步骤s300中所得到的寄存器传输级描述;对fpga架构中的资源进行整合处理以及布局布线操作,得到对应的目标网表,从而确定目标电路对应的控制流程布局。

[0076]

在一些可行的实施方式中,实施例中的布局约束包括时序约束或物理约束中的至少之一;目标网表包括综合网表或布局布线网表中的至少之一;进而实施例中根据所述布局约束对所述寄存器传输级描述得到目标网表,根据所述目标网表确定所述目标电路的流程布局这一步骤s400,可以包括步骤s410-s450:

[0077]

s410、根据所述时序约束和/或所述物理约束构建得到第一输入;

[0078]

s420、根据所述寄存器传输级描述构建得到第二输入;

[0079]

s430、通过fpga物理综合器,将所述第一输入以及所述第二输入进行整合处理输出得到综合网表;

[0080]

s440、通过fpga物理综合器,根据所述第一输入以及所述第二输入进行布局布线

处理输出得到布局布线网表;

[0081]

s450、根据所述综合网表以及所述布局布线网表确定所述目标电路的流程布局。

[0082]

具体在实施例中,首先将步骤s200中所得到的布局约束和高层次综合工具本身得到时序约束、物理约束作为综合实现的一组约束条件输入,即为第一输入;将步骤s300中所得到的寄存器传输级描述作为综合实现的rtl输入,即第二输入;然后实施例运行fpga物理综合器,执行综合、布局布线操作,获得综合后网表和布局布线后网表,根据所得到的网表确定目标电路的流程布局。

[0083]

在实施例中,步骤s230中根据所述电路模块对所述fpga架构进行分区,确定分区结果的成本函数,其中,成本函数物理意义是穿过分区边界的导线数量的总和。进而,实施例中的成本函数为:

[0084][0085]

其中,c为成本值,vi以及vj表征所述控制数据流图中的节点,i=1,2,3,

…

n,j=1,2,3,

…

n,n为正整数,e表征节点间fifo通道的集合,e

ij

为vi和vj之间的连接线,row表示行数,col表示列数,width表示数据位宽。

[0086]

在实施例中,步骤s240通过对所述fpga架构的分区结果进行分割迭代,确定所述成本函数为最小值或者分区中的资源到达资源约束的临界值,输出得到所述布局约束;其中,资源约束的表达式如下:

[0087][0088]

其中,vd表示节点v分配的分区空间,v

area

表示节点的所需资源,rv表示当前分区r所容纳的节点集合,(r

child

)

area

表示每个分区中的资源数量。

[0089]

在实施例中,对所述fpga架构的分区结果进行分割迭代,确定所述成本函数为最小值或者分区中的资源到达资源约束的临界值,输出得到所述布局约束这一步骤s240,可以包括步骤s241-s242:

[0090]

s241、获取所述控制数据流图中节点在分割迭代之前的第一坐标,根据分割方式确定坐标变换关系,根据所述坐标变换关系将所述第一坐标变换得到第二坐标;

[0091]

s242、所述分割方式包括水平方向分割或竖直方向分割;

[0092]

具体在实施例中,如图3所示,分区的过程可以看作是迭代地一次次一分为二,直到成本函数最小或者不再满足约束条件,最后再添加流水线fifo;第一步是把所有函数映射成rtl模块,放在一个分区中,称为初始化分区,其中依赖关系为1指向2、3、4,2、3、4指向5,而且2和3的资源占用比较少;第二步是竖直地一分为二,123放在上方,45放在下方;第三步是对于每个分区水平地一分为二,其结果是2和3位于左上方,1位于右上方,4位于左下方,5位于右下方;最后一步是为跨越block边界的走线添加fifo流水线,保证电路设计的吞吐量。

[0093]

进一步地,实施例中坐标变换关系的表达式如下:

[0094]

[0095][0096]

其中,v.row表示第二坐标中的行坐标,v.col表示第二坐标中的列坐标,(v.row)

prev

表示第一坐标中的行坐标,(v.col)

prev

表示第一坐标中的列坐标,vd表示节点v分配的分区空间,vertical partition表示水平方向分割,horizontal partition表示竖直方向分割。

[0097]

在实施例中,步骤s320对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡。

[0098]

具体在实施例中,给定一个已经分区和流水线化的数据流图g《v,e》,每个顶点v∈v代表数据流设计中的一个函数,每条边e∈e代表函数之间的fifo通道,宽度e.width表示边的位宽,延时e.lat代表在上一个流水线步骤中插入的额外延时,平衡延时e.balance代表在当前步骤中的平衡延时。对于每条边e∈e,每条路径的总延时可以表示为:

[0099][0100]

其中,{p1,p2}表示一对重新汇聚的路径。进一步地,延迟平衡中对于每条边(连接线)e,可以认为si≥sj+e

ij.lat

,额外的平衡延时可以表示为:

[0101]eij.balance

=(s

i-s

j-e

ij.lat

)

[0102]

其中,si表示节点vi的时间步,sj表示节点vj的时间步,s

i-sj表示节点vi和节点vj之间的所有路径之间的最大延迟;e

ij.lat

表示上一个流水线步骤在顶点vi和vj之间最长路径中插入的额外延时;e

ij.balance

表示当前流水线步骤在顶点vi和vj之间最长路径中插入的额外延时。

[0103]

示例性地,如图4所示,图4(a)表示平衡延迟过程中的cut-set1剪割集;图4(b)表示平衡延迟过程中的cut-set2和cut-set3剪割集,其中,边缘e13、e37和e27是根据平面图分区进行管道化的,然后每个边缘都携带1个单位的插入延迟。同时假设e14的位宽为2,其他所有边均为1。在延迟平衡步骤中,最优解决方案是给e47、e57、e67每条边增加2个单位的延迟,给e12每个增加1个单位的延迟。请注意,e27和e37可以存在于同一个剪割集cut-set中。

[0104]

如图5所示,分区划分后基于fifo进行连接,使其能够流水线化。采用fifo,可以直接调度匹配接口信号,而不影响功能,并且提供电路功能的并行性。

[0105]

在一些可行的实施方式中,所述对所述控制数据流图中节点之间的连接线插入流水线进行延迟平衡这一步骤s320,还可以包括步骤s321:

[0106]

s321、根据所述平衡时延构建面积开销的目标函数;

[0107]

具体在实施例中,平衡延迟的优化目标是最小化总面积开销,并且考虑到每条边的位宽开销。实施例中的目标函数为:

[0108][0109]

其中,e

ij.width

为流水线在节点vi与节点vj之间最大数据位宽

[0110]

从上述具体的实施过程,可以总结出,本发明所提供的技术方案相较于现有技术

存在以下优点或优势:

[0111]

本发明可以应用在中大型的数据流编程模型的高层次综合设计中,发挥高层次综合工具能够快速原型设计的特点,同时延展了设计流程,从高级语言到硬件描述语言,再到物理布局。高层次综合工具指导物理布局的全流程设计方法,可以进一步提高高层次综合设计的布局布线情况,减少布局拥塞,保证电路整体的吞吐量。

[0112]

示例性地,对riscv cpu设计分别使用默认的hls和应用布局约束hls,可以明显确定应用布局约束的hls设计将资源占用率最高的cpu模块、fft模块、usb1模块、usb2模块进行分区流水线处理,同时分布在相邻但不同的block块。在满足时序约束的情况下,时序裕量基本没有改变,但是拥塞情况大大改善,也减少了物理综合的运行时间。

[0113]

在一些可选择的实施例中,在方框图中提到的功能/操作可以不按照操作示图提到的顺序发生。例如,取决于所涉及的功能/操作,连续示出的两个方框实际上可以被大体上同时地执行或所述方框有时能以相反顺序被执行。此外,在本发明的流程图中所呈现和描述的实施例以示例的方式被提供,目的在于提供对技术更全面的理解。所公开的方法不限于本文所呈现的操作和逻辑流程。可选择的实施例是可预期的,其中各种操作的顺序被改变以及其中被描述为较大操作的一部分的子操作被独立地执行。

[0114]

此外,虽然在功能性模块的背景下描述了本发明,但应当理解的是,除非另有相反说明,功能和/或特征中的一个或多个可以被集成在单个物理装置和/或软件模块中,或者一个或多个功能和/或特征可以在单独的物理装置或软件模块中被实现。还可以理解的是,有关每个模块的实际实现的详细讨论对于理解本发明是不必要的。更确切地说,考虑到在本文中公开的装置中各种功能模块的属性、功能和内部关系的情况下,在工程师的常规技术内将会了解该模块的实际实现。因此,本领域技术人员运用普通技术就能够在无需过度试验的情况下实现在权利要求书中所阐明的本发明。还可以理解的是,所公开的特定概念仅仅是说明性的,并不意在限制本发明的范围,本发明的范围由所附权利要求书及其等同方案的全部范围来决定。

[0115]

在流程图中表示或在此以其他方式描述的逻辑和/或步骤,例如,可以被认为是用于实现逻辑功能的可执行指令的定序列表,可以具体实现在任何计算机可读介质中,以供指令执行系统、装置或设备(如基于计算机的系统、包括处理器的系统或其他可以从指令执行系统、装置或设备取指令并执行指令的系统)使用,或结合这些指令执行系统、装置或设备而使用。

[0116]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0117]

尽管已经示出和描述了本发明的实施例,本领域的普通技术人员可以理解:在不脱离本发明的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

[0118]

以上是对本发明的较佳实施进行了具体说明,但本发明并不限于上述实施例,熟悉本领域的技术人员在不违背本发明精神的前提下还可做作出种种的等同变形或替换,这

些等同的变形或替换均包含在本技术权利要求所限定的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1