一种SOI工艺中结电容和结电流的表征方法与流程

一种soi工艺中结电容和结电流的表征方法

技术领域

1.本发明涉及半导体设计spice建模技术领域,具体涉及一种soi工艺中结电容和结电流的表征方法。

背景技术:

2.半导体发展至今,无论是从结构和加工技术多方面都发生了很多的改进,半导体器件的规格在不断的缩小,芯片的集成度也在不断提升。随着mos管的尺寸不断的变小,沟道的不断变小,出现各种问题,如短沟道效应、栅极漏电、泄漏功率大等。为了克服不断出现的问题,研发人员不断从材料、结构、工艺这三个方面进行改进。

3.soi(silicon-on-insulator)工艺是在顶层硅和背衬底之间引入了一层埋氧化层,soi工艺相较于体硅工艺,具有漏电流低、寄生电容小等优势,可满足低压、低功耗、超高速电路设计需求。

4.bsim(berkeley short-channel igfet model)模型是uc berkeley(加州大学伯克利分校)胡正明团队针对短沟道mosfet(metal-oxide-semiconductor field-effect transistor)提出的模型,其中bsim-soi模型是针对于soi工艺的mosfet模型,具有仿真速度快,准确性和灵活度高等优点,缺点在于vds=0v附近的非对称性。为了解决对称性问题,uc berkeley模型团队于2010年开始研发新模型并于2013年推出第一个版本模型:bsim6 6.0.0,2016年bsim6正式更名为bsim-bulk,以便更好体现模型物理架构。目前使用较多的版本是bsim-bulk 106.2.0。由于对称性优势,业界使用bsim-bulk model越来越多。

5.在soi工艺中,采用bsim-bulk模型架构,可以解决对称性问题,满足电路设计对模型对称性的要求。然而bsim-bulk模型主要是适用于体硅工艺,在结电容和结电流方面,soi与体硅工艺存在较大差异。如何利用bsim-bulk模型精确表征soi工艺结电容和结电流,是本领域技术人员需要面对和解决的问题。

技术实现要素:

6.为了解决现有技术存在的不足,本发明的目的在于提供一种soi工艺中结电容和结电流的表征方法,解决结电容和结电流建模问题,从而提高模型仿真准确性。

7.为实现上述目的,本发明提供一种soi工艺中结电容和结电流的表征方法,包括以下步骤:

8.1)根据bsim-bulk模型需要的模型参数,建立soi器件的bsim-bulk模型;

9.2)基于二极管iv和cv测试数据,提取相应模型参数,建立二极管模型;

10.3)基于所述bsim-bulk模型和所述二极管模型,分别建立结电容计算模型和结电流计算模型;

11.4)确定结电容和结电流计算模型中的参数值;

12.5)对bsim-bulk模型参数rbodymod进行修正,将其值从0调整到1,其中rbodymod为衬底电阻模型开关;

13.6)基于结电容和结电流的实测数据,对bsim-bulk模型的参数cjsw/jsw进行微调。

14.进一步地,所述bsim-bulk模型参数,包括:漏极相关的栅极边缘侧壁结电容、源极相关的栅极边缘侧壁结电容、漏极相关的底部结电容,以及源极相关的底部结电容。

15.进一步地,所述步骤3)进一步包括,

16.建立结电容计算模型的计算公式为:

17.cjgate=cjswg*weffcv+cjsw*pd+cj*ad

18.其中,cjgate为结电容,cjswg为栅极边缘侧壁结电容,weffcv为交流情况下等效沟道宽度,cjsw为隔离边缘侧壁结电容,pd为漏极相关的结周长,cj为底部结电容,ad为结面积;

19.建立结电流计算模型的计算公式为:

20.ijgate=jswg*weffcv+jsw*pd+js*ad

21.式中,ijgate为结电流,jswg为栅极边缘侧壁反向饱和电流密度,jsw为二极管参数,为隔离边缘侧壁反向饱和电流密度,pd为漏极相关的结周长,js为源极相关的底部反向饱和电流密度。

22.进一步地,所述步骤4)进一步包括,针对结电容计算模型进行参数设定:

23.将结电容计算模型中的cjswg参数和cj参数分别置0,其中,cjswg参数包括cjswgd和cjswgs,其中cjswgd表示漏极相关的栅极边缘侧壁结电容,cjswgs表示源极相关的栅极边缘侧壁结电容;cj包括cjd和cjs,其中,cjd表示漏极相关的底部结电容,cjs表示源极相关的底部结电容;

24.从相应二极管模型确定cjsw参数,cjsw参数包括cjswd,cjsws,mjswd,mjsws,pbswd,pbsws,其中,cjswd表示漏极相关的隔离边缘侧壁结电容,cjsws表示源极相关的隔离边缘侧壁结电容,mjswd表示漏极相关的隔离边缘侧壁结电容梯度系数,mjsws表示源极相关的隔离边缘侧壁结电容梯度系数,pbswd表示漏极相关的隔离边缘侧壁结电容内建电势,pbsws表示源极相关的隔离边缘侧壁结电容内建电势。

25.进一步地,所述从相应二极管模型确定cjsw参数,包括,

26.将相应二极管参数cjsw复制到bsim-bulk模型参数cjswd和cjsws,其中,cjsw表示隔离边缘侧壁结电容;

27.将相应二极管参数mjsw复制到bsim-bulk模型参数mjswd和mjsws,其中,mjsw表示隔离边缘侧壁结电容梯度系数;

28.将相应二极管参数php复制到bsim-bulk模型参数pbswd和pbsws,其中,php表示隔离边缘侧壁结电容内建电势。

29.进一步地,所述步骤4)进一步包括,针对结电流计算模型进行参数设定:

30.将结电流计算模型中的jswg和js分别置0,jswg参数包括jswgd和jswgs,其中,jswgd表示漏极相关的栅极边缘侧壁反向饱和电流密度,jswgs表示源极相关的栅极边缘侧壁反向饱和电流密度;

31.从相应二极管模型确定jsw相关参数,jsw相关参数包括jswd,jsws,njd和njs,其中,jswd表示漏极相关的隔离边缘侧壁反向饱和电流密度,jsws表示源极相关的隔离边缘侧壁反向饱和电流密度,njd表示漏极相关的结发射系数,njs表示源极相关的结发射系数;将相应二极管参数jsw复制到bsim-bulk模型参数jswd和jsws,其中jsw表示隔离边缘侧壁

是“至少部分地基于”。术语“一个实施例”表示“至少一个实施例”;术语“另一实施例”表示“至少一个另外的实施例”;术语“一些实施例”表示“至少一些实施例”。其他术语的相关定义将在下文描述中给出。

48.需要注意,本发明中提及的“一个”、“多个”的修饰是示意性而非限制性的,本领域技术人员应当理解,除非在上下文另有明确指出,否则应该理解为“一个或多个”。“多个”应理解为两个或以上。

49.下面,将参考附图详细地说明本发明的实施例。

50.实施例1

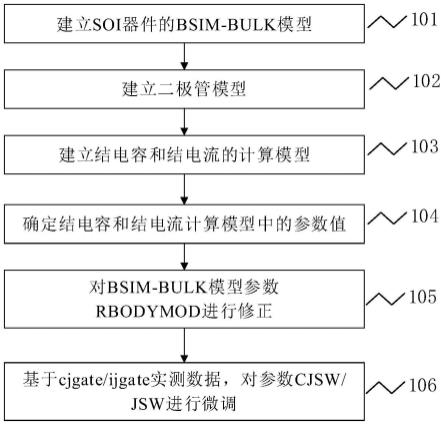

51.图1为根据本发明的soi工艺中结电容和结电流的表征方法流程图,下面将参考图1,对本发明的soi工艺中结电容和结电流的表征方法进行详细描述。

52.在步骤101,建立soi器件的bsim-bulk模型。

53.本发明实施例中,根据建立bsim-bulk模型所需要的模型参数,建立soi器件的bsim-bulk模型,其中,bsim-bulk模型参数,包括,漏极相关的栅极边缘侧壁结电容cjswgd、源极相关的栅极边缘侧壁结电容cjswgs、漏极相关的底部结电容cjd,以及源极相关的底部结电容cjs。

54.在步骤102,建立二极管模型。

55.本发明实施例中,基于二极管的电流电压(iv)和电容电压(cv)测试数据,提取相应模型参数,建立二极管模型(diode模型)。

56.在步骤103,建立结电容和结电流的计算模型。

57.本发明实施例中,基于步骤101中建立的bsim-bulk模型和步骤102中建立的二极管模型,建立结电容计算模型,计算公式如下:

58.cjgate=cjswg*weffcv+cjsw*pd+cj*ad

ꢀꢀꢀꢀꢀꢀ

(1)

59.式中,cjgate为结电容,cjswg为栅极边缘侧壁结电容,weffcv为交流情况下等效沟道宽度,cjsw为隔离边缘侧壁结电容,pd为结周长,cj为底部结电容,ad为结面积。

60.本发明实施例中,基于步骤101中建立的bsim-bulk模型和步骤102中建立的二极管模型,建立结电流计算模型,计算公式如下:

61.ijgate=jswg*weffcv+jsw*pd+js*ad

ꢀꢀꢀꢀꢀꢀ

(2)

62.式中,ijgate为结电流,jswg为栅极边缘侧壁反向饱和电流密度,jsw为二极管(diode)参数,为隔离边缘侧壁反向饱和电流密度,pd为结周长,js为源极相关的底部反向饱和电流密度。

63.在步骤104,确定结电容和结电流计算模型中的参数值。

64.本发明实施例中,分别针对结电容和结电流的计算模型进行参数设定。

65.对于结电容的计算模型,将公式(1)中cjswg和cj分别置0,具体地,cjswg参数包括cjswgd和cjswgs,其中cjswgd表示漏极相关的栅极边缘侧壁结电容,cjswgs表示源极相关的栅极边缘侧壁结电容;cj包括cjd和cjs,其中,cjd表示漏极相关的底部结电容,cjs表示源极相关的底部结电容,也就是说,将bsim-bulk模型参数cjswgd、cjswgs、cjd和cjs置0。

66.cjsw参数直接从相应二极管模型复制过来,cjsw参数包括cjswd,cjsws,mjswd,mjsws,pbswd,pbsws,其中,cjswd表示漏极相关的隔离边缘侧壁结电容,cjsws表示源极相关的隔离边缘侧壁结电容,mjswd表示漏极相关的隔离边缘侧壁结电容梯度系数,mjsws表

示源极相关的隔离边缘侧壁结电容梯度系数,pbswd表示漏极相关的隔离边缘侧壁结电容内建电势,pbsws表示源极相关的隔离边缘侧壁结电容内建电势。具体地,将相应二极管参数cjsw(表示隔离边缘侧壁结电容)复制到bsim-bulk模型参数cjswd和cjsws,将相应二极管参数mjsw(隔离边缘侧壁结电容梯度系数)复制到bsim-bulk模型参数mjswd和mjsws,将相应二极管参数php(隔离边缘侧壁结电容内建电势)复制到bsim-bulk模型参数pbswd和pbsws。

67.对于结电流的计算模型,将公式(2)中jswg和js分别置0,jswg参数包括jswgd和jswgs,其中,jswgd表示漏极相关的栅极边缘侧壁反向饱和电流密度,jswgs表示源极相关的栅极边缘侧壁反向饱和电流密度。具体地,将bsim-bulk模型参数jswgd、jswgs、jd(漏极相关的底部反向饱和电流密度)、js(源极相关的底部反向饱和电流密度)置0。

68.然后,jsw相关参数直接从相应二极管模型复制过来。jsw相关参数包括jswd,jsws,njd和njs,其中,jswd漏极相关的隔离边缘侧壁反向饱和电流密度,jsws为源极相关的隔离边缘侧壁反向饱和电流密度。具体地,将相应二极管参数jsw(隔离边缘侧壁反向饱和电流密度)复制到bsim-bulk模型参数jswd和jsws,将相应二极管参数n(结发射系数)复制到bsim-bulk模型参数njd(漏极相关的结发射系数)/njs(源极相关的结发射系数)。

69.对于pd(漏极相关的结周长)/ps(源极相关的结周长)计算公式进行修正,新计算公式为

70.pd=w+pdbcp

71.ps=w+psbcp

72.w为晶体管宽度,pdbcp漏极相关的体接触寄生边缘长度,psbcp表示源极相关的体接触寄生边缘长度。

73.bsim-bulk模型高低温参数包括tcjsw,tpbsw,xtid和xtis,将相应diode高低温参数ctp(cjsw温度系数)复制到bsim-bulk模型参数tcjsw(cjswd/cjsws温度系数),将相应diode高低温参数tphp(php温度系数)复制到bsim-bulk模型参数tpbsw(pbswd/pbsws温度系数),将相应diode高低温参数xti(结电流温度系数)复制到bsim-bulk模型参数xtid(漏极相关的结电流温度系数)和xtis(源极相关的结电流温度系数)。

74.计算模型高低温参数确保高低温条件下结电容和结电流模型的准确性。

75.在步骤105,对bsim-bulk模型参数rbodymod进行修正。

76.本发明实施例中,对bsim-bulk模型参数rbodymod(衬底电阻模型开关)进行修正,将其值从0调整到1。

77.在步骤106,基于cjgate/ijgate实测数据,对参数cjsw/jsw进行微调。

78.本发明实施例中,基于cjgate/ijgate常温和高低温实测数据,对bsim-bulk模型参数进行微调,进行微调的模型参数包括cjswd,cjsws,mjswd,mjsws,pbswd,pbsws,jswd,jsws,njd,njs,tcjsw,tpbs,xtid,xtis。具体地,在提参工具中,导入模型和数据,稍微修改模型参数值,使模型结果和数据更好吻合。

79.cjgate/ijgate实测数据中的常温条件是指25℃,低温条件是指-40℃,高温条件是指150℃。

80.实施例2

81.本发明实施例还提供了一种电子设备,包括存储器和处理器,存储器上储存有在

处理器上运行的程序,处理器运行所述程序时执行上述soi工艺中结电容和结电流的表征方法的步骤。

82.实施例3

83.本发明实施例还提供了一种计算机可读存储介质,其上存储有计算机指令,所述计算机指令运行时执行上述的soi工艺中结电容和结电流的表征方法的步骤,所述soi工艺中结电容和结电流的表征方法参见前述部分的介绍,不再赘述。

84.本领域普通技术人员可以理解:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1