存储芯片、控制方法及电子设备与流程

1.本技术属于芯片技术领域,具体涉及一种存储芯片、控制方法及电子设备。

背景技术:

2.由于独显芯片功能越来越丰富,并加入越来越多的ai(artificial intelligence,人工智能)算法,对数据吞吐速率和缓存容量要求变高,需要内部集成大容量缓存单元,其中,双倍速率同步动态随机存储器(double data rate synchronous dynamic random access memory,ddr)是比较合适的选择。

3.相关技术中,系统ddr内存通常比较大,供系统级芯片(system on chip,soc)使用,独显芯片中通过内置ddr供独显芯片使用,内置ddr的内存一般在2gb左右。

技术实现要素:

4.本技术实施例的目的是提供一种存储芯片、控制方法及电子设备,能够提高存储芯片的利用率。

5.第一方面,本技术实施例提供了一种存储芯片,包括第一切换模块、第二切换模块以及连接于所述第一切换模块与所述第二切换模块之间的存储模块;

6.所述第一切换模块分别与系统级芯片以及独显芯片连接,所述第二切换模块分别与所述系统级芯片以及所述独显芯片连接;

7.其中,在所述第一切换模块处于第一状态,且所述第二切换模块处于第二状态的情况下,所述存储芯片用于存储所述系统级芯片的数据信息;在所述第一切换模块处于第三状态,且所述第二切换模块处于第四状态的情况下,所述存储芯片用于存储所述独显芯片的数据信息。

8.第二方面,本技术实施例提供了一种芯片系统,包括系统级芯片、独显芯片以及如第一方面所述的存储芯片,所述系统级芯片与所述独显芯片连接。

9.第三方面,本技术实施例提供了一种控制方法,所述方法用于如第二方面所述芯片系统,所述方法包括:

10.在所述系统级芯片启动的情况下,向所述第一切换模块以及所述第二切换模块发送第一电平的模式切换信号,以控制所述第一切换模块进入第一状态以及所述第二切换模块进入第二状态,使所述存储芯片存储所述系统级芯片的数据信息;

11.所述系统级芯片在接收到所述独显芯片发送的第一通知信息或在所述独显芯片处于预设场景的情况下,向所述第一切换模块以及所述第二切换模块发送第二电平的模式切换信号,以控制所述第一切换模块切换为第三状态以及所述第二切换模块切换为第四状态,使所述存储芯片存储所述独显芯片的数据信息。

12.第四方面,本技术实施例提供了一种电子设备,包括如第一方面所述的存储芯片。

13.第五方面,本技术实施例提供了一种电子设备,包括如第二方面所述的芯片系统。

14.第六方面,本技术实施例提供了一种电子设备,该电子设备包括处理器和存储器,

所述存储器存储可在所述处理器上运行的程序或指令,所述程序或指令被所述处理器执行时实现如第三方面所述的方法的步骤。

15.第七方面,本技术实施例提供了一种可读存储介质,所述可读存储介质上存储程序或指令,所述程序或指令被处理器执行时实现如第三方面所述的方法的步骤。

16.第八方面,本技术实施例提供一种计算机程序产品,该程序产品被存储在存储介质中,该程序产品被至少一个处理器执行以实现如第三方面所述的方法的步骤。

17.在本实施例中,存储芯片设置有第一切换模块和第二切换模块,第一切换模块和第二切换模块处于不同状态,存储芯片对应可处于不同的工作模式,可通过改变第一切换模块和第二切换模块的状态,以改变存储芯片的工作模式,在第一切换模块处于第一状态,且第二切换模块处于第二状态的情况下,存储芯片可用于存储系统级芯片的数据信息,供系统级芯片使用,而在第一切换模块处于第三状态,且第二切换模块处于第四状态的情况下,存储芯片可用于存储独显芯片的数据信息,供系独显芯片使用,也即是可改变切换模块的状态,将可供系统级芯片使用的存储芯片切换为供独显芯片使用,无需在独显芯片内置ddr供独显芯片使用,存储芯片的利用率更高。

附图说明

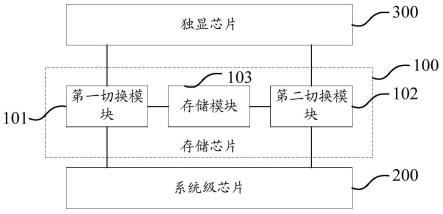

18.图1是本技术实施例提供的存储模块的结构图之一;

19.图2是本技术实施例提供的控制方法的流程图;

20.图3是现有应用独显芯片的硬件系统架构图;

21.图4是现有应用带内置ddr独显芯片的硬件系统结构框图;

22.图5是现有系统ddr芯片原理框图;

23.图6是现有系统ddr芯片中任一晶片的原理框图;

24.图7是本技术实施例提供的存储芯片的原理框图;

25.图8是本技术实施例提供的存储芯片中第二芯片的原理框图;

26.图9是本技术实施例提供的开关阵列示意图;

27.图10是本技术实施例提供的第一切换模块中开关的示意图;

28.图11是本技术实施例提供的第二切换模块中开关的示意图;

29.图12是本技术实施例提供的应用本技术实施的独显芯片的硬件系统架构图;

30.图13是本技术实施例提供的应用本技术实施例的独显芯片的硬件系统结构框图;

31.图14是本技术实施例提供的电子设备的结构示意图;

32.图15是本技术实施例提供的电子设备的硬件结构示意图。

具体实施方式

33.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员获得的所有其他实施例,都属于本技术保护的范围。

34.本技术的说明书和权利要求书中的术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便本技术的实施例能够以除了在这里图示或描述的那些以外的顺序实施,且“第一”、“第二”等所区分的对象通常为一类,并不限定对象的个数,例如第一对象可以是一个,也可以是多个。此外,说明书以及权利要求中“和/或”表示所连接对象的至少其中之一,字符“/”,一般表示前后关联对象是一种“或”的关系。

35.如图1所示,本技术提供一种实施例的存储芯片100,包括第一切换模块101、第二切换模块102以及连接于第一切换模块101与第二切换模块102之间的存储模块103,第一切换模块101分别与系统级芯片200以及独显芯片300连接,第二切换模块102分别与系统级芯片200以及独显芯片300连接。

36.其中,在第一切换模块101处于第一状态,且第二切换模块102处于第二状态的情况下,存储芯片100用于存储系统级芯片200的数据信息;在第一切换模块101处于第三状态,且第二切换模块102处于第四状态的情况下,存储芯片100用于存储独显芯片300的数据信息。

37.需要说明的是,切换模块也可称开关模块,在第一切换模块101与第二切换模块102处于不同的状态的情况下,存储芯片100对应处于不同的工作模式,比如,在第一切换模块101处于第一状态,且第二切换模块102处于第二状态的情况下,存储芯片100可供系统级芯片200使用,可以理解,存储芯片100供系统级芯片200使用的工作模式下,存储芯片100可存储系统级芯片200的数据信息,实现系统级芯片200的数据信息的写入,以及可向系统级芯片200发送数据,实现系统级芯片200向存储芯片100读取数据。在第一切换模块101处于第三状态,且第二切换模块102处于第四状态的情况下,存储芯片100可供独显芯片300使用,可以理解,存储芯片100供独显芯片300使用的工作模式下,存储芯片100可存储独显芯片300的数据信息,实现独显芯片300的数据信息的写入,以及可向独显芯片300发送数据,实现独显芯片300向存储芯片100读取数据。

38.在本实施例中,存储芯片100设置有第一切换模块101和第二切换模块102,第一切换模块101和第二切换模块102处于不同状态,存储芯片100对应可处于不同的工作模式,可通过改变第一切换模块101和第二切换模块102的状态,以改变存储芯片100的工作模式,在第一切换模块101处于第一状态,且第二切换模块102处于第二状态的情况下,存储芯片100可用于存储系统级芯片200的数据信息,供系统级芯片200使用,而在第一切换模块101处于第三状态,且第二切换模块102处于第四状态的情况下,存储芯片100可用于存储独显芯片300的数据信息,供系独显芯片300使用,也即是可改变切换模块的状态,将可供系统级芯片200使用的存储芯片100切换为供独显芯片300使用,无需在独显芯片300内置ddr供独显芯片300使用,可减少内存浪费。与此同时,可减少独显芯片300功耗和发热量,提升独显芯片300的性能。

39.在一个实施例中,存储芯片100包括n个第一芯片和第二芯片,n为正整数,其中,第二芯片包括第一切换模块101、第二切换模块102以及存储模块103;

40.其中,每个第一芯片分别与系统级芯片200连接,n个第一芯片中的第一目标芯片分别与系统级芯片200的m个第一信号端口以及k个第二信号端口连接,m、k为大于1的整数,m个第一信号端中m-1个第一信号端口还与第一切换模块101连接,k个第二信号端口还与第二切换模块102连接;

41.第一芯片用于存储系统级芯片200的数据信息,在第一切换模块101处于第一状态,且第二切换模块102处于第二状态的情况下,第二芯片用于存储系统级芯片200的数据

信息;在第一切换模块101处于第三状态,且第二切换模块102处于第四状态的情况下,第二芯片用于存储独显芯片300的数据信息。

42.需要说明的是,第一目标芯片是n个第一芯片中的任一芯片,一个第一芯片通过(m+k)个信号端口,与系统级芯片200的m个第一信号端口以及k个第二信号端口一一对应连接,需要说明的是,系统级芯片200是通过不同的信号端口与不同的第一芯片的信号端口连接,即每个第一芯片通过不同信号端口连接系统级芯片200的不同信号端口。

43.在本实施例中,存储芯片100中的n个第一芯片供系统级芯片200使用,将存储芯片100中的第二芯片作为可切换的芯片,即第二芯片可供系统级芯片200使用或者供独显芯片300使用,如此,存储芯片100可供系统级芯片200使用或者供系统级芯片200和独显芯片300共同使用,独显芯片300和系统级芯片200可共用存储芯片100,提高存储芯片100的利用率。与此同时,独显芯片300可使用存储芯片100中的第二芯片,无需在独显芯片300中内置ddr芯片,即独显芯片300不用内置ddr,也无需额外的ddr供电设计,可显著降低成本;还可将内置ddr的热量转移至系统级芯片的ddr中,可降低独显芯片的发热,提高独显芯片的性能。

44.在一个实施例中,第一切换模块101包括m个第一开关,第二切换模块102包括k个第二开关,其中,每个第一开关包括第一固定端、第一选择端和第二选择端,每个第二开关包括第二固定端、第三选择端和第四选择端;

45.其中,存储模块103连接于第一固定端与第二固定端之间,m个第一开关中m-1个第二目标开关的第一选择端与系统级芯片200的m-1个第一信号端口一一对应连接,m个第一开关的第二选择端与系统级芯片200的m个第二信号端口一一对应连接,第三目标开关的第一选择端连接独显芯片300的第一输出端口,第三目标开关为m个第一开关中除m-1个第二目标开关之外的开关,k个第二开关的第三选择端与系统级芯片200的k个第三信号端口一一对应连接,k个第二开关的第四选择端与独显芯片300的k个第四信号端一一对应连接。

46.需要说明的是,m-1个第二目标开关为m个第一开关中的m-1个开关。第一固定端和第一选择端之间的连接状态与第二固定端和第三选择端之间的连接状态是联动的,即连接状态一致,第一固定端和第三选择端之间的连接状态与第二固定端和第四选择端之间的连接状态是联动的,即连接状态一致。第二芯片通过m个第一开关,可选择输出到存储模块103的信号,例如,选择系统级芯片200的m-1个第一信号端口和独显芯片300的第一输出端口传输的信号,或者选择系统级芯片200的m个第二信号端口传输的信号。第二芯片通过k个第二开关,可选择连接到系统级芯片200的k个第三信号端口,或者选择连接到独显芯片300的k个第四信号端。

47.在本实施例中,通过对m个第一开关和k个第二开关状态的连接状态的改变,即可实现第二芯片供系统及芯片使用与供独显芯片300使用的切换,切换过程简单。

48.在一个实施例中,每个第一开关还包括第一控制端,每个第二开关还包括第二控制端,m个第一开关的第一控制端以及k个第二开关的第二控制端均与系统级芯片200的模式切换端口连接,m个第一开关的第一控制端以及k个第二开关的第二控制端用于接收系统级芯片200通过模式切换端口传输的模式切换信号;

49.其中,每个第一开关包括第一连接状态与第二连接状态,在第一开关处于第一连接状态下,第一开关的第一固定端与第一开关的第一选择端连通,在第一开关处于第二连接状态下,第一开关的第一固定端与第一开关的第二选择端连通,模式切换信号用于控制

每个第一开关在第一连接状态与第二连接状态之间切换;

50.每个第二开关包括第三连接状态与第四连接状态,在第二开关处于第三连接状态下,第二开关的第二固定端与第二开关的第三选择端连通,在第二开关处于第四连接状态下,第二开关的第二固定端与第二开关的第四选择端连通,模式切换信号用于控制每个第二开关在第三连接状态与第四连接状态之间切换。

51.需要说明的是,m个第一开关的第一控制端以及k个第二开关的第二控制端连接同一个端口,即系统级芯片200的模式切换端口,这样,系统级芯片200通过模式切换端口可向m个第一开关和k个第二开关发送同一个模式切换信号,以控制m个第一开关和k个第二开关的连接状态。m个第一开关处于第一连接状态下,第一切换模块101处于第一状态,k个第二开关处于第三连接状态下第二切换模块102处于第二状态,m个第一开关处于第二连接状态下,第一切换模块101处于第三状态,k个第二开关处于第四连接状态下第二切换模块102处于第四状态。

52.在本实施例中,通过系统级芯片200可向第一开关和第二开关发送模式切换信号,以控制第一开关在第一连接状态与第二连接状态之间切换,以及控制第二开关在第三连接状态与第四连接状态之间切换,从而实现第二芯片工作模式的切换,即实现供系统级芯片200使用和供独显芯片300使用之间的切换。

53.在一个实施例中,在模式切换信号为低电平信号的情况下,m个第一开关均处于第一连接状态,k个第二开关均处于第三连接状态;

54.在模式切换信号为高电平信号的情况下,m个第一开关均处于第二连接状态,k个第二开关均处于第四连接状态。

55.即在本实施例中,通过系统级芯片200发送高低电平信号,以控制第一开关和第二开关的连接状态,通过低电平信号可控制m个第一开关处于第一连接状态以及控制k个第二开关处于第三连接状态,通过高电平信号,控制m个第一开关处于第二连接状态以及控制k个第二开关处于第四连接状态,提高开关状态控制的准确性。

56.本技术提供一种实施例的芯片系统,包括系统级芯片、独显芯片以及如上实施例的存储芯片,系统级芯片与独显芯片连接。

57.需要说明的是,系统级芯片以及独显芯片均与显示屏连接,显示屏通过不同接口连接系统级芯片和独显芯片。

58.如图2所示,本技术提供一种实施例的控制方法,方法用于如上实施例的芯片系统,方法包括:

59.步骤201:在系统级芯片启动的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制第一切换模块进入第一状态以及第二切换模块进入第二状态,使存储芯片存储系统级芯片的数据信息;

60.步骤202:系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态,使存储芯片存储独显芯片的数据信息。

61.在一个实施例中,在系统级芯片启动的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制第一切换模块进入第一状态以及第二切换模块进

入第二状态之后,还包括:

62.系统级芯片向存储芯片发送第一重置信号,以对存储芯片进行重置;

63.系统级芯片向存储芯片发送第一初始化信号,以对存储芯片进行初始化;

64.系统级芯片向独显芯片发送第一电源信号,以使独显芯片上电,以及向独显芯片发送第二初始化信号,以对独显芯片进行初始化。

65.在一个实施例中,存储芯片包括n个第一芯片和第二芯片,其中,系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,包括:

66.系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,将第二芯片的数据迁移到n个第一芯片中的任一芯片;

67.在第二芯片的数据迁移完毕的情况下,系统级芯片向第一切换模块以及第二切换模块发送第二电平的模式切换信号。

68.在一个实施例中,存储芯片包括n个第一芯片和第二芯片,其中,系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态之后,还包括:

69.系统级芯片向独显芯片发送第二通知信息;

70.独显芯片在接收到第二通知信息的情况下,向第二芯片发送第二重置信号,以对第二芯片进行重置;

71.独显芯片向第二芯片发送第三初始化信号,以对第二芯片进行初始化。

72.在一个实施例中,存储芯片包括n个第一芯片和第二芯片,其中,系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态之后,还包括:

73.独显芯片在接收到系统级芯片发送的第三通知信息的情况下,向第二芯片发送第三重置信号,以对第二芯片进行重置;

74.独显芯片向第二芯片发送第四初始化信号,以对第二芯片进行初始化;

75.独显芯片在控制第二芯片初始化完成的情况下,向系统级芯片发送第四通知信息;

76.系统级芯片在接收到第四通知信息的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制所述第一切换模块进入所述第一状态以及所述第二切换模块进入所述第二状态,使所述存储芯片存储所述系统级芯片的数据信息。

77.下面以一个具体实施例对本技术的方法过程加以说明。

78.独立显示芯片(即独显芯片,也称独显)在个人电脑、移动终端等电子设备中有广泛的应用,作为外置的专用图像处理单元可以带来更高帧率、更高分辨率、色彩饱和度及对比度等显示增强效果。随着移动互联网的发展,游戏和影像需求也逐步扩充到移动终端,独显芯片在移动终端上也得到应用。

79.目前,常见的应用独显芯片的硬件系统架构如图3所示,系统ddr芯片贴装在soc(系统级芯片)上面,独显芯片和soc芯片贴装在移动终端的主板上。

80.芯片间的信号被分成两类,一类为gpio(general-purpose input/output,通用输入输出接口)信号,包含相互间的所有通信信号;一类为power(电源)信号,为芯片的供电信号。soc与独显芯片间的信号走线,需要先经soc的下基板内部走线引出后,经过主板内走线再接入到独显芯片的基板上,然后与内部晶片(独显主芯片、内置ddr)连接;同理,其他芯片互连信号如图3所示,不再赘述。

81.如图4所示,带内置ddr的独显芯片,独显主芯片对外经gpio1与soc进行通信交换数据,独显主芯片通过gpio2在内置ddr芯片中存取数据;由于内置ddr芯片与独显主芯片制程不同,其工作时的操作电压值和规格要求通常有明显差异,需要设计电压转换电路或提供单独的外供电源(power2)给内置ddr使用。其中:

82.gpio1:soc与独显之间的数据接口,包含数据传输信号以及其他控制信号;

83.power1:独显的部分供电信号,为独显主芯片及其与内置ddr共用的电源;

84.gpio2:独显主芯片与内置ddr芯片的数据接口;

85.power2:独显的部分供电信号,为独显内置ddr芯片单独使用的电源信号;

86.gpio3:soc与系统ddr芯片之间的数据接口;

87.power3:系统ddr芯片的供电信号;

88.gpio4:独显与显示屏之间的数据接口;

89.gpio5:soc与显示屏之间的数据接口;

90.ddr:双倍速率同步动态随机存储器,属于dram(动态随机存储器)内存的一种;

91.chip1/2/3/4:ddr芯片内部的晶片(芯片);

92.soc:系统级芯片,包含处理器内核、数字信号处理器、存储模块、通讯接口、电源管理、射频前端等模块;

93.lcm(liquide crystal module):液晶显示模组。

94.目前,如图4所示,通常系统ddr芯片由多个芯片(chip)和物理通道组成(取决于单颗内存晶片的位宽和soc芯片的总线位宽需求),每个chip有单独的数据和控制信号(gpio3),但是电源是共用的(power3)。以图5所示的系统ddr芯片为例,由4颗(chip1/2/3/4)容量为12gb、数据位宽为16bit的ddr芯片组成4通道的总位宽为64bit、总容量为48gb的ddr芯片。

95.系统启动时,power开始上电,reset信号拉高、拉低、再拉高进行芯片重置,随后时钟信号(ck、wck)、数据信号(cs、ca)前后传输进行初始化并开始工作;由于ck和wck都是差分信号,会先经过差分信号处理模块转换成内部的时钟数字信号再提供给需要的模块使用。

96.每个通道上可以串接多个芯片(chip)以拓展内存容量(图5所示例子每个通道只挂了1颗芯片),每组通道各共用一组cs/ck/ca/dq/rdqsi/rdqso/dmi/others信号,实现不同通道的数据控制和传输,各通道的芯片的reset和power信号共用。

97.如图6所示,为chip1的原理框图,结合图5所示,其中:

98.cs_a\b\c\d:片选信号,被选中的chip才能进行数据读写和控制等操作,每个chip各1根,其中,a对应chip1,b对应chip2,c对应chip3,d对应chip4;

99.ck_a\b\c\d:差分信号对,为地址\命令\控制等数据的时钟信号,每个通道各1对;

100.wck_a\b\c\d:差分信号对,为读写内存数据的时钟信号,每个通道各1对;

101.ca_a\b\c\d:传输地址\命令\控制等数据的信号,每个通常各1组;

102.dq_a\b\c\d:输出读写内存数据的信号,每个通道各1组;

103.rdqsi_a\b\c\d:差分信号对,读操作时,内存发出的信号,soc接收后判断何时接收数据;也被用作写操作时的奇偶校验引脚;

104.rdqso_a\b\c\d:差分信号对,写操作时,soc发出的信号,内存接收后判断何时接收数据;

105.dmi_a\b\c\d:数据掩码\翻转,双向传输用于指示被屏蔽的数据和总线上被反转的数据,以及读操作时的奇偶校验等功能;每个通道各共用1组信号;

106.others:其他实现控制和校准等功能的信号;

107.amp(amplifier):差分信号放大处理模块;

108.logic control:逻辑处理模块,实现时序、控制、解码等功能;

109.memory:ddr芯片的存储单元;

110.i/o driver:读写memory模块的驱动电路,也称输入输出驱动。

111.需要说明的是,本实施例中存储模块可包括逻辑处理模块、存储单元以及读写存储单元的驱动电路。目前,系统ddr内存通常比较大,供系统级芯片(soc)使用,而现有独显芯片中单独内置ddr(例如,内存在2gb左右),很多场景并不会使用到,容易造成内存的浪费。而且独显芯片内置ddr会增加独显芯片功耗和发热量,容易导致独显芯片的性能下降。而内置ddr芯片,还需要额外增加外置电源芯片,包括ldo(low dropout regulator,低压差线性稳压器),dcdc(direct current to direct current,直流转换器)等进行供电,或者在独显内集成ldo或load switch(负载开关)以共用电源芯片,外置电源芯片时还需要增加配套元器件(电阻/电容/电感等),增加成本的同时还占用了有限的主板空间,内置ldo/load switch则会增加独显芯片面积和成本,并且转换效率较低,增加了功耗。

112.本技术实施例提供一种应用独显芯片的硬件架构和ddr芯片设计,通过特别设计的ddr芯片以及重新设计的基板走线实现独显芯片与ddr芯片(存储芯片)间的直接或间接连接,实现独显芯片与soc共用ddr芯片,使得独显芯片不用单独内置ddr芯片,也省去独显给内置ddr芯片供电的设计,最终达到节省成本并提升性能的目的。

113.如图7所示,本实施例将独显芯片内置的ddr芯片封装到系统ddr芯片中,,得到的新设计的ddr芯片,即本技术实施例的存储芯片,可以供独显和soc芯片共同使用,且共用电源。

114.存储芯片内的chip5(ddr芯片内部的一个芯片串连在其中一个chip的通道上,图7以chip1为例:

115.新增1路来自soc芯片的片选信号cs_a_1、1路来自soc芯片的模式切换信号mode、1路来自独显芯片的reset_e信号、一组来自独显芯片的数据传输及控制信号(cs_e/ck_e/wck_e/ca_e,dq_e/rdqsi_e/rdqso_e/dmi_e/others),其中,e对应chip5;

116.如图8所示,为第二芯片的结构原理图,第二芯片为chip5为例,内部相对普通芯片新增第一切换模块和第二切换模块,第一切换模块对应图8中的sw1,第二切换模块对应图8中的sw2,均为开关阵列(参考图9),包含多个开关,开关受“mode”信号控制(模式切换信号)。开关可以是如图10和图11所示的n-mos\p-mos开关管,也可以是其他类型的起到开关作用的器件。

117.第一切换模块的开关如图10所示,有两组输入信号,a组为来自上一级chip1的信号ck_a\wck_a\ca_a\reset_n及来自soc的cs_a_1信号,b组为来自独显芯片的信号cs_e/ck_e/wck_e/ca_e,其中ck_e/wck_e已经过amp模块处理;第一切换模块的输出为a或b其中一组。

118.第二切换模块的开关如图11所示,公共端(固定端)与“输入输出驱动(i/o dirver)”连接,其他两端分别为与独显芯片连接(传输的信号包括dq_e/rdqsi_e/rdqso_e/dmi_e/others)以及与soc连接(传输的信号包括dq_a/rdqsi_a/rdqso_a/dmi_a/others)。

119.本技术实施例的芯片系统结构如图12和图13所示,独显芯片的内置ddr芯片被集成在系统ddr中,ddr芯片的下基板、soc的上下基板、主板以及独显芯片的下基板需要重新布局布线,以满足:

120.1)chip5能共用ddr的power信号(

⑥

);

121.2)chip5新增的信号(参考上述chip1/2/3/4内容)能够与soc的上基板连接,使得其中的cs_a_1信号(包含在

⑤

中)与soc芯片连接,其他信号(

③

)与soc的下基板连接;

122.3)上述与soc下基板连接的信号(

③

)需要与主板连接,并在主板内走线至独显芯片的位置;

123.4)独显芯片的下基板需要预留上述信号

③

的焊盘,并与内部独显主芯片连接。

124.相比图3的原架构,省去了电源走线

④

。

125.本技术实施例的控制方法流程如下:

126.在完成硬件设计后,结合图12,以本技术实施例的存储芯片、系统级芯片和独显芯片应用于手机为例进行说明,按照如下步骤实现独显芯片与soc芯片的共用ddr芯片的功能:

127.1、开机soc启动,即系统级芯片启动,ddr通过power(

⑥

)开始上电;

128.2、模式切换信号mode信号默认拉低,系统级芯片向第一切换模块和第二切换模块发送低电平的模式切换信号mode,进入“ddr的soc模式”;

129.3、ddr芯片初始化:

130.ddr芯片的chip1/2/3/4/5(n个第一芯片包括chip1-4,第二芯片为chip5)通过信号

⑤

中reset_n进行重置,通过其中的cs\ck\wck分别进行初始化并开始正常工作,可以理解,系统级芯片可向存储芯片发送第一重置信号,以对存储芯片进行重置,系统级芯片向存储芯片发送第一初始化信号,以对所述存储芯片进行初始化;

131.4、独显芯片初始化:

132.ddr正常工作后,手机最小系统已完成启动,独显随后通过power

②

和信号

①

进行上电和初始化工作,即系统级芯片向独显芯片发送第一电源信号,以使所述独显芯片上电,以及向独显芯片发送第二初始化信号,以对独显芯片进行初始化;

133.5、准备“ddr的soc+独显模式”切换:

134.独显通过信号

①

通知soc,或者soc提前预设好独显芯片需要使用ddr芯片的场景(例如,独显芯片进行图像增强处理等场景),进入特定场景时,soc提前开始准备进入“ddr的soc+独显模式”,即系统级芯片在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,系统级芯片可开始准备进入ddr的soc+独显模式”;

135.6、内存信息搬移:

136.soc收到独显芯片通知后,开始搬移chip5中的信息至其他chip,搬移完成后将mode信号拉高,即可将所述第二芯片的数据迁移到所述n个第一芯片中的任一芯片,在数据迁移完毕的情况下,系统级芯片向第一切换模块以及第二切换模块发送高电平的模式切换信号mode,控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态;

137.7、chip5初始化:

138.模式切换信号mode信号拉高后,soc通知独显芯片通过信号

③

中的reset_e信号对chip5进行重置,再通过信号

③

中的cs\ck\wck进行初始化工作,即模式切换信号mode拉高后,系统级芯片向独显芯片发送第二通知信息,独显芯片在接收到第二通知信息后,向第二芯片发送第二重置信号,以对第二芯片进行重置,独显芯片向第二芯片发送第三初始化信号,以对第二芯片进行初始化;

139.8、完成“ddr的soc+独显模式”切换,独显芯片正常使用ddr芯片,可以运行特定功能;

140.9、准备退出“ddr的soc+独显模式”:

141.soc通知独显芯片退出特定场景(不需要再使用ddr),即系统级芯片向独显芯片发送第三通知信号;

142.10、chip5初始化

143.独显芯片先通过信号

③

中的reset_e信号对chip5进行重置,再通过信号

③

的cs\ck\wck进行初始化工作,完成后,独显通过信号

①

通知soc,即独显芯片在接收到系统级芯片发送的第三通知信息后,向第二芯片发送第三重置信号,以对第二芯片进行重置,独显芯片向第二芯片发送第四初始化信号,以对第二芯片进行初始化,独显芯片在控制第二芯片初始化完成的情况下,向系统级芯片发送第四通知信息;

144.11、完成“ddr的soc+独显模式”切换:

145.soc收到独显芯片的通知后,开始将mode信号拉低,完成模式切换,soc正常使用chip5,即系统级芯片在接收到第四通知信息后,向第一切换模块以及第二切换模块发送低电平的模式切换信号mode,控制第一切换模块进入第一状态以及第二切换模块进入第二状态,使存储芯片存储系统级芯片的数据信息,系统级芯片可使用第二芯片。

146.通过本技术实施例方案,独显芯片共用soc的ddr芯片,ddr的利用率更高,成本也能显著降低;独显芯片无需额外的ddr芯片供电设计,面积和成本可以进一步降低;将内置ddr的热量转移到系统ddr中,降低独显发热量,能够充分释放独显性能,而ddr性能影响较小。

147.以上列举了一种内存容量组合方式(12gb*4+2gb),可以根据实际需求进行组合,例如:

148.4通道总容量为48gb,每通道1个12gb的chip:

149.12gb*3+8gb+4gb(chip5);

150.通道越多,数据吞吐能力就越强,总容量为48表示chip的总容量不超过48gb,其中一个通道的12gb被拆分成了8gb+4gb,就如上chip1-5这5个芯片,chip1-3这3个chip中每个chip的容量为12gb,chip4的容量为8gb,chip5的容量为4gb,两者容量之和为12gb,chip4与chip5这种关系如同以上实施案例中的chip1和chip5的关系。

151.4通道总容量为64gb,每通道2个8g的chip:

152.8gb*3*2+8gb(chip7)+6gb(chip8)+2gb(chip9);

153.chip的总容量不超过64gb,1通道chip1和chip2容量都是8gb;2通道chip3和chip4容量都是8gb;3通道chip5和chip 6容量都是8gb;其中一个通道被拆成了8gb+6gb+2gb,即4通道chip7、chip8、chip9容量分别是8gb、6gb、2gb。

154.本技术实施例还提供一种电子设备,包括如上实施例的存储芯片。

155.本技术实施例还提供一种电子设备,包括如上实施例的芯片系统。

156.本技术实施例中的该电子设备可以是终端,也可以是除终端之外的其他设备,电子设备可以为手机、平板电脑、笔记本电脑、掌上电脑、车载电子设备、移动上网装置(mobile internet device,mid)、增强现实(augmented reality,ar)/虚拟现实(virtual reality,vr)设备、机器人、可穿戴设备、超级移动个人计算机(ultra-mobile personal computer,umpc)、上网本或者个人数字助理(personal digital assistant,pda)等,还可以为网络附属存储器(network attached storage,nas)、个人计算机(personal computer,pc)、电视机(television,tv)、柜员机或者自助机等,本技术实施例不作具体限定。

157.可选地,如图14所示,本技术实施例还提供一种电子设备1400,包括处理器1401和存储器1402,存储器1402存储可在处理器1401上运行的程序或指令,该程序或指令被处理器1401执行时实现上述控制方法实施例的各个步骤,且能达到相同的技术效果,为避免重复,这里不再赘述。

158.需要说明的是,本技术实施例中的电子设备包括上述的移动电子设备和非移动电子设备。

159.图15为实现本技术实施例的一种电子设备的硬件结构示意图。

160.该电子设备1500包括但不限于:射频单元1501、网络模块1502、音频输出单元1503、输入单元1504、传感器1505、显示单元1506、用户输入单元15015、接口单元1508、存储器1509、以及处理器1510等部件。

161.本领域技术人员可以理解,电子设备1500还可以包括给各个部件供电的电源(比如电池),电源可以通过电源管理系统与处理器1510逻辑相连,从而通过电源管理系统实现管理充电、放电、以及功耗管理等功能。图15中示出的电子设备结构并不构成对电子设备的限定,电子设备可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置,在此不再赘述。

162.其中,电子设备1500中还包括独显芯片,独显芯片与所述处理器1510连接;

163.存储器1509包括第一切换模块、第二切换模块以及连接于第一切换模块与第二切换模块之间的存储模块;

164.第一切换模块分别与处理器1510以及独显芯片连接,第二切换模块分别与处理器1510以及独显芯片连接;

165.其中,在第一切换模块处于第一状态,且第二切换模块处于第二状态的情况下,存储器1509用于存储处理器1510的数据信息;在第一切换模块处于第三状态,且第二切换模块处于第四状态的情况下,存储器1509用于存储独显芯片的数据信息。

166.在一个实施例中,存储器1509包括n个第一芯片和第二芯片,n为正整数,其中,第二芯片包括第一切换模块、第二切换模块以及存储模块;

167.其中,每个第一芯片分别与处理器1510连接,n个第一芯片中的第一目标芯片分别与处理器1510的m个第一信号端口以及k个第二信号端口连接,m、k为大于1的整数,m个第一信号端中m-1个第一信号端口还与第一切换模块连接,k个第二信号端口还与第二切换模块连接;

168.第一芯片用于存储处理器1510的数据信息,在第一切换模块处于第一状态,且第二切换模块处于第二状态的情况下,第二芯片用于存储处理器1510的数据信息;在第一切换模块处于第三状态,且第二切换模块处于第四状态的情况下,第二芯片用于存储独显芯片的数据信息。

169.在一个实施例中,第一切换模块包括m个第一开关,第二切换模块包括k个第二开关,其中,每个第一开关包括第一固定端、第一选择端和第二选择端,每个第二开关包括第二固定端、第三选择端和第四选择端;

170.其中,存储模块连接于第一固定端与第二固定端之间,m个第一开关中m-1个第二目标开关的第一选择端与处理器1510的m-1个第一信号端口一一对应连接,m个第一开关的第二选择端与处理器1510的m个第二信号端口一一对应连接,第三目标开关的第一选择端连接独显芯片的第一输出端口,第三目标开关为m个第一开关中除m-1个第二目标开关之外的开关,k个第二开关的第三选择端与处理器1510的k个第三信号端口一一对应连接,k个第二开关的第四选择端与独显芯片的k个第四信号端一一对应连接。

171.在一个实施例中,每个第一开关还包括第一控制端,每个第二开关还包括第二控制端,m个第一开关的第一控制端以及k个第二开关的第二控制端均与处理器1510的模式切换端口连接,m个第一开关的第一控制端以及k个第二开关的第二控制端用于接收处理器1510通过模式切换端口传输的模式切换信号;

172.其中,每个第一开关包括第一连接状态与第二连接状态,在第一开关处于第一连接状态下,第一开关的第一固定端与第一开关的第一选择端连通,在第一开关处于第二连接状态下,第一开关的第一固定端与第一开关的第二选择端连通,模式切换信号用于控制每个第一开关在第一连接状态与第二连接状态之间切换;

173.每个第二开关包括第三连接状态与第四连接状态,在第二开关处于第三连接状态下,第二开关的第二固定端与第二开关的第三选择端连通,在第二开关处于第四连接状态下,第二开关的第二固定端与第二开关的第四选择端连通,模式切换信号用于控制每个第二开关在第三连接状态与第四连接状态之间切换。

174.在一个实施例中,在模式切换信号为低电平信号的情况下,m个第一开关均处于第一连接状态,k个第二开关均处于第三连接状态;

175.在模式切换信号为高电平信号的情况下,m个第一开关均处于第二连接状态,k个第二开关均处于第四连接状态。

176.在一个实施例中,在处理器1510启动的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制第一切换模块进入第一状态以及第二切换模块进入第二状态,使存储器1509存储处理器1510的数据信息;

177.处理器1510在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态,使存储器1509存储独显芯片

的数据信息。

178.在一个实施例中,在处理器1510启动的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制第一切换模块进入第一状态以及第二切换模块进入第二状态之后,还包括:

179.处理器1510向存储器1509发送第一重置信号,以对存储器1509进行重置;

180.处理器1510向存储器1509发送第一初始化信号,以对存储器1509进行初始化;

181.处理器1510向独显芯片发送第一电源信号,以使独显芯片上电,以及向独显芯片发送第二初始化信号,以对独显芯片进行初始化。

182.在一个实施例中,存储器1509包括n个第一芯片和第二芯片,其中,处理器1510在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,包括:

183.处理器1510在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,将第二芯片的数据迁移到n个第一芯片中的任一芯片;

184.在第二芯片的数据迁移完毕的情况下,处理器1510向第一切换模块以及第二切换模块发送第二电平的模式切换信号。

185.在一个实施例中,存储器1509包括n个第一芯片和第二芯片,其中,处理器1510在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态之后,还包括:

186.处理器1510向独显芯片发送第二通知信息;

187.独显芯片在接收到第二通知信息的情况下,向第二芯片发送第二重置信号,以对第二芯片进行重置;

188.独显芯片向第二芯片发送第三初始化信号,以对第二芯片进行初始化。

189.在一个实施例中,存储器1509包括n个第一芯片和第二芯片,其中,处理器1510在接收到独显芯片发送的第一通知信息或在独显芯片处于预设场景的情况下,向第一切换模块以及第二切换模块发送第二电平的模式切换信号,以控制第一切换模块切换为第三状态以及第二切换模块切换为第四状态之后,还包括:

190.独显芯片在接收到处理器1510发送的第三通知信息的情况下,向第二芯片发送第三重置信号,以对第二芯片进行重置;

191.独显芯片向第二芯片发送第四初始化信号,以对第二芯片进行初始化;

192.独显芯片在控制第二芯片初始化完成的情况下,向处理器1510发送第四通知信息;

193.处理器1510在接收到第四通知信息的情况下,向第一切换模块以及第二切换模块发送第一电平的模式切换信号,以控制第一切换模块进入第一状态以及第二切换模块进入第二状态,使存储器1509存储处理器1510的数据信息。

194.应理解的是,本技术实施例中,输入单元1504可以包括图形处理器(graphics processing unit,gpu)15041和麦克风15042,图形处理器15041对在视频捕获模式或图像捕获模式中由图像捕获装置(如摄像头)获得的静态图片或视频的图像数据进行处理。显示单元1506可包括显示面板15061,可以采用液晶显示器、有机发光二极管等形式来配置显示

面板15061。用户输入单元1507包括触控面板15071以及其他输入设备15072中的至少一种。触控面板15071,也称为触摸屏。触控面板15071可包括触摸检测装置和触摸控制器两个部分。其他输入设备15072可以包括但不限于物理键盘、功能键(比如音量控制按键、开关按键等)、轨迹球、鼠标、操作杆,在此不再赘述。

195.存储器1509可用于存储软件程序以及各种数据,存储器1509可主要包括存储程序或指令的第一存储区和存储数据的第二存储区,其中,第一存储区可存储操作系统、至少一个功能所需的应用程序或指令(比如声音播放功能、图像播放功能等)等。此外,存储器1509可以包括易失性存储器或非易失性存储器,或者,存储器1509可以包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,rom)、可编程只读存储器(programmable rom,prom)、可擦除可编程只读存储器(erasable prom,eprom)、电可擦除可编程只读存储器(electrically eprom,eeprom)或闪存。易失性存储器可以是随机存取存储器(random access memory,ram),静态随机存取存储器(static ram,sram)、动态随机存取存储器(dynamic ram,dram)、同步动态随机存取存储器(synchronous dram,sdram)、双倍数据速率同步动态随机存取存储器(double data rate sdram,ddrsdram)、增强型同步动态随机存取存储器(enhanced sdram,esdram)、同步连接动态随机存取存储器(synch link dram,sldram)和直接内存总线随机存取存储器(direct rambus ram,drram)。本技术实施例中的存储器1509包括但不限于这些和任意其它适合类型的存储器。

196.处理器1510可包括一个或多个处理单元;可选地,包括但不限于应用程序和操作系统。处理器1510可集成应用处理器和调制解调处理器,其中,应用处理器主要处理操作系统、用户界面和应用程序等,调制解调处理器主要处理无线通信。可以理解的是,上述调制解调处理器也可以不集成到处理器1510中。

197.本技术实施例还提供一种可读存储介质,所述可读存储介质上存储有程序或指令,该程序或指令被处理器执行时实现上述方法实施例的各个过程,且能达到相同的技术效果,为避免重复,这里不再赘述。

198.其中,所述处理器为上述实施例中所述的电子设备中的处理器。所述可读存储介质,包括计算机可读存储介质,如计算机只读存储器rom、随机存取存储器ram、磁碟或者光盘等。

199.本技术实施例另提供了一种芯片,所述芯片包括处理器和通信接口,所述通信接口和所述处理器耦合,所述处理器用于运行程序或指令,实现上述方法实施例的各个过程,且能达到相同的技术效果,为避免重复,这里不再赘述。

200.应理解,本技术实施例提到的芯片还可以称为系统级芯片、系统芯片、芯片系统或片上系统芯片等。

201.本技术实施例提供一种计算机程序产品,该程序产品被存储在存储介质中,该程序产品被至少一个处理器执行以实现如上述方法实施例的各个过程,且能达到相同的技术效果,为避免重复,这里不再赘述。

202.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该

要素的过程、方法、物品或者装置中还存在另外的相同要素。此外,需要指出的是,本技术实施方式中的方法和装置的范围不限按示出或讨论的顺序来执行功能,还可包括根据所涉及的功能按基本同时的方式或按相反的顺序来执行功能,例如,可以按不同于所描述的次序来执行所描述的方法,并且还可以添加、省去、或组合各种步骤。另外,参照某些示例所描述的特征可在其他示例中被组合。

203.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分可以以计算机软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端(可以是手机,计算机,服务器,或者网络设备等)执行本技术各个实施例所述的方法。

204.上面结合附图对本技术的实施例进行了描述,但是本技术并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本技术的启示下,在不脱离本技术宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本技术的保护之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1