一种真随机数发生器电路

1.本发明涉及新型存储与计算技术领域,具体涉及一种真随机数发生器电路设计。

背景技术:

2.物联网(iot)是一个集信息传感与通信网络于一体的巨大网络。随着iot技术的迅速发展,智能化电子设备的数量呈现出爆发式增长,这对于信息传输和存储的安全性提出了巨大的挑战。为有效应对信息泄露、盗取等问题,需建立完善且可靠的信息安全系统。在信息的传输和存储过程中,信息安全可通过加密技术得到保障。其中,随机数的产生是整个加密系统的基础,密钥算法、安全协议、密钥的产生等均离不开随机数的应用。因此,生成高质量的独立且不可预测的随机数是信息安全技术的核心与保障。

3.随机数发生器是产生随机数序列的硬件设备,根据所产生的随机数序列的特性可分为真随机数发生器(trng)和伪随机数发生器(prng)。伪随机数产生器是基于特定的算法和逻辑处理产生随机数的,所产生的伪随机数具有周期性、可预测的特性。虽然伪随机数生成器结构简单,随机数产生速率很快,但是由于伪随机数的生成算法是以种子作为初始状态,而生成随机数的算法是确定的,因此一旦种子确定,便可以完全实现输出结果的复现与预测。对于安全性要求较高的系统而言,使用伪随机数生成器易于遭受攻击,系统的安全性无法得到保障。而真随机数发生器是基于物理过程的固有随机性产生随机数,与伪随机数相比,真随机数发生器生成的随机序列具有独立性与不可预测性,无法通过数学算法对产生的随机序列进行准确预测,大大提高了系统的安全性,因此构建高质量可靠的真随机数发生器对于保障硬件系统安全而言至关重要。基于cmos电路的随机数发生器通常利用振荡器、电阻器—放大器—模拟/数字转换器链、具有电容反馈的亚稳态元件中的热噪声作为随机熵源,除此以外随机电报噪声、氧化物软击穿后的电流扰动、与时间相关的氧化物击穿过程等均可以作为真随机数发生器的随机噪声源。然而传统的基于cmos的trng电路结构复杂,需要额外的校准电路消除偏差,以确保产生的序列的随机性,消耗了大量硬件代价与功耗。基于新型存储器件,如电阻式随机存取存储器(rram)、磁性隧道结(mtj)等,利用其内在固有的随机性构建的trng具有低面积代价、低功耗的优势。

4.然而,目前基于rram的trng在随机数产生速率、可靠性、电路开销等方面仍存在巨大挑战。例如,利用rram读出电流的随机噪声作随机源需要高精度的提取电路和额外复杂的校准电路来改善所生成随机序列的均匀性;利用扩散型rram的写时间涨落做随机源面临低速和耐久性的问题等。因此,实现更为高速、可靠、结构简单的trng具有显著的意义。

技术实现要素:

5.针对以上现有技术中存在的问题,本发明提出了一种真随机数发生器电路,利用易失性阻变器件开启的延迟时间作随机源,搭建了真随机数发生器。与传统的基于cmos电路以及目前报道的基于新型存储器件的trng相比,本发明利用易失性阻变器件构建trng,具有电路结构简单、无需后校准处理电路、随机数产生速率快的优势,实现了高速可靠的

trng。

6.本发明的技术方案如下:

7.一种真随机数发生器电路,其特征在于,采用易失性阻变器件开启的延迟时间作随机源,将易失性阻变器件与一固定电阻串联,通过固定电阻分压,将易失性阻变器件的响应电流放大,将固定电阻一端的分压引出连接到t触发器的时钟控制信号。对易失性阻变器件输入一连串幅值和宽度相同的脉冲,t触发器用于检测易失性阻变器件的响应电流是否达到阈值,当易失性阻变器件开启且响应电流超过阈值后,产生的脉冲电压高于t触发器的触发电压,使得t触发器的信号发生翻转,其输出端连接到d触发器的输入端,d触发器用来保存上一次t触发器的状态,输入脉冲信号的下降沿通过反相器产生相反的信号,用来作为d触发器的触发时钟信号,将t触发器与d触发器的输出信号引出连接至异或门xor后输出,得到表示易失性阻变器件是否开启的0/1随机比特流信号,即t触发器与d触发器输出相反,得到随机比特为“1”,t触发器与d触发器输出相同,得到随机比特为“0”。

8.进一步,本发明中使用易失性阻变器件产生随机源,易失性阻变器件采用导电桥式随机存取存储器(cbram)或阈值开关(ts)器件。其中cbram受内部导电细丝固有涨落影响,其阈值电压在不同循环内存在涨落。对阈值开关器件施加一定的电压,相变材料在电流产生的热效应下,达到阈值转变温度,发生绝缘体-金属-转变(imt),由初始绝缘状态转变为金属导电状态,电流瞬间增大,在电压撤去后,器件恢复初始高阻态。由于热扰动,器件的电流-电压曲线以及对应的操作电压呈现随机性分布。

9.进一步,对易失性阻变器件施加固定脉冲幅值与宽度的脉冲,易失性阻变器件的开启存在一定的延迟,约几十纳秒到几百微秒。由于易失性阻变器件内在固有的随机性波动,器件开启的延迟时间也呈现出随机性分布。因此,利用易失性阻变器件操作电压与开启时间的随机性,对器件施加多个相同的脉冲,易失性阻变器件在不同脉冲下对应的响应电流存在波动。根据每个脉冲对应的响应电流的大小,设置一个阈值标准,超过该阈值电流,则易失性阻变器件开启,对应的产生“1”比特,反之,若易失性阻变器件的响应电流低于该阈值电流,则为关闭状态,对应的产生“0”比特。通过调节施加脉冲的幅值或宽度可以调节最终生成的随机序列中“1”的概率,施加的脉冲的幅值或宽度越大,则易失性阻变器件开启的概率越大,最终产生的随机序列中“1”的占比越大。

10.本发明的真随机数发生器中所使用的随机源是具有典型的易失特性阻变器件,包括导电桥式随机存取存储器(cbram)、阈值开关(ts)器件等。其中阈值开关器件的中间介质层可以采用具有绝缘体-金属-转变(imt)特性的相变材料,如vo

x

、nbo

x

等。

11.本发明旨在提出一种利用易失性阻变器件的概率性开启实现电路结构简单、随机数产生速率高的真随机数发生器trng,这对于构建硬件安全性系统具有重要意义。

12.本发明的技术效果如下:

13.1、本发明与目前已有的基于新型存储器件的trng相比,利用易失性阻变器件的概率性开启作随机源,不需要额外的重置reset操作,同时由于易失性阻变器件的开启延迟时间大约为几十纳秒到几百微秒,因此操作简单且随机数生成速率快。

14.2、本发明由于电路结构简单,只用到一个反相器、t触发器、d触发器以及异或门xor,无需比较器、放大器、电容、时钟clock等,可以降低电路面积与功耗。

附图说明

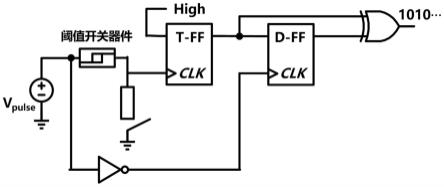

15.图1为本发明一种真随机数发生电路结构示意图。

具体实施方式

16.下面结合附图,通过具体实施例,进一步清楚、完整地阐述本发明。

17.本发明利用易失性阻变器件的概率性开启作随机源,即使用的易失性阻变器件在一定的电压扫描下,响应的电流在大于阈值电压的情况下骤然增大,在电压回扫的过程中,器件将在小于阈值电压的某一电压下电流急剧下降,回到初始高阻态。受到阻变过程中器件内部固有的涨落的影响,器件在多次直流电压扫描下,电流-电压曲线存在随机性波动,对应的阈值电压在一定区间内随机分布。这为下面器件在固定脉冲下概率性开启提供了基础。对易失性阻变器件施加一定幅值和宽度的脉冲,器件的开启存在一定的延迟,在几十纳秒到几百微秒的延迟时间后器件才会开启。对器件施加连续相同的脉冲,器件的延迟时间呈现出随机性分布,因此可以利用此物理过程的随机性作为随机源,结合后续的随机比特流提取电路,构建完整的随机数发生器。

18.图1为本发明一种真随机数发生器电路的结构图。将一易失性阻变器件与一固定电阻串联,然后将固定电阻一端的分压引出连接到t触发器的时钟控制信号,t触发器的输入端始终接高压信号,输出端连接到d触发器的输入端。输入脉冲信号的下降沿通过反相器产生相反的信号,用来作为d触发器的触发时钟信号。将t触发器与d触发器的输出信号引出连接至异或门xor后输出,得到表示易失性阻变器件是否开启的0/1随机比特流信号。

19.对易失性阻变器件输入一连串幅值和宽度相同的脉冲,器件在每一个脉冲下呈现随机的开启,通过固定电阻分压,将易失性阻变器件的响应电流放大输入到后面的检测提取电路。t触发器用于检测器件的响应电流是否达到阈值,当器件开启且响应电流超过阈值后,产生的脉冲电压高于t触发器的触发电压,使得t触发器的信号发生翻转。输入脉冲信号的下降沿通过反相器产生相反的信号,用来作为d触发器的触发时钟信号。d触发器用来保存上一次t触发器的状态。当输入脉冲的上升沿到达时,t触发器可以捕获器件的响应状态,并将响应信号“0”/“1”存下来。当输入脉冲的下降沿到来时,这个信息被存储在d触发器中。当下一个输入脉冲的上升沿到来时,器件第二次的响应状态作为1bit信息保存在t触发器内,这时d触发器还在保存上一次的信息。把t触发器与d触发器的输出通过异或门xor后输出,得到表示器件是否开启的随机比特流。假如器件开启,t触发器与d触发器输出相反,得到随机比特为“1”。假如器件没有开启,t触发器与d触发器输出相同,得到随机比特为“0”。

20.本实施例完整、详细地阐述了基于易失性开关器件的trng的实现原理及电路结构,相较基于传统cmos以及其他新型存储器件的trng,具有显著降低的硬件代价以及更加简单的操作方式,实现了高速可靠的trng。

21.最后,需要注意的是,公布实施例的目的在于帮助进一步理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附的权利要求的精神和范围内,各种替换和修改都是可能的。因此,本发明不应局限于实施例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1