一种基于泰勒展开的高性能近似除法器及误差补偿方法

1.本发明涉及近似算术运算电路设计领域,具体为一种基于泰勒展开的高性能近似除法器及误差补偿方法。

背景技术:

2.随着通信领域和人工智能技术的迅速发展,一些包含着大量数据的应用对算力的需求变得尤为重要,支撑其相关技术的硬件设备资源开销也随之迅速增长。除法是数字信号处理中至关重要的基本算术运算。在数字图像处理如二维图像背景去除,变化检测以及图形渲染等应用场景中,除法运算都发挥着重要作用。然而,由于除法算法的高度复杂性,硬件除法器在延迟和能耗方面是一个昂贵的模块。例如,amd12h系列的整数除法器指令对于16位除法具有9

–

17个周期的延迟,对于32位除法则具有9

–

25个周期的延迟,而对于相同宽度的整数乘法器指令,imul只需要三个周期就能完成。另一个例子是,相较于fpga上的相同精度乘法器,单精度浮点除法器需要1.35倍到3倍的硬件资源,运算速度上也会慢27%。

3.然而,随着新兴信号处理算法的发展,除法器在低功耗系统中发挥着越来越重要的作用,对除法器的需求也越来越大。为了在处理复杂运算的同时保持低功耗,研究人员提出了近似计算的概念。作为一种新兴计算范式,近似计算在具有容错特性的系统中有着广泛的应用场景。而在除法器应用的信号处理场景中,其中间过程甚至最终结果出现轻微误差是可以接受的,且仍然可以产生有意义的结果。例如图像处理等与人类感知相关的应用中,人脑自身强大的容错和推理能力使得我们对轻微的差别并不敏感,可以轻易纠正微小误差。因此,针对这些容错应用,可以设计基于近似计算技术的高性能的除法器。而如何设计一个计算结果不完全精确但又不影响应用正常使用的近似除法器电路已成为一个关键问题。

技术实现要素:

4.本发明针对现有技术中的不足,提供了一种基于泰勒展开的高性能近似除法器及误差补偿方法。

5.为达成上述目的,本发明采用以下技术方案:一种基于泰勒展开的高性能近似除法器,包括前导1检测电路、逻辑运算单元电路、乘累加电路和移位电路,其中:前导1检测电路包括或门和选择器电路,是用编码记录除数和被除数二进制表示中最高1的位置并输出到移位电路中,将除数和被除数移位直至前导1落在最高位上并截断为八位,之后输出被除数移位数据到逻辑运算单元电路中;逻辑运算单元电路将前导1检测电路输入的数据取反加一得到一组数据,然后将得到的数据再加一得到另一组数据,得到的两组数据输出到乘累加电路中;乘累加电路将逻辑运算单元电路输出的两组数据进行乘累加操作以生成除数的倒数结果,以分时钟周期控制进行数据乘累加操作,对乘累加计算得到的结果与精确结果

对比进行误差分析及误差补偿计算,误差补偿后的数据再与除数移位数据相乘,得到的结果输出到移位电路中;移位电路对前导1检测电路输出的位置编码与乘累加电路输出的结果进行移位操作,得到最终的近似除法器的结果。

6.进一步的,乘累加电路包括截断乘法器电路、累加器电路和加法器电路,截断乘法器电路以分时钟周期进行数据乘法计算,累加器电路以分时钟周期进行截断乘法器电路输出数据累加操作,将累加器电路输出的乘累加结果与精确结果对比进行误差分析,通过加法器电路加上常数的方法进行误差补偿得到误差补偿后的数据,二次调用截断乘法器电路将误差补偿后的数据与前导1检测电路中的除数移位数据相乘,得到的结果输出到移位电路中。

7.进一步的,截断乘法器电路包括精确部分积压缩电路、精确加法器电路和超前进位加法器电路,截断乘法器的低k位不产生部分积阵列,高k位按照阵列方式生成部分积,精确部分积压缩电路使用精确加法器电路将部分积阵列压缩成两行,输出到超前进位加法器电路中,超前进位加法器电路对压缩产生的两行部分积进行处理,得到截断乘法器电路的输出结果。

8.本发明还提供了一种基于泰勒展开的高性能近似除法器的误差补偿方法,包括以下步骤:s1:对除数的倒数使用有限阶数的泰勒展开,除法表达式为:, 为被除数,、为位置编码,、为移位数据,有限阶数泰勒展开表达式为:;s2:除数和被除数首先通过前导1检测电路得到位置编码和以及移位数据和,位置编码和输出到移位电路中,移位数据输出到逻辑运算单元电路;s3:逻辑运算单元电路对取反加1得到数据,然后对再加1得到,和输出到乘累加电路中;s4:乘累加电路通过分时钟周期调用和执行乘累加计算得数据,与精确结果对比进行误差分析及误差补偿计算得到误差补偿后的数据,二次调用截断乘法器电路将误差补偿后的数据与前导1检测电路中的除数移位数据相乘,得到,输出到移位电路中;s5:移位电路将位置编码和与进行移位计算得到最终的近似除法器输出。

9.进一步的,步骤s2中,除数和被除数通过前导1检测电路,通过将数据分段并使用或门和数据选择器找到非零段,得到前导1位置编码和,然后再左移和 位得到和。

10.进一步的,步骤s3中,逻辑运算单元电路对进行计算,表达式为:,。

11.进一步的,步骤s4中,乘累加电路对有限阶数泰勒展开执行乘累加运算,通过控制截断乘法器电路分时钟周期得到的结果并计算,最后控制累加器电路分时钟周期进行数据累加操作得到数据。

12.进一步的,步骤s4中,将乘累加计算后得到的和精确结果对比进行误差分析,通过加法器电路加上常数的方法降低误差曲线减小误差,得到误差补偿后的。

13.进一步的,步骤s4中,二次调用截断乘法器电路,误差补偿后的在截断乘法器电路中和前导1检测电路中的相乘,得到乘累加电路的输出结果,输出到移位电路中。

14.进一步的,步骤s5中,对乘累加电路的输出结果进行移位操作,最终得到近似除法器的输出,表达式为:。

15.本发明的有益效果是:1. 本发明在电路中重复调用同一截断乘法器,所以功耗面积更低,并且由于我们使用有限阶数的泰勒展开,与现有的基于泰勒展开的近似除法器相比我们的计算速度更快,用于图像处理和机器学习应用中更具优势;2. 本发明与现有的基于乘法器的近似除法器相比,精度更高,对于提升应用效果更具有优势。

附图说明

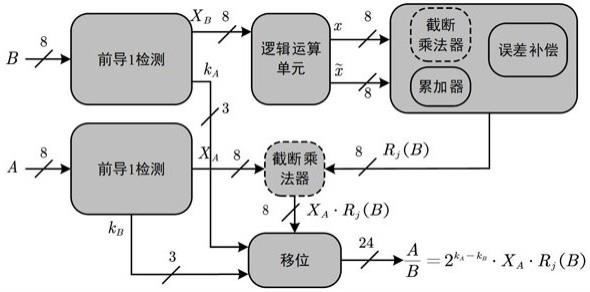

16.图1是8比特近似除法器的设计过程示意图。

17.图2是16比特前导1检测电路图;图3是乘累加电路的分时钟周期操作图;图4是8比特截断乘法器的部分积点阵图。

具体实施方式

18.以下结合附图对本发明的实施例作进一步详细描述。

19.一种基于泰勒展开的高性能近似除法器,包括前导1检测电路、逻辑运算单元电路、乘累加电路和移位电路,其中:前导1检测电路包括或门和选择器电路;乘累加电路包括截断乘法器电路、累加器电路和加法器电路;截断乘法器电路还包括精确部分积压缩电路、精确加法器电路和超前进位加法器电路。

20.本发明基于泰勒展开的高性能近似除法器采用倒数的泰勒展开方法,将除法中除数的倒数基于有限阶数的泰勒展开转换为多项式的加减法,以和被除数相乘;上述前导1检测电路是用编码记录除数和被除数二进制表示中最高1的位置并输出到移位电路中,同时将除数和被除数移位直至前导1落在最高位上并截断为八位以适应截断乘法器的位宽,之后输出到逻辑运算单元电路中;上述逻辑运算单元电路将前导1检测电路输入的数据取反加1,所得数据再加1,分

别得到两组数据输出到乘累加电路中;上述乘累加电路将逻辑运算单元电路输出的数据进行乘累加操作以生成除数的倒数结果,其中乘法的操作通过截断乘法器电路完成,累加器电路对乘法器电路的数据进行累加,加法器电路对误差补偿分析后的数据进行补偿误差,之后再输出到截断乘法器电路中;上述的误差补偿分析是将累加器电路的输出和精确结果进行数据分析统计误差曲线,精确结果是直接使用乘法符号进行计算,数据分析统计误差曲线是使用matlab仿真对比,再通过加法器电路进行常数误差补偿减小误差;上述截断乘法器电路包括精确部分积压缩电路、精确加法器电路和超前进位加法器电路,截断乘法器的低k位不产生部分积阵列,高k位按照阵列方式生成部分积,精确部分积压缩电路使用精确加法器电路将部分积阵列压缩成两行,输出到超前进位加法器电路中,超前进位加法器电路对压缩产生的两行部分积进行处理,得到截断乘法器的结果;上述移位电路对乘累加电路输出的被除数乘以除数的倒数的结果进行移位操作,得到最终的近似除法器的结果。

21.如图1中8比特近似除法器设计流程图所示,除数和被除数首先通过前导1检测电路得到3比特前导1位置编码和以及8比特移位数据和。逻辑运算单元对取反加1得到8比特数据,然后对再加1得到。和输出到乘累加电路中,通过分时钟周期调用截断乘法器和累加器计算有限阶数泰勒展开的。通过对比精确数据进行误差分析,使用常数补偿方法降低误差曲线达到减小误差的目的。本发明使用的常数补偿方法中,的小数部分位宽为6比特,因此误差补偿的步长设置在。补偿后的输出到截断乘法器电路中和相乘,得到乘法结果 ,最后结合前导1检测电路输出的前导1位置编码对该乘法结果进行移位得到最终的除法输出。

22.图2为16比特前导1检测电路图,假设除法器输入位宽为,其中。图中为输入16比特数据,为输出的位置编码,分别是对应的二分段非零数据。前导1检测电路首先将输入数据分段,找到其中的非零段并将高位数据输入或门中,位置编码的最高位即为或门的输出。然后对此非零段继续二分段找到其中的非零段,再将高位数据输入或门中,位置编码的次高位即为或门的输出,重复此操作直到剩下两位数据,最低一位的位置编码即等于这两位数据的高位。对于位的除法器输入,需要位的位置编码。

23.图3为乘累加器的分时钟周期操作图,图中即计算括号中的乘累加部分,对于本发明设计的近似除法器,其泰勒展开阶数为5阶,即乘累加器的计算表达式为。如图3所示,第1个时钟周期截断乘法器计算,累加器输出即为;第2个时钟周期截断乘法器计算,累加器输出;第3个时钟周期截断乘法器计算,累加器输出。

24.图4为8比特截断乘法器的部分积点阵图。当生成部分积时,低7位的部分积直接截断即不生成,而高位部分积通过与门电路生成。部分积压缩时,本实例使用精确的4-2压缩器以及全加器压缩部分积,直到最后生成两行部分积。所述超前进位加法器计算最后两行

部分积的结果,得到截断乘法器的最终结果。

25.以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1