基于全连接结构的L0BTB容错设计系统及方法与流程

本发明涉及分支目标缓冲器容错设计领域,特别涉及一种基于全连接结构的l0btb容错设计系统及方法。

背景技术:

1、处理器在运行过程中可能会出现两种潜在错误,第一种是芯片的硬件电路出现问题;第二种是受到外界环境干扰,导致高能粒子撞击引起瞬态故障,具体而言,即处理器设计中分支预测模块中l0 btb(l0 branch target buffer)会受到外界环境辐照影响,例如单粒子翻转(seu)(single event upset)。对于第一种错误,是电路单元产生的永久性故障,不可恢复。第二种错误通过增加冗余技术,能够消除瞬态故障带来的影响。

2、分支预测模块是处理器设计过程中关键的模块之一,它对当前指令地址进行预测,将预测结果作为目标指令地址,发送给pc寄存器进行取指。l0 btb作为分支预测模块中关键的一环,如果表项出现翻转错误,就可能导致将带有翻转错误的表项输出给cache模块。那么即使cache的容错设计成功率达到100%,也会带来错误的目标指令。因此对l0 btb的容错设计,有助于提升cache取指令的准确率,维护处理器能够正常和稳定的运行。

3、关于cache和寄存器堆的容错设计方法已经很成熟,并且被成功部署在了各种不同的处理器中使用。但是关于l0 btb的容错设计并没有专门的研究工作,将cache和寄存器堆的容错设计工作直接用于l0 btb,会导致命中率下降的问题。因此需要设计一种专门针对全连接结构的l0 btb的容错设计方案。

技术实现思路

1、本发明的目的是提供一种基于全连接结构的l0 btb容错设计系统及方法,旨在通过编码逻辑校验,来降低l0 btb收到外界环境辐射,例如单粒子翻转的影响,保证分支预测模块的正常运转,以及cache取指令功能的正常稳定执行。

2、本发明解决其技术问题,采用的技术方案是:

3、一方面,本发明提出的是一种基于全连接结构的l0 btb容错设计系统,包括:

4、主-从冗余模块,包括两个l0 btb结构,两个结构完全相同,均包含多个表项,当进行l0 btb预测目标指令时,通过两个l0 btb结构输出预测结果;

5、校验决策模块,包括两个校验模块和一个决策模块,两个校验模块分别对应于主模块和从模块,用于分别对两个l0 btb结构的预测结果进行校验,两个校验模块的结构完全一致,均输出使能信号和校验结果,如果使能信号和校验结果都为1,则说明该表项是候选表项,如果其中一个为0,则该表项认为不是可选的目标表项。

6、作为进一步优化,所述两个l0 btb结构分别为l0 btb1和l0 btb2,所述l0 btb1和l0 btb2均包含40个表项。

7、作为进一步优化,每个表项中包含的内容有:当前指令地址、目标指令地址、使能信号以及异或校验值。

8、作为进一步优化,在写表项时,先将当前地址经过一个异或逻辑,获取当前地址的异或校验码,并将当前地址和异或校验码拼接后作为输入分别输入至两个l0 btb结构。

9、作为进一步优化,在读表项时,当前指令地址同时访问两个l0 btb结构,通过当前指令地址与目标指令地址进行比对,确定是否命中l0 btb,如果命中其中一个l0 btb,使能信号值为1,获取该表项内容并对该表项进行异或校验,如果该表项的异或校验值与表项中存储的校验值相同,则将该表项作为候选表项,根据获得的候选表项进行决策,如果校验结果表明,没有出现候选表项,则认为当前指令地址没有命中l0 btb。

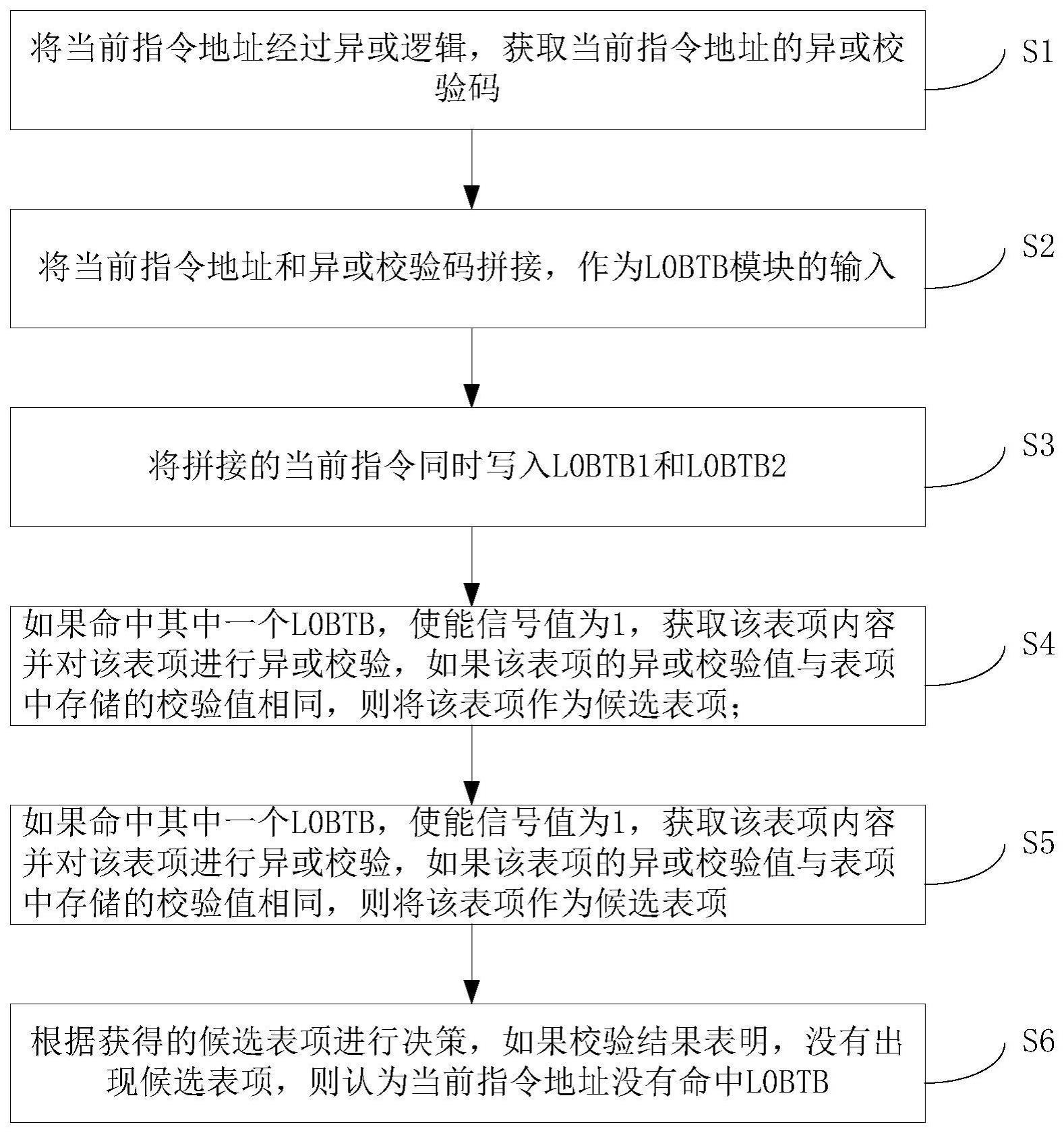

10、另一方面,本发明提出的是一种基于全连接结构的l0 btb容错设计方法,应用于所述的基于全连接结构的l0 btb容错设计系统,包括如下步骤:

11、将当前指令地址经过异或逻辑,获取当前指令地址的异或校验码;

12、将当前指令地址和异或校验码拼接,作为l0 btb模块的输入;

13、将拼接的当前指令同时写入l0 btb1和l0 btb2;

14、当前指令地址同时访问l0 btb1和l0 btb2,通过当前指令地址与目标指令地址进行比对,确定是否命中l0 btb;

15、如果命中其中一个l0 btb,使能信号值为1,获取该表项内容并对该表项进行异或校验,如果该表项的异或校验值与表项中存储的校验值相同,则将该表项作为候选表项;

16、根据获得的候选表项进行决策,如果校验结果表明,没有出现候选表项,则认为当前指令地址没有命中l0 btb。

17、作为进一步优化,将拼接的当前指令同时写入l0 btb1和l0 btb2时,设置计数器来确定表项的放置位置,替换策略为先进先出策略。

18、本发明的有益效果是:通过上述基于全连接结构的l0 btb容错设计系统及方法,通过主-从冗余模块保证当前指令地址能够在两个相同的l0 btb结构中匹配到正确的表项,通过校验决策模块,能够对对两个l0 btb结构的预测结果进行校验,输出正确的表项。能够大大降低l0 btb收到外界环境辐射,例如单粒子翻转的影响,保证分支预测模块的正常运转,以及cache取指令功能的正常稳定执行。本发明不仅对于全相联的l0 btb是受用的,还可以将其用于分支预测中的返回地址堆栈(ras)(return address stack)模块,证明本发明提出的方案对多种不同的结构都具有通用性。

技术特征:

1.基于全连接结构的l0 btb容错设计系统,其特征在于,包括:

2.根据权利要求1所述的基于全连接结构的l0 btb容错设计系统,其特征在于,所述两个l0 btb结构分别为l0 btb1和l0 btb2,所述l0 btb1和l0 btb2均包含40个表项。

3.根据权利要求1所述的基于全连接结构的l0 btb容错设计系统,其特征在于,每个表项中包含的内容有:当前指令地址、目标指令地址、使能信号以及异或校验值。

4.根据权利要求1-3任意一项所述的基于全连接结构的l0 btb容错设计系统,其特征在于,在写表项时,先将当前地址经过一个异或逻辑,获取当前地址的异或校验码,并将当前地址和异或校验码拼接后作为输入分别输入至两个l0 btb结构。

5.根据权利要求4所述的基于全连接结构的l0 btb容错设计系统,其特征在于,在读表项时,当前指令地址同时访问两个l0 btb结构,通过当前指令地址与目标指令地址进行比对,确定是否命中l0 btb,如果命中其中一个l0 btb,使能信号值为1,获取该表项内容并对该表项进行异或校验,如果该表项的异或校验值与表项中存储的校验值相同,则将该表项作为候选表项,根据获得的候选表项进行决策,如果校验结果表明,没有出现候选表项,则认为当前指令地址没有命中l0 btb。

6.基于全连接结构的l0 btb容错设计方法,应用于权利要求1-5任意一项所述的基于全连接结构的l0 btb容错设计系统,其特征在于,包括如下步骤:

7.根据权利要求6所述的基于全连接结构的l0 btb容错设计方法,其特征在于,将拼接的当前指令同时写入l0 btb1和l0 btb2时,设置计数器来确定表项的放置位置,替换策略为先进先出策略。

技术总结

本发明涉及分支目标缓冲器容错设计领域,提出了一种基于全连接结构的L0 BTB容错设计系统及方法,包括:将当前指令地址经过异或逻辑,获取当前指令地址的异或校验码;将当前指令地址和异或校验码拼接同时写入两个L0 BTB;当前指令地址同时访问两个L0 BTB,通过当前指令地址与目标指令地址进行比对,确定是否命中L0 BTB;如果命中其中一个L0 BTB,使能信号值为1,获取该表项内容并对该表项进行异或校验,如果该表项的异或校验值与表项中存储的校验值相同,则将该表项作为候选表项;根据获得的候选表项进行决策,如果校验结果表明,没有出现候选表项,则认为当前指令地址没有命中L0 BTB。

技术研发人员:年嘉伟,刘鸿瑾,梁宗南,杨孟飞,张绍林,杨一楠,高鑫,高嘉轩,孙印昂

受保护的技术使用者:北京轩宇空间科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!