OCV缩放因子的获取方法与流程

ocv缩放因子的获取方法

技术领域

1.本发明涉及一种半导体集成电路的制造方法,特别是涉及一种片上变化(on chip variation,ocv)缩放因子的获取方法。

背景技术:

2.由于硅衬底芯片工艺的限制,同一颗芯片上不同位置的晶体管的性能会有差异。芯片设计仿真所需的时序模型,不同器件在同一时间仅考虑相同pvt(process voltage temperature)的时序,pvt是指芯片工作条件,静态时序分析通常是在特定工作条件下执行的;而实际上芯片的pvt不会落在同一点上,而是一个范围;如有时序关系的一些单元,有的pvt在0.99/1.17v/24℃,而有些pvt则在1.01/1.21v/30℃;这种情形下的时序分析必然有误差,那么就要考虑留有裕量。其中,时序裕量是指足够的数据建立、保持时间。如图1所示,是现有时序电路的数据建立和保持时间的示意图;曲线101为时序电路如d触发器(ff)的输入数据的曲线,曲线102为现有时序电路输入的时钟信号曲线;时序电路要实现正确的数据输出,则需要在曲线102的上升沿之前的数据建立时间内曲线101中的数据信号需要保持稳定以及在曲线102的上升沿之后的数据保持时间内曲线101中的数据信号需要保持稳定。图1中,数据建立时间采用tsetup表示,数据保持时间采用thold表示。也即,数据信号保持稳定的起点需要早于时钟信号的上升沿减去tsetup,以及数据信号保持稳定的终点需要晚于时钟信号的上升沿加thold,对应的差值越大,则时序裕值也就越大。

3.由于芯片上具有ocv,ocv是指在同一芯片上,由于工艺的误差及芯片实际工作环境的差异,导致不同位置的器件性能不一样。所以,同一芯片上不同位置处对应的时序电路的thold,tsetup具有由于ocv引起的差异,为了克服ocv的差异的不利影响,时序裕值需要增大,在设计中,时序裕值和ocv缩放因子相对应,通过ocv缩放因子能改变时序电路对应的路径如发射路径或捕获路径上的器件单元的延迟时间,从而得到对应的时序裕值。

4.现有方法中,设置裕量会采用其他厂商或工艺平台的参考值,但是实际上不同工艺的ocv情况不尽相同。ocv情况不同时,对应的时序裕量设置应当也不同,为了使各种不同ocv情况下数据建立和保证都满足要求,现有方法需要设置较大的时序裕量。原因为:因为芯片上不同位置的晶体管性能会有差异,有时序关系的相同单元在芯片上所处位置不同,门级延时也会有差异,而库时序模型中pvt只是描述一个“点”,所以留有一定数值时序裕量,才能保证电路逻辑不会出错。

5.但是,现有方法具有如下不利后果:

6.在芯片设计时序收敛时,由于时序裕量过大,修复时序将会增加许多冗余单元,导致芯片局部连线困难,或者说时序收敛较难;反之,如果裕量太小,时序问题会导致芯片功能出错。

技术实现要素:

7.本发明所要解决的技术问题是提供一种ocv缩放因子的获取方法,能获取被测试

的时序电路如触发器的建立时间和保持时间的最佳裕量值,从而能防止时序电路的建立时间和保持时间的裕量值过大所带来的缺陷如需要插入过多的冗余逻辑电路以及增加布局布线难度,从而有利于设计时序收敛;同时还能防止时序电路的建立时间和保持时间的裕量值过小所带来因逻辑时序问题而产生的芯片功能错误,所以能提高时序电路的建立时间和保持时间的裕量值的可靠性。

8.为解决上述技术问题,本发明提供的ocv缩放因子的获取方法包括如下步骤:

9.步骤一、在芯片的多处设置第一时序电路,所述第一时序电路包括第一信号输入端、第一时钟信号输入端和第一信号输出端。

10.所述第一时序电路的第一信号输入端和第一信号输入电路相连。

11.所述第一时序电路的第一时钟信号输入端和第一时钟信号相连,所述第一时钟信号由第一时钟输入电路输出,所述第一时钟输入电路的输入端连接输入时钟信号。

12.所述第一时序电路具有第一建立时间和第一保持时间;所述芯片的各位置处的所述第一时序电路的第一建立时间和第一保持时间具有ocv差异。

13.所述第一信号输入电路具有第一延迟时间,所述第一延迟时间的大小能通过所述第一时钟输入电路调节。

14.所述第一时钟输入电路具有第二延迟时间,所述第二延迟时间的大小能通过所述第一时钟输入电路调节。

15.步骤二、设定所述第一建立时间的裕量值以及所述第一保持时间的裕量值。

16.步骤三、选取所述芯片的多处的所述第一时序电路,按照所设定的所述第一建立时间的裕量值以及所述第一保持时间的裕量值调节所述第一延迟时间和所述第二延迟时间,使得所述第一时序电路的所述第一信号输入端的数据稳定时间满足所述第一建立时间和所述第一保持时间的要求。

17.步骤四、重复步骤二和步骤三直至得到所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值。

18.进一步的改进是,步骤一中,所述第一时序电路采用第一触发器。

19.进一步的改进是,所述第一触发器采用第一d触发器。

20.进一步的改进是,所述第一信号输入电路包括第二时序电路和组合逻辑(combination logic)电路。

21.所述第二时序电路包括第二信号输入端、第二时钟信号输入端和第二信号输出端。

22.所述第二时序电路的第二信号输入端和输入信号相连。

23.所述第二时序电路的第二时钟信号输入端和第二时钟信号相连,所述第二时钟信号由第二时钟输入电路输出,所述第二时钟输入电路的输入端连接所述输入时钟信号。

24.所述第二时序电路的第二信号输出端连接所述组合逻辑电路的输入端,所述组合逻辑电路的输出端连接所述第一时序电路的第一信号输入端。

25.所述第一延迟时间的大小能通过所述所述组合逻辑电路调节。

26.进一步的改进是,所述第二时序电路采用第二触发器。

27.进一步的改进是,所述第二触发器采用第二d触发器。

28.进一步的改进是,步骤二中,同时设定所述第一建立时间的多级裕量值以及同时

所述第一保持时间的多级裕量值。

29.进一步的改进是,步骤四中,在进行重复步骤二和步骤三的循环步骤中,采用逐次逼近的方式得到所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值。

30.进一步的改进是,ocv缩放因子和所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值成比例。

31.进一步的改进是,步骤三中,所述第一时序电路的所述第一信号输入端的数据稳定时间满足所述第一建立时间和所述第一保持时间的要求包括:

32.所述第一信号输入端的数据稳定阶段的起始时间早于所述第一时钟信号的上升沿减所述第一建立时间。

33.所述第一信号输入端的数据稳定阶段的终点时间晚于所述第一时钟信号的上升沿加所述第一保持时间。

34.进一步的改进是,所述第一时钟信号的上升沿减所述第一建立时间之后和所述第一信号输入端的数据稳定阶段的起始时间的差值大于所设定的所述第一建立时间的裕量值。

35.进一步的改进是,所述第一时钟信号的上升沿加所述第一保持时间之后和所述第一信号输入端的数据稳定阶段的终点时间的差值大于所设定的所述第一保持时间的裕量值。

36.进一步的改进是,所述第一信号输入端的数据稳定阶段的起始时间由所述第一延迟时间调节。

37.所述第一时钟信号的上升沿的时间由所述第二延迟时间调节。

38.进一步的改进是,所述第一信号输入端的数据稳定阶段的终点时间和起始时间相差一个时钟周期。

39.进一步的改进是,步骤二中,所设定所述第一建立时间的裕量值的级数为3级以上以及所述第一保持时间的裕量值级数和所述第一建立时间的裕量值的级数相同。

40.进一步的改进是,步骤四中,所述第一建立时间的最佳裕量值为在能消除所述第一建立时间的ocv差异的条件下所得到的最小裕量值。

41.所述第一保持时间的最佳裕量值为在能消除所述第一保持时间的ocv差异的条件下所得到的最小裕量值。

42.本发明通过设置具有能调节第一延迟时间的第一信号输入电路以及能调节第二延迟时间的第一时钟输入电路,通过不断循环进行设置第一建立时间的裕量值以及第一保持时间的裕量值以及进行第一延迟时间和第二延迟时间的测试,最终能得到第一建立时间的最佳裕量值以及第一保持时间的最佳裕量值,所以,本发明能获取被测试的时序电路如触发器的建立时间和保持时间的最佳裕量值,从而能防止时序电路的建立时间和保持时间的裕量值过大所带来的缺陷如需要插入过多的冗余逻辑电路以及增加布局布线难度,从而有利于设计时序收敛;同时还能防止时序电路的建立时间和保持时间的裕量值过小所带来因逻辑时序问题而产生的芯片功能错误,所以能提高时序电路的建立时间和保持时间的裕量值的可靠性。

附图说明

43.下面结合附图和具体实施方式对本发明作进一步详细的说明:

44.图1是现有时序电路的数据建立和保持时间的示意图;

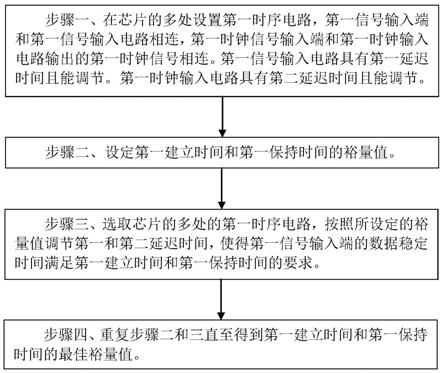

45.图2是本发明实施例ocv缩放因子的获取方法的流程图;

46.图3是本发明实施例ocv缩放因子的获取方法中的电路图;

47.图4是本发明实施例ocv缩放因子的获取方法整体实施流程图。

具体实施方式

48.如图2所示,是本发明实施例ocv缩放因子的获取方法的流程图;如图3所示,是本发明实施例ocv缩放因子的获取方法中的电路图;本发明实施例ocv缩放因子的获取方法包括如下步骤:

49.步骤一、在芯片的多处设置第一时序电路201,所述第一时序电路201包括第一信号输入端d2、第一时钟信号输入端clk2和第一信号输出端q2。

50.所述第一时序电路201的第一信号输入端d2和第一信号输入电路相连。

51.所述第一时序电路201的第一时钟信号输入端clk2和第一时钟信号相连,所述第一时钟信号由第一时钟输入电路204输出,所述第一时钟输入电路204的输入端连接输入时钟信号clkin。

52.所述第一时序电路201具有第一建立时间和第一保持时间;所述芯片的各位置处的所述第一时序电路201的第一建立时间和第一保持时间具有ocv差异。

53.本发明实施例中,所述第一时序电路201采用第一触发器,图1中,所述第一时序电路201也采用ff2表示。在一些较佳实施例中,所述第一触发器采用第一d触发器。

54.所述第一信号输入电路具有第一延迟时间,所述第一延迟时间的大小能通过所述第一时钟输入电路204调节。

55.本发明实施例中,所述第一信号输入电路包括第二时序电路202和组合逻辑电路203。

56.所述第二时序电路202包括第二信号输入端d1、第二时钟信号输入端clk1和第二信号输出端q1。

57.所述第二时序电路202的第二信号输入端d1和输入信号in相连。

58.所述第二时序电路202的第二时钟信号输入端clk1和第二时钟信号相连,所述第二时钟信号由第二时钟输入电路205输出,所述第二时钟输入电路205的输入端连接所述输入时钟信号clkin。图3中显示了,所述第二时钟信号相对于所述输入时钟信号clkin的延迟时间为t

clk1

。

59.所述第二时序电路202的第二信号输出端q1连接所述组合逻辑电路203的输入端,所述组合逻辑电路203的输出端连接所述第一时序电路201的第一信号输入端d2。

60.所述第一延迟时间的大小能通过所述所述组合逻辑电路203调节。

61.所述第二时序电路202采用第二触发器,图3中,所述第二时序电路202也采用ff1表示。在一些较佳实施例中,所述第二触发器采用第二d触发器。

62.所述第一时钟输入电路204具有第二延迟时间,所述第二延迟时间的大小能通过所述第一时钟输入电路204调节。所述第二延迟时间即为所述第一时钟信号相对于所述输

入时钟信号clkin的延迟时间,图3中显示了,所述第一时钟信号相对于所述输入时钟信号clkin的延迟时间为t

clk2

。t

clk1

和t

clk2

具有偏差(skew)。

63.步骤二、设定所述第一建立时间的裕量值以及所述第一保持时间的裕量值。

64.步骤三、选取所述芯片的多处的所述第一时序电路201,按照所设定的所述第一建立时间的裕量值以及所述第一保持时间的裕量值调节所述第一延迟时间和所述第二延迟时间,使得所述第一时序电路201的所述第一信号输入端d2的数据稳定时间满足所述第一建立时间和所述第一保持时间的要求。

65.本发明实施例中,所述第一时序电路201的所述第一信号输入端d2的数据稳定时间满足所述第一建立时间和所述第一保持时间的要求包括:

66.所述第一信号输入端d2的数据稳定阶段的起始时间早于所述第一时钟信号的上升沿减所述第一建立时间。该特征可以采用公式(1)表示为:

67.t

(c-q) + t

logic + t

setup

ꢀ‑ꢀ

t

skew 《 t

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1);

68.其中,t

(c-q)

表示ff1即所述第二时序电路202的clk1端输入到q1端输出的延时;

69.t

logic

表示combinational logic部分即所述组合逻辑电路203的延时;

70.t

setup

表示ff2即所述第一时序电路201的d2端要求的数据保持时间;

71.t

skew

表示t

clk1

与t

clk2

的延时差值;

72.t表示clkin的时钟周期。

73.所述第一信号输入端d2的数据稳定阶段的终点时间晚于所述第一时钟信号的上升沿加所述第一保持时间。该特征可以采用公式(2)表示为:

74.t

(c-q) + t

logic

ꢀ‑ꢀ

t

skew 》 t

hold

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2);

75.其中,t

hold

表示ff2的d2端要求的数据建立时间;

76.进一步,所述第一时钟信号的上升沿减所述第一建立时间之后和所述第一信号输入端d2的数据稳定阶段的起始时间的差值大于所设定的所述第一建立时间的裕量值。

77.所述第一时钟信号的上升沿加所述第一保持时间之后和所述第一信号输入端d2的数据稳定阶段的终点时间的差值大于所设定的所述第一保持时间的裕量值。

78.本发明实施例中,所述第一信号输入端d2的数据稳定阶段的起始时间由所述第一延迟时间调节。所述第一延迟时间为t

clk1、

t

(c-q)

和t

logic

的和,所述第一延迟时间则是由t

logic

调节。

79.而所述第一信号输入端d2的数据稳定阶段的终点时间和起始时间相差一个时钟周期。

80.所述第一时钟信号的上升沿的时间由所述第二延迟时间即t

clk2

调节。

81.步骤四、重复步骤二和步骤三直至得到所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值。

82.本发明实施例中,步骤二中同时设定所述第一建立时间的多级裕量值以及同时所述第一保持时间的多级裕量值。在一些较佳实施例中,步骤二中,所设定所述第一建立时间的裕量值的级数为3级以上以及所述第一保持时间的裕量值级数和所述第一建立时间的裕量值的级数相同。

83.步骤四中,在进行重复步骤二和步骤三的循环步骤中,采用逐次逼近的方式得到所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值。

84.ocv缩放因子和所述第一建立时间的最佳裕量值以及所述第一保持时间的最佳裕量值成比例。

85.步骤四中,所述第一建立时间的最佳裕量值为在能消除所述第一建立时间的ocv差异的条件下所得到的最小裕量值。

86.所述第一保持时间的最佳裕量值为在能消除所述第一保持时间的ocv差异的条件下所得到的最小裕量值。

87.本发明实施例通过设置具有能调节第一延迟时间的第一信号输入电路以及能调节第二延迟时间的第一时钟输入电路204,通过不断循环进行设置第一建立时间的裕量值以及第一保持时间的裕量值以及进行第一延迟时间和第二延迟时间的测试,最终能得到第一建立时间的最佳裕量值以及第一保持时间的最佳裕量值,所以,本发明实施例能获取被测试的时序电路如触发器的建立时间和保持时间的最佳裕量值,从而能防止时序电路的建立时间和保持时间的裕量值过大所带来的缺陷如需要插入过多的冗余逻辑电路以及增加布局布线难度,从而有利于设计时序收敛;同时还能防止时序电路的建立时间和保持时间的裕量值过小所带来因逻辑时序问题而产生的芯片功能错误,所以能提高时序电路的建立时间和保持时间的裕量值的可靠性。

88.如图4所示,是本发明实施例ocv缩放因子的获取方法整体实施流程图,包括如下步骤:

89.步骤s101、设计扫描链电路,制定多级裕量值。

90.步骤s102、作成版图设计数据。

91.在进行步骤s102的过程中同时进行步骤s103,即执行延时调整脚本。延时调整脚本能对版图设计数据对应的电路中的器件单元的延伸进行调整。

92.经过上述步骤s101至s103之后就能得到本发明实施例的步骤一和步骤二。

93.之后进行步骤s104、根据芯片测试结果得出ocv缩放因子。步骤s104则是采用本发明实施例的步骤二至步骤四实现。

94.在获得所述ocv缩放因子后,进行步骤s105、结束。

95.本发明实施例通过调节combinational logic和t

clk2

的延时,使得寄存器即触发器ff2的数据输入端d2满足建立及保持时间;

96.通过选取芯片中多点位置处的ff2,制定多级裕量值,逐次逼近的方式得出合适的时序裕量值。在一些具体实施例中,多级裕量值参考表一所示:

97.表一

[0098][0099]

test_chip1表示测试芯片,wc表示最坏情形(worst case),bc表示最好情形(best case)。set ratio for data表示ocv采用百分比表示;uncertainty表示设置的多级裕量值,可以看出,在wc和bc时都设置了3级裕量值,分别为150ps,100ps和50ps。

[0100]

和现有方法相比:

[0101]

本发明实施例能提供可靠的时序裕量,保证不会因为逻辑时序问题导致芯片功能错误。

[0102]

本发明实施例还同时能保留合适的裕量值,既可避免插入过多冗余逻辑,增加布局布线难度,也有益于芯片设计时序收敛。

[0103]

本发明实施例实现的原理为:通过调节combinational logic和tclk2的延时,使得寄存器ff2的数据输入端d满足建立及保持时间;

[0104]

当tclk2》tclk1时,调节combinational logic或tclk2的延时使之满足上面的公式(1)和公式(2)。

[0105]

本发明实施例最好能根据设定的多级裕量值(150ps,100ps,50ps),由芯片测试结果确定ocv缩放因子。

[0106]

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1