一种连接铜排等效电路阻抗仿真方法、设备和介质与流程

1.本发明涉及电力电子领域,具体涉及一种连接铜排等效电路阻抗仿真方法、设备和介质。

背景技术:

2.随着新能源电动汽车产业的飞速发展,电动汽车逐步走入千家万户,广泛为消费者所选择。电动汽车的可靠性,安全性,耐久性等因素深受大家重视。其中,电池组件作为电动汽车的核心动力来源,对电池包含的所有组件进行深入研究非常有必要。连接铜排作为电动汽车电力连接的关键部件,其电力传输性能,电磁兼容性能,稳定性能等因素左右着电力传输及电力系统的稳定程度。

3.为了合理地利用连接铜排,在其设计生产阶段,需要彻底摸清其电气性能,包括其特性阻抗,寄生电容,寄生电感,寄生电阻等。实验测试往往是体现电气数据最为直观的方式,但是往往存在以下弊端:测试需要送往特定的实验室,而这类实验室分布并不广泛,且实验测试花费较为昂贵;每次实验测试只能确定唯一一种连接铜排的相关参数,一旦其物理参数中的一种或多种发生改变,整个测试工作就需要重新进行,实验测试的周期长。因此,当需要进行大批量连接铜排的电气参数摸底时,实验测试的长周期,高费用性导致了实验测试不再适用,需要寻求一种新的方法。

技术实现要素:

4.为解决现有技术所存在的技术问题,本发明提供一种连接铜排等效电路阻抗仿真方法、设备和介质,通过三维建模计算和仿真技术,使用模拟的技术手段获取连接铜排的阻抗特性曲线,可以快速获取不同连接铜排的特性阻抗曲线,该方法低耗费,解决了实验测试高费用的问题。

5.本发明的第一个目的在于提供一种连接铜排等效电路阻抗仿真方法。

6.本发明的第二个目的在于提供一种计算机设备。

7.本发明的第三个目的在于提供一种存储介质。

8.本发明的第一个目的可以通过采取如下技术方案达到:

9.一种连接铜排等效电路阻抗仿真方法,所述方法包括:

10.获取连接铜排的模型信息,通过三维制图软件对铜排进行数字化建模,得到连接铜排的三维模型;

11.将连接铜排的三维模型导入电磁仿真软件中,建立连接铜排的电磁仿真模型;

12.通过电磁仿真模型获取连接铜排的寄生参数,根据获取的连接铜排的寄生参数,建立连接铜排的等效电路拓扑结构;

13.根据连接铜排的等效电路拓扑结构绘制连接铜排的等效电路模型;

14.通过电路仿真软件建立连接铜排等效电路模型的阻抗仿真电路,添加端口激励进行扫频计算,得到连接铜排等效电路模型的阻抗仿真电路的特性阻抗曲线。

15.优选的技术方案中,所述通过三维制图软件对铜排进行数字化建模,得到连接铜排的三维模型,包括:三维制图软件采用cad软件,根据连接铜排实物的模型信息,通过cad软件绘制铜排导电材料部分的几何体和绝缘体部分的几何体,将铜排导电材料部分的几何体和绝缘体部分的几何体组合,得到连接铜排的三维模型。

16.所述根据获取的连接铜排的寄生参数,建立连接铜排的等效电路拓扑结构,包括:根据电路原理通过q3d软件仿真分别获取:u相与v相之间存在的寄生电容、v相与w相之间存在的寄生电容、u相与v相之间存在的寄生电感、v与w相之间存在的寄生电感、u相的寄生电阻、v相的寄生电阻、w相的寄生电阻、u相的寄生电感、v相的寄生电感、w相的寄生电感,故根据获取到的寄生电容、寄生电阻和寄生电感,搭建连接铜排等效电路拓扑结构。

17.本发明的第二个目的可以通过采取如下技术方案达到:

18.一种计算机设备,包括处理器以及用于存储处理器可执行程序的存储器,所述处理器执行存储器存储的程序时,实现上述的一种连接铜排等效电路阻抗仿真方法。

19.本发明的第三个目的可以通过采取如下技术方案达到:

20.一种存储介质,存储有程序,所述程序被处理器执行时,实现上述的一种连接铜排等效电路阻抗仿真方法。

21.本发明与现有技术相比,具有如下优点和有益效果:

22.本发明提供了一种连接铜排等效电路阻抗仿真方法、设备和介质,通过对铜排进行等效三维建模,并输入电磁仿真软件中获取连接铜排寄生参数,根据铜排寄生参数绘制连接铜排的等效电路图,根据等效电路图通过电路仿真软件扫频计算获得铜排的特性阻抗曲线,本发明对于需要更改连接铜排形状或材质时,可灵活设置,简便快捷,省去了实验测试的成本和时间周期,可实现快速、低成本获取不同连接铜排的特性阻抗曲线。

附图说明

23.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

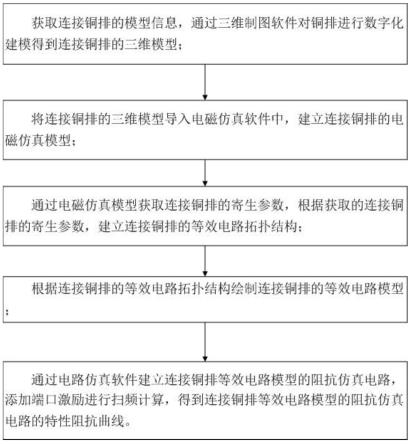

24.图1是本发明实施例中的一种连接铜排等效电路阻抗仿真方法的流程图;

25.图2是本发明实施例中的三维建模及优化效果图;

26.图3是本发明实施例中的连接铜排的等效电路拓扑结构示意图;

27.图4是本发明实施例中的连接铜排等效电路模型图;

28.图5是本发明实施例中的交流铜排正极u相阻抗仿真电路图;

29.图6是本发明实施例中的交流铜排正极u相与v相阻抗仿真电路图;

30.图7是本发明实施例中的交流铜排正极u相阻抗特性曲线图;

31.图8是本发明实施例中的交流铜排正极u相与v相阻抗特性曲线图。

具体实施方式

32.下面将结合附图和实施例,对本发明技术方案做进一步详细描述,显然所描述的实施例是本发明一部分实施例,而不是全部的实施例,本发明的实施方式并不限于此。基于

本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

33.实施例1:

34.本发明提供的连接铜排阻抗仿真方法,可以实现通过计算机模拟仿真的方法获取交流铜排的阻抗参数,避免采用实验测试来获取铜排的特性阻抗参数,减少了实验花费,节约了时间。根据设计需求通过计算机改变三维模型并仿真计算,可实现快速获取不同连接铜排的特性阻抗曲线,适用于三相交流及直流铜排。

35.如图1所示,本发明所述的一种连接铜排等效电路阻抗仿真方法,包括以下步骤:

36.s1、获取连接铜排的模型信息,通过三维制图软件对铜排进行数字化建模,得到连接铜排的三维模型。

37.连接铜排往往使用在大电流传导连接处,如风力发电机、电动汽车上。当有连接铜排实物,则直接将连接铜排实物确定为需求模型,获取连接铜排实物的模型信息,包括铜排的种类(三相或两项)、铜排的尺寸大小、铜排的形状、外部绝缘体形状、外部绝缘体材料等;当连接铜排实物,则需要设定铜排模型信息。

38.所述三维制图软件采用cad软件,根据连接铜排实物的模型信息,通过cad软件绘制铜排导电材料部分几何体和绝缘体部分几何体,采取组装的方式将铜排导电体和绝缘体组合,得到连接铜排的完整的三维模型。

39.s2、将连接铜排的三维模型导入电磁仿真软件中,通过电磁仿真软件建立连接铜排的电磁仿真模型。

40.优选地,电磁仿真软件为q3d软件,q3d软件是workbench中的电磁仿真软件,用于准静态的电磁场仿真,适用于5ghz以下频率,可通过q3d软件完成串扰、延时、反射等仿真模拟,通过q3d计算,可获取电阻r、电感l、g、电容c等电路参数。

41.将连接铜排的三维模型导入q3d软件中,建立连接铜排的电磁仿真q3d模型,具体包括步骤:

42.创建q3d模型,首先建立q3d仿真文件,将连接铜排的三维模型导入电磁仿真q3d软件中。

43.材料设置,根据铜排工作情况设置物理场和边界条件,添加金属材料和绝缘材料,将导电体材料设置为铜,绝缘材料设为pbt;

44.网格划分,按照q3d软件的预设自适应网格设置,调整网格细化程度为7级,并绘制网格。

45.添加激励,在需要提取寄生参数的端口表面设置source端口和sink端口,即激励的源端和末端。

46.求解器设置,在q3d软件中使用add solution setup添加求解器,求解器用于计算连接铜排的寄生参数。

47.add solution setup即为添加求解器按钮,add solution setup用于求解得到连接铜排的寄生参数,即:寄生电容,寄生电阻,寄生电感。

48.s3、通过电磁仿真模型获取连接铜排的寄生参数,根据获取的连接铜排的寄生参数建立连接铜排的等效电路拓扑结构。

49.本实施例中,在q3d电磁仿真模型中创建results,create matrix report,

rectangular plot,根据电路原理通过q3d软件仿真分别获取:u相与v相之间存在的寄生电容、v相与w相之间存在的寄生电容、u相与v相之间存在的寄生电感、v与w相之间存在的寄生电感、u相的寄生电阻、v相的寄生电阻、w相的寄生电阻、u相的寄生电感、v相的寄生电感、w相的寄生电感,故根据获取到的寄生电容、寄生电阻和寄生电感,搭建连接铜排等效电路拓扑结构

50.具体地,如图3所示,连接铜排的等效电路拓扑结构示意图,本实施以三相交流母排为例,根据三相交流铜排的特性,根据获取的连接铜排的寄生参数,建立连接铜排的等效电路拓扑结构,具体包括获取:u相与v相(v-u相)、v与w相(u-w相)存在的寄生电容,获取u相、v相、w相分别存在的寄生电阻和寄生电感,获取u相与v相(u-v相)、v与w相(u-w相)间存在的寄生互感,故根据获取到的连接铜排的寄生电容、寄生电阻及寄生电感值信息,搭建连接铜排等效电路拓扑结构。其中,u相、v相、w相的次序表示三相电动势的相序。

51.在图3中,ru、rv、rw分布表示u、v、w相的寄生电阻;cvu、cuw分布为v-u相、u-w相寄生电容,lu、lv、lw分别为u相、v相、w相寄生电感;mvu、muw分别为u-v相,u-w相寄生互感。

52.s4、根据连接铜排的等效电路拓扑结构绘制连接铜排的等效电路模型。

53.如图4所示,连接铜排等效电路模型图,根据连接铜排的等效电路拓扑结构绘制连接铜排的等效电路模型,具体地包括:

54.设置连接铜排的输入和输出端,图4中,设1、3、5为输入端;2、4、6为输出端。

55.根据u相的寄生电阻、v相的寄生电阻、w相的寄生电阻、u相的寄生电感、v相的寄生电感、w相的寄生电感,分别绘制u相、v相、w相电路;

56.根据u-v相、v-w相存在互感和寄生电容,分别绘制u相与v相之间存在的寄生电容、v相与w相之间存在的寄生电容、u相与v相之间存在的寄生电感、v与w相之间存在的寄生电感。

57.s5、通过电路仿真软件建立连接铜排等效电路模型的阻抗仿真电路,添加端口激励进行扫频计算,得到连接铜排等效电路模型的阻抗仿真电路的特性阻抗曲线。

58.本实施例中,电路仿真软件为saber仿真软件,通过saber仿真软件分别建立u相阻抗仿真电路、v相阻抗仿真电路、w相阻抗仿真电路、u相与v相阻抗仿真电路、v相与w相阻抗仿真电路,对阻抗仿真电路添加端口激励并进行扫频计算,提取阻抗仿真电路端口的阻抗幅频和相频特性仿真结果。

59.如图5所示,为交流铜排正极u相阻抗仿真电路图,图中u相两端接上激励电源,u相存在寄生电容与寄生电感;u-v相、v-w相间存在寄生电容。

60.如图6所示,为交流铜排正极u相与v相阻抗仿真电路,u相v相间添加激励电源,u-v相间存在寄生电容形成一个环路。u相、v相、w相均存在寄生电阻与寄生电感。

61.本实施例中,以u相为例,在saber仿真软件中建立铜排正极u相阻抗仿真电路。首先在saber仿真软件中绘制如图5所示的电路;仿真对象为铜排u相,故将u相输入输出端,即图5中1,2端口添加电源激励,形成回路;v相、w相端口3、4、5、6分别空载;在软件中进行扫频计算。通过上述仿真步骤,可得到铜排u相阻抗特性曲线。

62.如图7所示,为交流铜排u相阻抗特性曲线图,图中频率范围10khz-108mhz,纵坐标为特性阻抗值,采用对数坐标系,曲线表示交流铜排u相从10khz-108mhz频率范围内特性阻抗的变化情况。

63.以u相-v相为例,在saber仿真软件中建立铜排正极u-v相阻抗仿真电路。首先在saber仿真软件中绘制如图6所示电路;仿真对象为铜排u-v相,故将u-v相输入端,即图6中1,3端口添加电源激励,输出端口2、4空载;w相端口5、6分别空载,在软件中进行扫频计算。通过上述仿真步骤,可得到铜排u相阻抗特性曲线。

64.如图8所示,为交流铜排u相与v相阻抗特性曲线图,图中频率范围10khz-108mhz,纵坐标为特性阻抗值,采用对数坐标系,曲线表示交流铜排u-v相从10khz-108mhz频率范围内特性阻抗的变化情况。

65.综上所述,本发明通过对铜排进行等效三维建模,并输入电磁仿真软件中获取连接铜排寄生参数,根据铜排寄生参数绘制连接铜排的等效电路图,根据等效电路图通过电路仿真软件扫频计算获得铜排的特性阻抗曲线,本发明对于需要更改连接铜排形状或材质时,可灵活设置,简便快捷,省去了实验测试的成本和时间周期,可实现快速、低成本获取不同连接铜排的特性阻抗曲线。

66.实施例2:

67.本实施例提供了一种计算机设备,该计算机设备可以是服务器、计算机等,其包括通过系统总线连接的处理器、存储器、输入装置、显示器和网络接口,该处理器用于提供计算和控制能力,该存储器包括非易失性存储介质和内存储器,该非易失性存储介质存储有操作系统、计算机程序和数据库,该内存储器为非易失性存储介质中的操作系统和计算机程序的运行提供环境,处理器执行存储器存储的计算机程序时,实现上述实施例1的一种连接铜排等效电路阻抗仿真方法,如下:

68.获取连接铜排的模型信息,通过三维制图软件对铜排进行数字化建模,得到连接铜排的三维模型;

69.将连接铜排的三维模型导入电磁仿真软件中,建立连接铜排的电磁仿真模型;

70.通过电磁仿真模型获取连接铜排的寄生参数,根据获取的连接铜排的寄生参数,建立连接铜排的等效电路拓扑结构;

71.根据连接铜排的等效电路拓扑结构绘制连接铜排的等效电路模型;

72.通过电路仿真软件建立连接铜排等效电路模型的阻抗仿真电路,添加端口激励进行扫频计算,得到连接铜排等效电路模型的阻抗仿真电路的特性阻抗曲线。

73.实施例3:

74.本实施例提供了一种存储介质,该存储介质为计算机可读存储介质,其存储有计算机程序,所述程序被处理器执行时,处理器执行存储器存储的计算机程序时,实现上述实施例1的一种连接铜排等效电路阻抗仿真方法,如下:

75.获取连接铜排的模型信息,通过三维制图软件对铜排进行数字化建模,得到连接铜排的三维模型;

76.将连接铜排的三维模型导入电磁仿真软件中,建立连接铜排的电磁仿真模型;

77.通过电磁仿真模型获取连接铜排的寄生参数,根据获取的连接铜排的寄生参数,建立连接铜排的等效电路拓扑结构;

78.根据连接铜排的等效电路拓扑结构绘制连接铜排的等效电路模型;

79.通过电路仿真软件建立连接铜排等效电路模型的阻抗仿真电路,添加端口激励进行扫频计算,得到连接铜排等效电路模型的阻抗仿真电路的特性阻抗曲线。

80.上述实施例为本发明较佳的实施方式,但本发明的实施方式并不受上述实施例的限制,其他的任何未背离本发明的精神实质与原理下所作的改变、修饰、替代、组合、简化,均应为等效的置换方式,都包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1