一种针对多协议快充芯片的FPGA数字设计验证平台的制作方法

一种针对多协议快充芯片的fpga数字设计验证平台

技术领域

1.本发明涉及电子电路技术领域,尤其是涉及一种针对多协议快充芯片的fpga数字设计验证平台。

背景技术:

2.随着电子设备性能的不断提升以及人们对于电子设备依赖性的增强,人们对电子设备充电速度的要求也越来越高,近年来快充协议发展迅速,市场上不断涌现出新的快充协议,而且同一快充协议版本也有较快的迭代和调节,至今出现的快充协议类型有:mtk协议、qc协议、pd协议、pps协议、fcp协议、afc协议和vooc协议等,对于电源适配器厂商来说,开发出能够识别和支持多种类型的快充协议的电源适配器是发展趋势,其中,多协议快充芯片的开发又是电源适配器开发中比较重要的一环。

3.在芯片的设计开发过程中,往往需要对其数字设计进行验证,即通过模拟芯片的功能和应用环境,验证芯片的整体功能和性能能否达到预期效果。随着电源适配器支持的快充协议类型越来越多,该多协议快充芯片内部的数据处理方式相应的也会越来越复杂,因此针对多协议快充芯片的数字设计验证时,需要一种验证速度快、验证结果可靠的验证平台,以缩短多协议快充芯片的开发周期,提高芯片的流片成功率。

技术实现要素:

4.为了缩短多协议快充芯片的开发周期以及提高芯片的流片成功率,本技术提供一种针对多协议快充芯片的fpga数字设计验证平台。

5.本技术提供一种针对多协议快充芯片的fpga数字设计验证平台,采用如下的技术方案:一种针对多协议快充芯片的fpga数字设计验证平台,所述验证平台与待充电设备连接,所述验证平台包括:电流放大模块、检测模块、fpga数据处理模块、比较模块、隔离模块、调节模块、变压器t;电流放大模块,用于对所述变压器t副边的输出电流i

out

采样并放大,生成放大输出电流en-i

out

;检测模块,用于接收所述放大输出电流en-i

out

,生成待充电设备的电流信号;还用于检测所述待充电设备端口的电压值,生成待充电设备的电压信号;fpga数据处理模块,用于接收所述待充电设备的电压信号或电流信号,并通过所述检测模块与待充电设备通信,解析出待充电设备的快充协议类型,生成与所述快充协议类型适配的基准电压cv-ref或最大电流cc-ref;比较模块,用于接收所述放大输出电流en-i

out

、基准电压cv-ref和最大电流cc-ref,并获取变压器t副边的输出电压v

out

;并根据所述最大电流cc-ref值、放大输出电流en-i

out

值、基准电压cv-ref值、输出电压v

out

值,生成电流比较结果i

result

或电压比较结果vresult

;隔离模块,用于接收所述电流比较结果i

result

或电压比较结果v

result

,根据所述电流比较结果i

result

或电压比较结果v

result

生成调节信号;调节模块,用于接收所述调节信号,根据所述调节信号调节输出电流i

out

值或输出电压v

out

值,使得调节后的输出电流i

out

或输出电压v

out

与待充电设备的快充协议类型相适配。

6.通过采用上述技术方案,本验证平台以fpga数字处理模块为中心,通过fpga数字处理模块获取检测模块输出的电压信号和电流信号,解析即可得到待充电设备的快充协议类型,再通过调节模块使输出电压和输出电流与待充电设备相匹配,即可实现对待充电设备的快充操作。本验证平台的处理逻辑清晰,且fpga数字处理模块处理速度快,因此验证速度快,可以缩短多协议快充芯片的开发周期;同时fpga数字处理模块支持多次编程的修改,验证结果的可靠性高,提高了芯片的流片成功率。

7.在一个具体的可实施方案中,所述验证平台还包括ad模块,所述电流放大模块对所述调节后的输出电流i

out

采样并放大,生成调节后的放大输出电流en-i

out

;所述ad模块接收所述调节后的放大输出电流en-i

out

,并获取调节后的输出电压v

out

,并将调节后的放大输出电流en-i

out

和调节后的输出电压v

out

转换为数字信号,输出至所述fpga数据处理模块;所述fpga数据处理模块根据所述调节后的放大输出电流en-i

out

、调节后的输出电压v

out

解析得到当前输出电压值和电流值,并通过检测模块将所述当前输出电压值和电流值反馈至待充电设备。

8.通过采用上述技术方案,将当前输出电压值和电流值反馈至待充电设备,便于待充电设备根据当前输出电压值和电流值,相应做出调整,避免当前输出电压值和电流值与待充电设备的需求偏差过大,影响待充电设备电池的使用寿命。

9.在一个具体的可实施方案中,所述检测模块包括d+/d-检测电路、cc线检测电路、输出电流检测电路和切换电路;所述d+/d-检测电路用于检测待充电设备d+端口和d-端口的电压值;所述cc线检测电路用于检测待充电设备cc1端口或cc2端口的电压值;所述输出电流检测电路用于检测所述输出电流i

out

值;所述切换电路用于输出不同的电压值至待充电设备的d+端口和d-端口。

10.通过采用上述技术方案,通过对待充电设备多个端口的电压值进行检测,以及对输出电流i

out

的检测,再利用切换电路输出电压值的变化,使fpga数据处理模块与待充电设备进行多次通信,提高fpga数据处理模块对待充电设备的快充协议类型判断的准确性。

11.在一个具体的可实施方案中,所述cc线检测电路包括第一比较器和第二比较器,所述第一比较器和第二比较器的同相输入端均与待充电设备的cc1端口或cc2端口连接;所述第一比较器的同相输入端的电压值由第一使能开关组控制,所述第一使能开关组包括多路并联的使能开关,每一路中的使能开关与一电流源串联;所述第一比较器的反相输入端的电压值由第二使能开关组控制,所述第二使能开关组由多路使能开关组成,每一路中的使能开关配置对应的电压;所述第二比较器的同相输入端的电压值由第三使能开关组控制,所述第三使能开关组包括多路并联的使能开关,每一路中的使能开关与一电流源串联;所述第二比较器的反相输入端的电压值由第四使能开关组控制,所述第四使能开关组由多路使能开关组成,

每一路中的使能开关配置对应的电压。

12.通过采用上述技术方案,通过闭合不同的使能开关,第一比较器和第二比较器的输出电平的高低会发生变化,可以实现fpga数据处理模块对cc1端口或cc2端口电压的多次检测,提高对cc1端口或cc2端口电压判断的准确性。

13.在一个具体的可实施方案中,所述切换电路包括多个使能开关,fpga数据处理模块通过控制所述切换电路中各使能开关的闭合,使所述切换电路输出不同的电压值至待充电设备的d+端口和d-端口。

14.通过采用上述技术方案,fpga数据处理模块通过控制各使能开关的闭合,进而控制切换电路输出的电压值,即可实现fpga数据处理模块与待充电设备的通信,通信效率高。

15.在一个具体的可实施方案中,所述比较模块包括da芯片、第三比较器、第四比较器;所述da芯片将所述基准电压cv-ref和所述最大电流cc-ref转换为模拟信号,所述第三比较器比较基准电压cv-ref值与输出电压v

out

值,生成电压比较结果v

result

,所述第四比较器比较最大电流cc-ref值与放大输出电流en-i

out

值,生成电流比较结果i

result

。

16.通过采用上述技术方案,比较模块中的两个比较器,一个用来比较基准电压cv-ref值与输出电压v

out

值,一个用来比较最大电流cc-ref值与放大输出电流en-i

out

值,使本比较模块电路的比较逻辑清晰,不易紊乱。

17.在一个具体的可实施方案中,所述隔离模块为光耦、磁耦或容耦,所述隔离模块通过串联一电阻后与所述变压器t副边的输出端连接。

18.通过采用上述技术方案,通过隔离模块实现变压器t的原边电路和副边电路的电气隔离,同时又能进行信号的传递,通过串联的电阻可以防止电流过大损坏隔离模块的芯片,提高了系统的安全性。

19.在一个具体的可实施方案中,所述fpga数据处理模块与所述比较模块、所述ad模块之间的通信均采用i2c通信方式。

20.通过采用上述技术方案,i2c通信方式只需一根数据线和一根时钟线即可实现,优化了多协议快充芯片的空间,且i2c通信方式功耗低,抗干扰能力强,提高了验证平台的性能。

21.综上所述,本技术的技术方案至少包括以下有益技术效果:1、采用fpga数字设计验证平台可以检测并解析出待充电设备的快充协议类型,控制输出电压或输出电流与待充电设备相匹配,实现对待充电设备的快充操作,本验证平台的验证速度快,缩短了多协议快充芯片的开发周期,同时验证结果可靠,提高了芯片流片成功率,使芯片的流片成功率达到90%以上。

附图说明

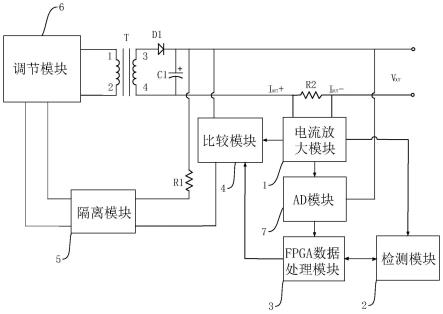

22.图1是本技术实施例中一种针对多协议快充芯片的fpga数字设计验证平台的整体电路图。

23.图2是本技术实施例中检测模块2的电路图。

24.图3是本技术实施例中fpga数字处理模块3的电路图。

25.图4是本技术实施例中比较模块4的电路图。

26.图5是本技术实施例中隔离模块5的电路图。

27.图6是本技术实施例中ad模块7的电路图。

28.附图标记说明:1、电流放大模块;11、放大器;2、检测模块;21、d+/d-检测电路;211、第五比较器;212、第六比较器;213、第七比较器;214、第八比较器;215、第九比较器;216、第十比较器;217、第十一比较器;218、第十二比较器;22、cc线检测电路;221、第一比较器;222、第二比较器;23、输出电流检测电路;231、第十三比较器;232、第十四比较器;233、第十五比较器;24、切换电路;3、fpga数字处理模块;4、比较模块;41、da芯片;42、第三比较器;43、第四比较器;5、隔离模块;51、光耦;6、调节模块;7、ad模块;71、ad芯片。

具体实施方式

29.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施方式作进一步地详细说明。

30.本技术公开一种针对多协议快充芯片的fpga数字设计验证平台,如图1所示,变压器t的端口1和端口2连接的是原边电路,变压器t的端口3和端口4连接的是副边电路,变压器t的副边电路与待充电设备连接,通过变压器t副边的输出端为待充电设备供电。

31.变压器t的端口1和端口2与调节模块6连接,由于变压器t原边输出电压与副边输出电压大小的比值为变压器t原边线圈和副边线圈的匝数比,利用变压器t的这一特性,调节模块6改变变压器t原边输出电压值,即可实现变压器t副边输出电压v

out

和副边输出电流i

out

的调节。

32.变压器t的端口3串联二极管d1,二极管d1的正极与端口3连接,二极管d1的负极连接至待充电设备,二极管d1的负极还与电容c1的正极连接,电容c1的负极与变压器t的端口4连接。二极管d1用于对输出电压v

out

进行整流,将交流电整成直流电,再通过电容c1将整流后的直流电进行滤波,使输出至待充电设备的电压更加稳定。

33.本技术中,fpga数字设计验证平台的运行过程如下:s1:电流放大模块1包括放大器11,放大器11的两个输入端连接电阻r2的两端,将变压器t副边的输出电流i

out

采样并按照预设倍数放大,生成放大输出电流en-i

out

。

34.可选的,上述预设倍数为50倍。

35.s2:检测模块2接收电流放大模块1输出的放大输出电流en-i

out

,生成待充电设备的电流信号;检测模块2还与待充电设备多个端口连接,检测多个端口的电压值,生成待充电设备的电压信号。

36.其中,检测模块2包括d+/d-检测电路21、cc线检测电路22、输出电流检测电路23和切换电路24;d+/d-检测电路21用于检测待充电设备d+端口和d-端口的电压值;cc线检测电路22用于检测待充电设备cc1端口或cc2端口的电压值;输出电流检测电路23用于检测输出电流i

out

值;切换电路24用于输出不同的电压值至待充电设备的d+端口和d-端口。

37.如图2所示,d+/d-检测电路21包括第五比较器211、第六比较器212、第七比较器213和第八比较器214、第九比较器215、第十比较器216、第十一比较器217、第十二比较器218;第五比较器211~第八比较器214的同相输入端与待充电设备的d+端口连接,反相输入端配置不同的电压值,用于对待充电设备的d+端口的电压值进行比较,并输出d+端口的电压比较结果至fpga数字处理模块3;第九比较器215~第十二比较器218的同相输入端与待充

samsng、使能开关k-bc12、使能开关k-hw、使能开关k-dat-lkg、电阻r5、电阻r6、电阻r7、电阻r8。闭合切换电路24中不同的使能开关,切换电路24输出不同的电压值至待充电设备的d+端口和d-端口。切换电路24的具体连接如下:电阻r5的一端配置电压值,电阻r5的另一端通过串联使能开关k-apple输出电压值至待充电设备的d+端口;电阻r6的一端配置另外一个电压值,电阻r6通过串联使能开关k-samsng输出电压值至待充电设备的d-端口,使能开关k-apple与使能开关k-samsng之间连接有使能开关k-bc12,使能开关k-samsng的一端通过串联电阻r7、串联使能开关k-hw接地,使能开关k-apple的一端通过串联电阻r8、串联使能开关k-dat-lkg接地。

48.可选的,上述电阻r5的一端配置的电压值为2.7v,上述电阻r6的一端配置的电压值为1.2v。

49.s3:fpga数据处理模块3,接收检测模块2输出的待充电设备的电压信号或电流信号,并通过检测模块2与待充电设备通信,解析出待充电设备的快充协议类型,生成与所述快充协议类型适配的基准电压cv-ref或最大电流cc-ref。

50.其中,电压信号即d+/d-检测电路21输出的d+端口的电压比较结果、d-端口的电压比较结果,以及cc线检测电路22输出的cc1端口或cc2端口的电压比较结果;电流信号即输出电流检测电路23输出的输出电流比较结果。

51.fpga数据处理模块3根据待充电设备的电压信号,闭合切换电路24中相应的使能开关,使切换电路24输出不同的电压值至待充电设备的d+端口和d-端口,与待充电设备进行通信;待充电设备接收到切换电路24输出的电压值,从而改变d+端口、d-端口或cc1端口或cc2端口的电压值;检测模块2再次检测,并再次生成电压信号和电流信号输出至fpga数据处理模块3,fpga数据处理模块3即可解析出待充电设备的快充协议类型,生成与所述快充协议类型适配的基准电压cv-ref或最大电流cc-ref。

52.或者,fpga数据处理模块3连续接收多次待充电设备的电流信号,即连续接收多次电流检测电路23输出的电流信号,便可解析出待充电设备的快充协议类型,生成与所述快充协议类型适配的基准电压cv-ref或最大电流cc-ref。

53.特别的,fpga数据处理模块3不同时输出基准电压cv-ref和最大电流cc-ref。

54.s4:比较模块4,用于接收电流放大模块1输出的放大输出电流en-i

out

、并接收fpga数据处理模块3输出的基准电压cv-ref和最大电流cc-ref,并获取变压器t副边的输出电压v

out

;比较模块4根据最大电流cc-ref值、放大输出电流en-i

out

值、基准电压cv-ref值、输出电压v

out

值,生成电流比较结果i

result

或电压比较结果v

result

。

55.在本技术的一个实施例中,如图4所示,比较模块4包括da芯片41、第三比较器42、第四比较器43、电阻r3、电阻r4、二极管d2、二极管d3。da芯片41与fpga数据处理模块3的输出端连接,将基准电压cv-ref和最大电流cc-ref转换为模拟信号。第三比较器42的同相输入端接收da芯片41输出的基准电压cv-ref,第三比较器42的反相输入端通过串联电阻r3与变压器t副边输出端连接,电阻r3的另一端通过串联电阻r4接地,第三比较器42的反相输入端获取输出电压v

out

,第三比较器42的输出端与二极管d2的负极连接,第三比较器42通过比较基准电压cv-ref值与输出电压v

out

值,生成电压比较结果v

result

,通过二极管d2输出至隔离模块5。第四比较器43的同相输入端接收da芯片41输出的最大电流cc-ref,第四比较器43的反相输入端与放大模块1的输出端连接,获取放大输出电流en-i

out

,第四比较器43的输出

端与二极管d3的负极连接,第四比较器43通过比较最大电流cc-ref值与放大输出电流en-i

out

值,生成电流比较结果i

result

,通过串联二极管d3输出至隔离模块5。

56.其中,当输出电压v

out

大于基准电压cv-ref时,第三比较器42输出低电平;当输出电压v

out

小于基准电压cv-ref时,第三比较器42输出高电平。当放大输出电流en-i

out

大于最大电流cc-ref时,第四比较器43输出低电平,当放大输出电流en-i

out

小于最大电流cc-ref时,第四比较器43输出高电平。

57.特别的,由于fpga数据处理模块3不同时输出基准电压cv-ref和最大电流cc-ref,第三比较器42和第四比较器43也不会同时输出比较结果。

58.特别的,da芯片与fpga数据处理模块3之间通信的方式是i2c通信。

59.s5:隔离模块5,用于接收比较模块4输出的电流比较结果i

result

或电压比较结果v

result

,根据电流比较结果i

result

或电压比较结果v

result

生成调节信号。

60.隔离模块5为光耦、磁耦或容耦。

61.在本技术的一个实施例中,隔离模块5为光耦51,如图5所示,光耦51包括发光二极管d4和光敏三极管q1,其中,光敏三极管q1的两端与调节模块6连接,发光二极管d4的正极通过串联电阻r1与二极管d1的负极连接,用于接收变压器t副边电路输出端的输出电压v

out

,发光二极管d4的负极与二极管d2的正极连接,发光二极管d4的负极与二极管d3的正极连接,当第三比较器42或第四比较器43输出高电平时,发光二极管d4不导通,不发光,光敏三极管q1无电流;当第三比较器42或第四比较器43输出低电平时,发光二极管d4导通并发光,光敏三极管q1通过感知发光二极管d4发出的光改变自身电流。

62.s6:调节模块6,用于接收隔离模块5输出的调节信号,根据调节信号调节输出电流i

out

值或输出电压v

out

值,使得调节后的输出电流i

out

或输出电压v

out

与待充电设备的快充协议类型相适配。具体为:调节模块6根据光敏三极管q1的电流变化,可以判断出输出电压v

out

值与基准电压cv-ref值的大小,或者放大输出电流en-i

out

值与最大电流cc-ref值的大小,调节模块6通过控制变压器t原边输出电压值,即可实现变压器t副边输出电压v

out

和副边输出电流i

out

的调节。

63.s7:电流放大模块1对调节后的输出电流i

out

采样并按照预设倍数放大,生成调节后的放大输出电流en-i

out

;ad模块7与电流放大模块1的输出端连接,接收调节后的放大输出电流en-i

out

,ad模块7还与变压器t副边输出端连接,获取调节后的输出电压v

out

;ad模块7将调节后的放大输出电流en-i

out

和调节后的输出电压v

out

转换为数字信号,输出至fpga数据处理模块3;fpga数据处理模块3根据调节后的放大输出电流en-i

out

、调节后的输出电压v

out

,解析得到当前输出电压值和电流值,并通过检测模块2与待充电设备连接的d+端口、d-端口或者cc1端口/cc2端口,将当前输出电压值和电流值反馈至待充电设备,便于待充电设备相应做出调整,避免当前输出电压值和电流值和待充电设备的需求偏差过大,影响待充电设备电池的使用寿命。

64.其中,ad模块7包括ad芯片71。

65.特别的,ad模块7与fpga数据处理模块3之间通信的方式是i2c通信。

66.以上均为本技术的较佳实施例,并非依此限制本技术的保护范围,故:凡依本技术的结构、形状、原理所做的等效变化,均应涵盖于本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1