一种基于FPGA的射频脉冲生成方法及装置与流程

一种基于fpga的射频脉冲生成方法及装置

技术领域

1.本发明涉及量子测控技术领域,特别涉及一种基于fpga的射频脉冲生成方法及装置。

背景技术:

2.量子计算机的工作原理为:通过量子测控系统对量子芯片上制备的量子比特qubit进行操控,实现某种量子算法,并通过量子测控系统读取量子比特的测量输出而获得计算的结果。其中,量子测控系统主要由低噪声精密电压单元、脉冲发生单元、射频脉冲单元、反射测量单元、高精密微波源等多个功能单元来构成测控通道,每个测控通道用于对应一个量子比特的操控与测量。而为了实现更多量子比特的量子计算,就必须要求量子测控系统具有足够多的测控通道,来支持更多量子比特的操控与测量。

3.其中,射频脉冲单元产生一路射频脉冲信号的原理如图1所示,将波形数据缓存至ram,然后会根据触发信号,将ram中缓存的波形数据输出至数模转换器(dac),dac根据波形数据实时产生波形信号,最后由射频前端单元(rf)根据dac输出的波形信号生成相应地射频脉冲信号。那么,若要支持更多量子比特的操控,则需要大量的ram资源。

4.fpga凭借其具有丰富的硬件资源(包括ram硬件资源)以及可重复编的特性,射频脉冲单元通常采用fpga来提供ram硬件资源以及实现多路波形数据的同步输出,但是,fpga在多路大容量ram并发输出波形数据时,会出现逻辑时序不收敛,使多路波形数据输出的同步性无法满足测控通道间的同步要求;虽然可以通过降低fpga输出波形数据的路数,来缓解逻辑时序不收敛的问题,但必然使用更多的fpga才能实现同等路数的波形输出,将增加了硬件成本。

技术实现要素:

5.鉴于以上所述现有技术的不足,本发明的目的在于:提供一种基于fpga的射频脉冲生成方法,对fpga内的ram资源和高传数据传输接口的布局优化,解决fpga在多路大容量ram并发输出波形数据时,出现逻辑时序不收敛的问题。

6.为实现上述发明目的,本发明提供以下技术方案:

7.一种基于fpga的射频脉冲生成方法,其包括以下步骤:

8.s1:根据fpga的ram资源分布情况,确定所述fpga中用于传输波形数据的高速数据传输接口的位置,使每个用于传输波形数据的高速数据传输接口以就近原则获取预设容量的ram资源;

9.s2:以时序优先为布线策略,对所述fpga中用于传输波形数据的高速数据传输接口及其对应的ram资源进行布线优化,并使所述fpga的逻辑时序收敛;

10.s3:将每路射频脉冲信号的波形数据分别缓存至用于传输该路射频脉冲信号的波形数据的高速数据传输接口对应的ram资源;

11.s4:根据触发信号的触发控制,每个用于传输波形数据的高速数据传输接口读取

其对应的ram资源内缓存的波形数据,并输出至其对应的数模转换器;每个所述数模转换器将其基于输入的波形数据而生成相应的波形信号输出至其对应的射频前端单元,以生成相应的射频脉冲信号。

12.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成方法的步骤s2中,判断所述fpga的逻辑时序是否收敛的方式为:

13.获取时序参考分析采用的时钟clk0输入至所述fpga的外部走线延时,时钟clk0到达所述fpga内部时序路径上第一个reg的d端的第一内部走线延时,以及,时钟clk0在所述fpga内部时序路径上任意两个相邻的reg之间的第二内部走线延时;

14.若所述外部走线延时与所述第一内部走线延时的总延时小于时钟clk0的时钟周期,且所述第二内部走线延时小于时钟clk0的时钟周期,则所述fpga的逻辑时序收敛,否则,所述fpga的逻辑时序不收敛。

15.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成方法中,两个相邻reg之间的所述第二内部走线延时大于时钟clk0的时钟周期,则在所述两个相邻reg之间增加一级reg。

16.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成方法的步骤s2中,当所述fpga的逻辑时序收敛时,采用lockregion方式锁定所述fpga中各个用于传输波形数据的高速数据传输接口及其对应的所述ram资源的当前布线方式。

17.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成方法中,所述高速数据传输接口为jesd204b协议的高速串行接口。

18.本发明的另一方面,还提供一种基于fpga的射频脉冲生成装置,其包括:

19.fpga、n个数模转换器以及n个射频前端单元;

20.其中,所述fpga被配置为:根据所述fpga的ram资源分布情况,确定所述fpga中n个用于传输波形数据的高速数据传输接口的位置,使每个用于传输波形数据的高速数据传输接口以就近原则获取预设容量的ram资源;以时序优先为布线策略,对所述fpga中n个用于传输波形数据的高速数据传输接口及其对应的所述ram资源进行布线优化,使逻辑时序收敛;以及,根据触发信号的触发控制,每个用于传输波形数据的高速数据传输接口读取其对应的ram资源内缓存的波形数据,并输出至其对应的数模转换器;

21.每个所述数模转换器将其基于输入的波形数据而生成相应的波形信号输出至其对应的射频前端单元,以生成相应的射频脉冲信号。

22.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成装置中,所述fpga被配置为:外部走线延时与第一内部走线延时的总延时小于时钟clk0的时钟周期且第二内部走线延时小于时钟clk0的时钟周期,则逻辑时序收敛,否则,逻辑时序不收敛;

23.其中,所述外部走线延时为时序参考分析采用的时钟clk0输入至所述fpga的延时,所述第一内部走线延时为时钟clk0到达所述fpga内部时序路径上第一个reg的d端的延时,以及,所述第二内部走线延时为时钟clk0在所述fpga内部时序路径上任意两个相邻的reg之间的延时。

24.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成装置中,所述fpga被配置为:当有两个相邻reg之间的所述第二内部走线延时大于时钟clk0的时钟周期时,则在所述两个相邻reg之间增加一级reg。

25.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成装置中,所述fpga被配置为:当逻辑时序收敛时,采用lockregion方式锁定所述fpga中各个用于传输波形数据的高速数据传输接口及其对应的所述ram资源的当前布线方式。

26.根据一种具体的实施方式,本发明基于fpga的射频脉冲生成装置中,所述高速数据传输接口为jesd204b协议的高速串行接口。

27.与现有技术相比,本发明的有益效果:

28.本发明基于fpga的射频脉冲生成方法中,根据需要生成的射频脉冲信号的路数以及fpga的ram资源分布情况,确定fpga中各个用于传输波形数据的高速数据传输接口的数量与位置,并使每个用于传输波形数据的高速数据传输接口以就近原则获取预设容量的ram资源;然后,以时序优先为布线策略,对fpga中各个用于传输波形数据的高速数据传输接口及其对应的所述ram资源进行布线优化,使fpga的逻辑时序收敛;最后,将波形数据缓存至ram资源中,并通过高速数据传输接口输出波形数据,并通过数模转换器和射频前端单元生成射频脉冲信号;因此,本发明能够解决fpga在多路大容量ram并发输出波形数据时,出现逻辑时序不收敛的问题。

附图说明:

29.图1为射频脉冲单元产生一路射频脉冲信号的原理示意图;

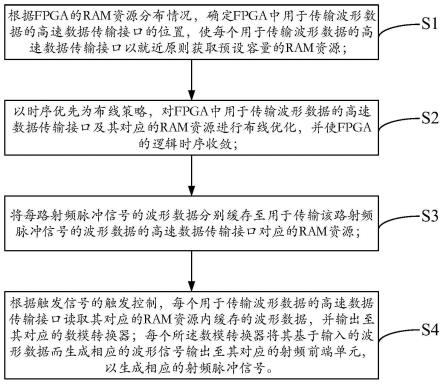

30.图2为本发明实施例中基于fpga的射频脉冲生成方法的流程示意图;

31.图3为fpga在一般应用场景下高速数据传输接口的位置分布图;

32.图4为本发明实施例中fpga内高速数据传输接口的位置分布图;

33.图5为本发明实施例中fpga的时序路径分析图;

34.图6为本发明实施例中基于fpga的射频脉冲生成装置的结构示意图。

具体实施方式

35.下面结合附图及具体实施例对本发明作进一步的详细描述。但不应将此理解为本发明上述主题的范围仅限于以下的实施例,凡基于本发明内容所实现的技术均属于本发明的范围。

36.如图2所示,本发明提供的一种基于fpga的射频脉冲生成方法,其包括以下步骤:

37.s1:根据fpga的ram资源分布情况,确定所述fpga中用于传输波形数据的高速数据传输接口的位置,使每个用于传输波形数据的高速数据传输接口以就近原则获取预设容量的ram资源;

38.s2:以时序优先为布线策略,对所述fpga中用于传输波形数据的高速数据传输接口及其对应的ram资源进行布线优化,并使所述fpga的逻辑时序收敛;

39.s3:将每路射频脉冲信号的波形数据分别缓存至用于传输该路射频脉冲信号的波形数据的高速数据传输接口对应的ram资源;

40.s4:根据触发信号的触发控制,每个用于传输波形数据的高速数据传输接口读取其对应的ram资源内缓存的波形数据,并输出至其对应的数模转换器;每个所述数模转换器将其基于输入的波形数据而生成相应的波形信号输出至其对应的射频前端单元,以生成相应的射频脉冲信号。

41.具体的,fpga内部集成了方便和高速dac匹配的高速数据传输接口,通常称呼为高速收发器或者gt,支持pcie、jesd204b、sata等多种协议,不同的fpga型号有不同数量的高速收发器;因此,fpga的高速收发器资源需要大于高速dac数量,而且,由于高速数据传输接口的作用是读取fpga的ram资源内缓存的波形数据,而波形数据对ram资源的容量要求高,因此,需要对高速数据传输接口的位置选择进行优化,使其能够以就近原则获取预设容量的ram资源。以选用fpga的型号为xc7vx690t为例,包含20个高速收发bank(也称quad),需要产生8路射频脉冲信号(即8个高速dac),如图3所示,如果选择的8个高速数据传输接口集中在一个区域,后续为每个高速数据传输接口开辟fpga内部ram资源时,可能导致某些高速数据传输接口访问ram资源路径较远,最后时序分析时走线延时较大导致时序不收敛。由于fpga上的ram资源基本上是均匀分布的,故将高速数据传输接口均匀地分布在fpga的周围,即图4所示,避免高速数据传输接口以较长的路径访问ram资源,方便后期逻辑代码的实现。

42.如图5所示,在步骤s2中,判断所述fpga的逻辑时序是否收敛的方式为:

43.获取时序参考分析采用的时钟clk0输入至fpga的外部走线延时input delay,时钟clk0到达fpga内部时序路径上rega的d端的第一内部走线延时internal delay 1,以及,时钟clk0在fpga内部时序路径上任意两个相邻的reg之间的第二内部走线延时data path delay;

44.若外部走线延时input delay与第一内部走线延时internal delay 1的总延时小于时钟clk0的时钟周期,且第二内部走线延时data path delay小于时钟clk0的时钟周期,则fpga的逻辑时序收敛,否则,所述fpga的逻辑时序不收敛。

45.在实施时,若时钟clk0在fpga内部时序路径上两个相邻reg之间的所述第二内部走线延时大于时钟clk0的时钟周期,则在所述两个相邻reg之间增加一级reg。

46.由于多路射频脉冲信号的波形数据使用的ram资源为fpga片内的资源,会占用大量的逻辑资源和布线资源,在fpga内部设计实现布局布线阶段,如果外部走线延时input delay与第一内部走线延时internal delay 1的总延时大于时钟clk0的时钟周期或第二内部走线延时data path delay大于时钟clk0的时钟周期,可能会导致部分时钟和数据的时序无法满足建立保持时间,导致时序不收敛数据出错。同时,由于高速数据传输接口为jesd204b协议的高速串行接口,fpga内部自带时序约束和调整internal delay 2。因此,本发明能够解决fpga在多路大容量ram并发输出波形数据时,出现逻辑时序不收敛的问题。

47.进一步地,当所述fpga的逻辑时序收敛时,采用lockregion方式锁定所述fpga中各个用于传输波形数据的高速数据传输接口及其对应的所述ram资源的当前布线方式。如此,方便后续如果需要修改程序其他功能时,这一部分就不需要再重新综合实现。

48.本发明的另一方面,还提供如图6所示的基于fpga的射频脉冲生成装置,其包括:

49.fpga、8个数模转换器dac1~dac8以及8个射频前端单元rf1~rf8;

50.其中,所述fpga被配置为:根据所述fpga的ram资源分布情况,确定所述fpga中用于传输波形数据的高速数据传输接口gt1~gt8的位置,使每个用于传输波形数据的高速数据传输接口以就近原则获取预设容量的ram资源;以时序优先为布线策略,对所述fpga中8个用于传输波形数据的高速数据传输接口gt1~gt8及其对应的所述ram资源进行布线优化,使逻辑时序收敛;以及,根据触发信号的触发控制,每个用于传输波形数据的高速数据传输接口读取其对应的ram资源内缓存的波形数据,并输出至其对应的数模转换器;

51.每个所述数模转换器将其基于输入的波形数据而生成相应的波形信号输出至其对应的射频前端单元,以生成相应的射频脉冲信号。

52.本发明基于fpga的射频脉冲生成装置中,所述fpga被配置为:外部走线延时与第一内部走线延时的总延时小于时钟clk0的时钟周期且第二内部走线延时小于时钟clk0的时钟周期,则逻辑时序收敛,否则,逻辑时序不收敛;

53.其中,所述外部走线延时为时序参考分析采用的时钟clk0输入至所述fpga的延时,所述第一内部走线延时为时钟clk0到达所述fpga内部时序路径上第一个reg的d端的延时,以及,所述第二内部走线延时为时钟clk0在所述fpga内部时序路径上任意两个相邻的reg之间的延时。

54.在实施时,所述fpga被配置为:当有两个相邻reg之间的所述第二内部走线延时大于时钟clk0的时钟周期时,则在所述两个相邻reg之间增加一级reg。

55.本发明基于fpga的射频脉冲生成装置中,所述fpga被配置为:当逻辑时序收敛时,采用lockregion方式锁定所述fpga中各个用于传输波形数据的高速数据传输接口及其对应的所述ram资源的当前布线方式。

56.本发明基于fpga的射频脉冲生成装置中,所述高速数据传输接口为jesd204b协议的高速串行接口。

57.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1