一种有源相控阵面校正数据的分布式快速分发方法与流程

1.本技术涉及相控阵面波束控制技术领域,特别涉及一种有源相控阵面校正数据的分布式快速分发方法。

背景技术:

2.有源相控阵面具有快速改变波束指向和波束形状的能力,在军事和通信等领域得到了广泛应用。相控阵面要求每个阵元间的幅度和相位稳定、一致和可控,否则会对波束形成产生不利的影响。

3.但在实际系统中,由于元器件性能的差异、设备加工装配精度的差异以及设备工作频率和环境的差异,导致相控阵面各阵元原始幅度和相位的一致性难以保证,因此相控阵面必须进行幅相校正,并用校正数据对波束控制码进行修正,用修正后的波束控制码进行布相。大型宽带相控阵面工作频带宽、工作模式多,幅相校正数据量大,需要大容量高性能的幅相校正单元,实现校正数据的快速分发。

4.但是现有技术中,大容量的幅相校正单元,尚未实现校正数据的快速分发。

技术实现要素:

5.本技术提供了一种有源相控阵面校正数据的分布式快速分发方法,可用于解决大容量的幅相校正单元需实现校正数据快速分发的技术问题。

6.本技术提供一种有源相控阵面校正数据的分布式快速分发方法,所述方法包括:

7.初始装载操作和查询分发操作;

8.其中,初始装载操作在相控阵面加电后执行,将存储于初始数据空间的校正数据装载到配置数据空间,进行分布式存储;

9.查询分发操作在工作时实时执行,以相控阵面的工作状态和阵元的原始波束控制码为地址读取配置数据空间的校正数据,获取修正后的波束控制码。

10.相控阵面波束控制系统包括波束控制主机和多个子板;

11.所述初始数据空间布置在波束控制主机的大容量掉电非易失nandflash存储阵列中,所述配置数据空间布置在子板的高速随机存储器ddr存储阵列中;

12.所述波束控制主机和子板以fpga为控制核心;波束控制主机配置多个光发送模块,每个子板配置一个光接收模块,波束控制主机和各个子板间形成多路一对一的光链路,波束控制主机和各个子板间通过对应光链路传输校正数据,校正数据以数据流形式传输。

13.可选的,初始数据空间的校正数据结构如下:以每个子板的校正数据为单元,依次存储到nand flash存储阵列的各个plane中,若子板数超过plane数,超出的部分再次从plane起始排列,初始装载操作过程中对nand flash的读取操作在各plane间流水操作。

14.可选的,以子板1为例,所述初始装载操作包括:

15.步骤11,波束控制主机接收到初始装载操作指令,进入初始装载操作状态;

16.步骤12,波束控制主机发送读取子板1的校正数据包1的请求;

17.步骤13,波束控制主机等待子板1的数据输出;

18.步骤14,波束控制主机读取子板1的校正数据后,在校正数据前加入报文标识、报文长度、数据类型等信息,并通过光链路传输给子板1;

19.步骤15,子板1接收到校正数据后,将校正数据按照数据类型信息更新到ddr存储阵列中。

20.可选的,其他子板的初试装载操作从步骤12开始执行,至步骤15结束,并且当子板1执行步骤13时,子板2同时执行步骤12,当子板2执行步骤13时,子板3同步执行步骤12,依次类推。

21.可选的,配置存储空间的校正数据结构如下:

22.ddr存储阵列包括n片ddr,每片ddr包含m个bank;

23.存储顺序将阵元按照编号顺序依次存储入ddr1的bank1、ddr2的bank1,

……

,ddrn的bank1,ddr1的bank2、ddr2的bank2,

……

,直至历遍所有bank后,再从ddr1的bank1开始存储。

24.可选的,以阵元1为例,所述查询分发操作包括:

25.步骤21,波束控制子板接收到查询分发操作指令,进入查询分发操作状态;

26.步骤22,查询阵元1的校正数据,根据当前阵面工作频率查询阵元号、阵元1的初始幅度和初始相位,确定出阵元1的查询地址,将查询地址和读请求发送给ddr存储器;

27.步骤23,等待阵元1的数据输出;

28.步骤24,更新阵元1的校正数据。

29.可选的,其他阵元的初试装载操作相同,并且当阵元1执行步骤23时,阵元2同时执行步骤22。

30.由于对同一ddr存储器,连续两次操作对象为不同bank,不存在预冲操作,所有操作连续执行。

31.本发明可以实现有源相控阵面校正数据的分布式快速分发,在初始装载操作阶段,快速将大量校正数据加载到配置数据空间,节省有源相控阵面准备时间,使阵面尽快具备作战能力,在查询分发操作阶段,快速获取各个阵元的校正数据,即校正后的波束控制码,实现有源相控阵面波束指向快速切换。

附图说明

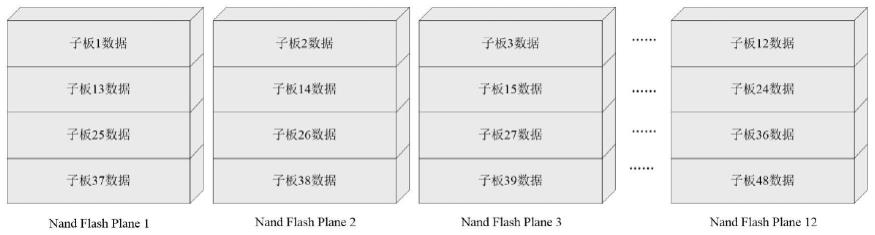

32.图1是本技术实施例提供的初始数据空间的校正数据结构;

33.图2是本技术实施例提供的校正数据的分布式快速分发方法的初始装载操作流水图;

34.图3是本技术实施例提供的配置数据空间的校正数据结构;

35.图4是本技术实施例提供的校正数据的分布式快速分发方法的查询分发操作流水图。

具体实施方式

36.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施方式作进一步地详细描述。

37.下面首先结合图对本技术实施例进行介绍。

38.本技术提供一种有源相控阵面校正数据的分布式快速分发方法,方法包括:

39.初始装载操作和查询分发操作;

40.其中,初始装载操作在相控阵面加电后执行,将存储于初始数据空间的校正数据装载到配置数据空间,进行分布式存储;

41.查询分发操作在工作时实时执行,以相控阵面的工作状态和阵元的原始波束控制码为地址读取配置数据空间的校正数据,获取修正后的波束控制码。

42.相控阵面波束控制系统包括波束控制主机和多个子板;

43.初始数据空间布置在波束控制主机的大容量掉电非易失nand flash存储阵列中,配置数据空间布置在子板的高速随机存储器ddr存储阵列中;

44.波束控制主机和子板以fpga为控制核心,充分利用fpga的并行操作特性提高数据分发效率;波束控制主机配置多个光发送模块,每个子板配置一个光接收模块,波束控制主机和各个子板间形成多路一对一的光链路,波束控制主机和各个子板间通过对应光链路传输校正数据,校正数据以数据流形式传输。

45.为减少初始装载操作时间,初始数据空间的校正数据结构如下:以每个子板的校正数据为单元,依次存储到nand flash存储阵列的各个plane中,若子板数超过plane数,超出的部分再次从plane起始排列,初始装载操作过程中对nand flash的读取操作在各plane间流水操作;可减少读取nand flash的等待时间。

46.具体的,比如子板1的校正数据存储在plane1中,子板2的校正数据存储在plane2中,

……

,子板12的校正数据存储在plane12中;由于子板数超过总plane数,子板13的校正数据存储在plane1中,子板14的校正数据存储在plane2中,其他子板的校正数据存储位置依次类推。

47.以子板1为例,初始装载操作包括:

48.步骤11,波束控制主机接收到初始装载操作指令,进入初始装载操作状态;

49.步骤12,波束控制主机发送读取子板1的校正数据包1的请求;

50.步骤13,波束控制主机等待子板1的数据输出;

51.步骤14,波束控制主机读取子板1的校正数据后,在校正数据前加入报文标识、报文长度、数据类型等信息,并通过光链路传输给子板1;

52.步骤15,子板1接收到校正数据后,将校正数据按照数据类型信息更新到ddr存储阵列中。

53.其他子板的初试装载操作从步骤12开始执行,至步骤15结束,并且当子板1执行步骤13时,子板2同时执行步骤12,当子板2执行步骤13时,子板3同步执行步骤12,依次类推。

54.波束控制主机继续请求子板1的校正数据包2,重复以上步骤,直至子阵1所有的校正数据装载完毕,则子板1的初始装载操作完成。当子板1等待数据输出时,子板2可发送读取数据请求,由于等待数据输出时间较长,不同plane间的数据操作可认为是同步操作,而对相同plane的读写操作必须等待当前操作结束后再发送请求。若单个子板的初始装载操作时间为t0,波束控制系统包括m个子板,初始数据空间按物理结构由n个plane组成,则完成m块子板的初始装载操作时间t

sum

满足远小于顺序完成m块子板的初

始装载操作时间t’sum

=mt0。

55.配置存储空间的校正数据结构:

56.ddr存储阵列包括n片ddr,每片ddr包含m个bank;

57.存储顺序将阵元按照编号顺序依次存储入ddr1的bank1、ddr2的bank1,

……

,ddrn的bank1,ddr1的bank2、ddr2的bank2,

……

,直至历遍所有bank后,再从ddr1的bank1开始存储。

58.具体的,比如阵元1的校正数据存储在ddr1的bank1中,阵元2的校正数据存储在ddr2的bank1中,

……

,阵元16的校正数据存储在ddr2的bank8中;

59.由于阵元数超过总bank数,相应地,阵元17的校正数据存储在ddr1的bank1中,阵元18的校正数据存储在ddr2的bank1中,其他阵元的校正数据存储位置依此类推。

60.以阵元1为例,查询分发操作包括:

61.步骤21,波束控制子板接收到查询分发操作指令,进入查询分发操作状态;

62.步骤22,查询阵元1的校正数据,根据当前阵面工作频率查询阵元号、阵元1的初始幅度和初始相位,确定出阵元1的查询地址,将查询地址和读请求发送给ddr存储器;

63.步骤23,等待阵元1的数据输出;

64.步骤24,更新阵元1的校正数据。

65.其他阵元的初试装载操作相同,并且当阵元1执行步骤23时,阵元2同时执行步骤22,

66.完成所有阵元数据的查询和更新后,则查询分发操作完成。当阵元1等待数据输出时,阵元2可继续发送读取数据请求,对不同ddr的操作可认为是同步的,由于对同一ddr存储器,连续两次操作对象为不同bank,不存在预冲操作,所有操作可连续执行。若单个阵元的查询分发操作时间为t0=t

s23

+t

others

,其中t

s23

为执行步骤23所需时间,t

others

为执行其他步骤所需时间,子阵中包括p个阵元,q个ddr存储器,则完成p个阵元的查询分发操作时间远小于完成p阵元顺序执行查询分发操作的时间t

‘

sum

=pt0=pt

s23

+pt

others

。

67.下面,结合两个具体实施例对本技术进行阐述,

68.实施例一:

69.以某有源相控阵面为例,该阵面包括48个子阵,则该波束控制系统由1个波束控制主机和48个波束控制子板组成,波束控制主机和子板以fpga为控制核心,波束控制主机配置的nand flash存储阵列物理上由12个plane组成,波束控制子板配置的ddr存储阵列由2片ddr组成,每片ddr包括8个bank。波束控制主机配置48个光发送模块,每个子板配置1个光接收模块,波束控制主机和各个子板间形成48路一对一光链路,波束控制主机和各子板间通过该光链路传输校正数据,校正数据以数据流形式传输。

70.初始数据空间的校正数据结构如图1所示,子板1~子板12的校正数据分别存储在plane1~plane12,由于子板数超过plane数,相应地,子板13~子板24的校正数据分别存储在plane1~plane12,子板25~子板36的校正数据分别存储在plane1~plane12,子板37~子板48的校正数据分别存储在plane1~plane12。

71.校正数据的分布式快速分发方法的初始装载操作流水图如题2所示。对于子板1,

初始装载操作包括如下步骤:

72.步骤11:波束控制主机接收到初始装载操作指令,进入初始装载操作状态;

73.步骤12:波束控制主机发送读取子板1的校正数据包1的请求,子板1的校正数据存储在plane1中,子板的校正数据按照传输长度划分为多个校正数据包;

74.步骤13:波束控制主机等待子板1的数据输出;

75.步骤14:波束控制主机读取子板1的校正数据后,在校正数据前加入报文标识、报文长度、数据类型等信息,并通过光链路传输给子板1;

76.步骤15:子板1接收到校正数据后,将校正数据按照数据类型信息分别更新到2片ddr存储器中;

77.然后,波束控制主机请求子板1的校正数据包2,重复步骤12到步骤15,直至所有的校正数据装载完毕,则子板1的初始装载操作完成。

78.得益于初始数据空间的校正数据结构和fpga的并行操作特性,当子板1执行步骤13时,子板2可同时执行步骤12,当子板2执行步骤13时,子板3可同步执行步骤12,依次类推。由于初始装载操作中步骤13所需的时间最长,当子板12执行步骤12时,子板1~子板11仍然在执行步骤13,因此12块子板的初始装载操作可认为是并行执行的。对于不同plane,读写操作可并行执行,但对于相同plane,必须等待当前读写操作完成才能执行下一次操作,因此子板13必须等待子板12执行完步骤13后,才能执行步骤12。若单个子板的初始装载操作时间为t0,而采用本发明的初始数据空间的校正数据结构和操作步骤,实际完成48块子板的初始装载操作时间t

sum

满足4t0《t

sum

《8t0,远小于顺序完成48块子板的初始装载操作时间t’sum

=48t0,大大提高了校正数据分发效率。

79.实施例二:

80.仍以该有源相控阵面为例,每个子阵有64个阵元,因此每次查询分发操作需要查询64个阵元在某一工作状态的校正数据。

81.配置存储空间的校正数据结构如图3所示,ddr存储阵列由2片ddr组成,每片ddr包含8个bank,阵元1的校正数据存储在ddr1的bank1中,阵元2的校正数据存储在ddr2的bank1中,

……

,阵元16的校正数据存储在ddr2的bank8中,由于阵元数超过总bank数,相应地,阵元17的校正数据存储在ddr1的bank1中,阵元18的校正数据存储在ddr2的bank1中,其他阵元的校正数据存储位置依此类推。

82.校正数据的分布式快速分发方法的查询分发操作流水图如图4所示。对于阵元1,查询分发操作包括如下步骤:

83.步骤21:波束控制子板接收到查询分发操作指令后,进入查询分发操作状态;

84.步骤22:查询阵元1的校正数据,根据当前阵面工作频率freq、查询阵元号ch1、阵元1的初始幅度atten1和初始相位phase1,计算出阵元1的查询地址addr1={freq,ch1,atten1,phase1},该数据位于ddr1的bank1,将该地址和读请求发送给ddr1;

85.步骤23:等待阵元1的数据输出;

86.步骤24:更新阵元1的校正数据。

87.得益于配置存储空间的校正数据结构和fpga的并行操作特性,当阵元1执行步骤23时,阵元2可同时执行步骤22,对不同ddr的操作可认为是同步操作。对同一个ddr存储器,连续两次操作为同一bank时,需要执行预冲操作,再执行读取操作,两次操作间有较大延

时,采用本发明的数据结构,两次操作对象为不同bank,可同时执行。对于单个阵元的查询分发操作,若所需时间t0=t

s23

+t

others

,其中t

s23

为执行步骤23所需时间,t

others

为执行其他步骤所需时间,由于两个ddr的操作为并行执行,则64阵元的查询分发操作所需时间t

sum

=t

s23

+32t

others

,远小于64元顺序执行查询分发操作的时间t

‘

sum

=64t0,大大提高了校正数据分发效率。

88.本发明可以实现有源相控阵面校正数据的分布式快速分发,在初始装载操作阶段,快速将大量校正数据加载到配置数据空间,节省有源相控阵面准备时间,使阵面尽快具备作战能力,在查询分发操作阶段,快速获取各个阵元的校正数据,即校正后的波束控制码,实现有源相控阵面波束指向快速切换。

89.以上所述的本技术实施方式并不构成对本技术保护范围的限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1