基于对数运算系统的小型浮点运算单元及其在FPGA中的应用

基于对数运算系统的小型浮点运算单元及其在fpga中的应用

技术领域

1.本发明属于fpga设计领域,尤其涉及一种基于对数运算系统的小型浮点运算单元设计及其在机器学习等容错性计算中的应用。

背景技术:

2.随着多媒体技术、机器学习等技术的不断的发展,越来越多的应用领域具有较强的容错性,即适当的计算误差并不会影响最终的应用效果。在此背景下近似计算技术获得了学术界与工业界的广泛关注。近似计算不仅可以在模拟电路中实现(如:存内计算技术),也可以在数字电路中实现(如:近似逻辑综合算法,近似运算电路设计)。在近似运算电路设计领域,xilinx在2021年提出了基于6输入查找表的7比特小型浮点乘法器,成功应用于resnet-50神经网络。xilinx提出的小型浮点乘法器具有以下特征:

3.(1)输入为两个7比特浮点数(含指数位3比特(e)、尾数位3比特(f)、指数位偏置为4;当指数位为0时,该浮点数为0;当指数位为7时,该浮点数依然按照(-1)s×2e-4

×

(1+f)计算;非零最小值和最大值分别为0.125和15;该浮点数格式记为sfp《3,3》)。

4.(2)输出为一个9比特浮点数(含指数位4比特、小数位4比特、指数位偏置为8;该浮点数格式记为sfp《4,4》)。

5.(3)该小型浮点乘法器的核心为将乘积的结果存在6输入查找表中。

6.该方案不但避免了神经网络的量化训练,而且相比传统的基于int8的神经网络设计,将vu13p开发板上算力从25tops提升至40tops。在fpga上实现该乘法器只需要10个6输入查找表。

7.然而当输入数字的尾数大于3位,所消耗的硬件资源将显著增加,例如,乘法器改用sfp《3,4》的格式输入,sfp《4,5》的格式输出,resnet-50的精度将从98.8%提高到100.4%(32位浮点数乘法的精度为100%),但需要18个6输入查找表实现。因此,此方案在实现更高的计算精度时,将不适合硬件设计。

技术实现要素:

8.有鉴于此,本发明提出了一种基于对数运算系统的小型浮点运算单元,旨在解决现有技术中,输入乘数的尾数多于3位时,硬件资源显著增加的问题。本发明提出的运算单元还可以实现除法和幂函数的运算。

9.为实现上述目的,本发明提供了一种基于查找表的小型浮点乘法运算单元,技术方案如下:

10.基于对数运算系统的小型浮点运算单元,包括对数转换器、尾数运算器、反对数转换器和指数运算器。

11.进一步地,当小型浮点运算单元为乘法运算单元时,乘法运算单元包括对数转换器、尾数加法器、反对数转换器和指数加法器。

12.所述的对数转换器用于将sfp格式数据的3~5位尾数f

l

经过对数转换,得到slfp

格式下的尾数k

l

:k

l

=log2(1+f

l

)。

13.所述的尾数加法器通过加法器实现,是将slfp格式下的尾数k

l

与slfp格式下的3~4位尾数kw相加:kw+k

l

={carry,k};其中,carry是指数进位,k是乘积结果在slfp格式下的尾数。

14.所述的反对数转换器是将乘积结果在slfp格式下的尾数k从slfp格式转换为sfp格式,反对数转换器用于实现函数f=2

k-1。

15.所述的指数加法器包括加法器和0判断模块,其中,加法器是将3位指数ew和3位指数e

l

相加:e=ew+e

l

;0判断模块的作用是,若检测到两个乘数ew和e

l

的任意一个指数位为0,则产生清零信号clear,将乘积结果置零。

16.进一步地,当小型浮点运算单元为除法运算单元时,在乘法运算单元基础上进行调整,通过计算slfp格式下尾数的差得到sfp格式下尾数的商,用对数域内的减法实现除法。

17.进一步地,当小型浮点运算单元为幂函数运算单元时,在乘法运算单元基础上进行调整,通过计算slfp格式下指数和尾数的乘积得到sfp格式下指数和尾数的幂,用对数域内的乘法实现幂运算。

18.进一步地,slfp格式数据的表示方法:使用动态指数偏置;当指数为0时,数值视为0。

19.上述的基于对数运算系统的小型浮点运算单元在fpga中的应用,fpga电路包括对数转换电路、尾数运算电路、指数运算电路和反对数转换电路;所述对数转换电路的输入端连接sfp浮点数输入,输出端连接尾数运算电路的一个输入;所述尾数运算电路的另一个输入端连接对数域内的权值,输出的进位信号连接指数运算电路,输出的尾数结果连接反对数转换电路的输入;指数运算电路的输出和反对数转换电路的输出共同构成所述运算单元的输出;对数转换和尾数运算电路同时完成对输入数据和权重的数据格式转换和加法运算。

20.本发明的设计原理:

21.将对数域内指数e位,尾数m位的浮点数表示为slfp《e,m》。当e等于0时,该浮点数视为0。使用动态指数偏置,等于2

e-1

,在3位或4位指数情况下,偏置量分别等于4、8,可以消除指数运算中的“+4”操作。

22.所述的基于对数运算系统的小型浮点运算单元具有一个浮点数输入,一个对数域内的权重常数,一个浮点数输出,运算单元将完成输入和权重的乘法运算。其中,输入浮点数和权重常数的指数位长度为3位,尾数位长度为3~5位;输出数据的指数位长度为4位,尾数位长度为3~6位。

23.所述的基于对数运算系统的小型浮点运算单元,通过对数转换器将输入的sfp格式数据转换为对数域内的浮点数slfp格式数据,并通过尾数加法器用加法实现两个输入的浮点数尾数部分的乘法。

24.所述的基于对数运算系统的小型浮点运算单元中的反对数转换器用于将经尾数加法器乘积得到的结果从slfp格式转换回sfp格式。

25.在此乘法器的基础上,本发明提供的运算单元结构可以进一步应用于除法和幂函数技术方案如下:

26.将输入的浮点数转换到对数域内,对于除法运算单元,尾数除法可以通过对数域内的减法实现,用少量硬件资源即可完成除法运算;对于幂函数运算单元,尾数的幂可以通过对数域内的乘法实现。

27.表1sfp和slfp乘法器的硬件消耗

[0028][0029]

表2sfp和slfp乘法器的计算误差

[0030][0031][0032]

本发明提出的乘法运算单元与xilinx的sfp乘法器精度及消耗硬件资源情况对比见上表。其中,表2误差比的计算方法为:当前乘法器的平均绝对误差/sfp-1的平均绝对误差。由表可知,slfp-5的计算误差小于sfp-2,且硬件资源消耗减少了12个6输入查找表。

[0033]

本发明的优势在于:在实现较高精度乘法的同时大大减少硬件消耗,更适合在fpga上实现;经测试,达到较高精度的同时,吞吐量不会减少;支持多种精度,可根据需要选取,应用于不同的卷积层;支持除法和幂函数,适用范围更广。

附图说明

[0034]

图1是本发明实施例提供的小型浮点数和对数域内的小型浮点数的示意图。

[0035]

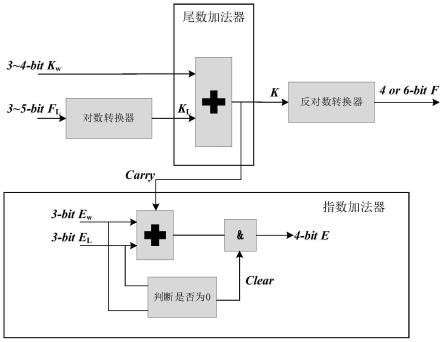

图2是本发明实施例提供的一种基于对数系统的小型浮点数乘法运算单元的硬件结构示意图。

[0036]

图3是本发明实施例提供的乘法器的一种电路示意图,3位kw,3位f

l

,输出尾数4位。

[0037]

图4是本发明实施例提供的乘法器的一种电路示意图,3位kw,4位f

l

,输出尾数4位。

[0038]

图5是本发明实施例提供的乘法器的一种电路示意图,4位kw,4位f

l

,输出尾数4位。

[0039]

图6是本发明实施例提供的乘法器的一种电路示意图,3位kw,5位f

l

,输出尾数6位。

[0040]

图7是本发明实施例提供的乘法器的一种电路示意图,4位kw,5位f

l

,输出尾数6位。

具体实施方式

[0041]

下面将结合实施例和附图,对本发明中的技术方案进一步描述。

[0042]

在本发明实施例中,将对数域内,指数e位,尾数m位的小浮点数格式记为slfp《e,m》。其中,slfp的指数位长度e为3或4;slfp的尾数位长度m可以根据精度要求,在3~6之间选择。

[0043]

图1是一个二进制浮点数,包括符号位,指数部分,尾数部分。在sfp或slfp格式下,一个二进制数表示不同的值。以3位指数,4位尾数的浮点数为例,其中指数部分e是0~7的整数,尾数部分m是0~(1-24)的小数。此二进制数在sfp格式下表示的值为(-1)s×2e-bias

×

(1+m),在slfp格式下表示的值为(-1)s×2e-bias

×2m

。其中,指数的偏置bias是一个变量,等于(max(e)+1)/2;s表示符号位,等于0或1。

[0044]

图2是所提出的slfp乘法器的硬件结构示意图。

[0045]

其中,卷积神经网络中的权重w应预先量化为slfp格式,为适应fpga的内存资源,权重w应小于8位,含3位指数ew和3~4位尾数kw。

[0046]

每个卷积层的输入具有3位指数e

l

,3~5位尾数f

l

,输出具有4位指数e

l

,3~5位指数f

l

。输入输出都被写成sfp格式。

[0047]

输入sfp格式数据的尾数f

l

经过对数转换,得到slfp格式下的尾数k

l

,k

l

等于log2(1+f

l

)。

[0048]

将sfp格式的输入l写成slfp格式,也就是将重写成因为权重w也是slfp格式,即所以每个卷积层输入和权重的乘积可以表示为因此尾数部分的计算可以通过加法器实现,kw+k

l

={carry,k}。其中,carry是指数进位,k是乘积结果在slfp格式下的尾数。

[0049]

指数加法部分由加法器和0判断模块组成。其中,0判断模块的作用是,若检测到两个乘数的任意一个指数位为0,则产生清零信号clear,将乘积结果置零。

[0050]

两个乘数的指数部分有3位,偏置等于4;输出的指数部分4位,偏置等于8。两数相乘,其指数值等于(e

w-4)+(e

l-4),等于ew+e

l-8。输出的指数位等于e-8。因此,e=ew+e

l

,与标准浮点格式相比,该方法不需要对输出的偏置进行处理,可以消除“+4”操作。

[0051]

最后,如前所述,输出应通过反对数转换器将数据从slfp格式转换为sfp格式,反对数转换器用于实现函数f=2

k-1。

[0052]

图7是本发明实施例提供的一个尾数计算和反对数转换模块的电路示意图,适用于具有5位尾数的输入l和具有4位尾数的权重w,通过使用6输入查找表和fpga中的超前快速进位逻辑结构carry4实现,以降低延迟,提高运算单元的吞吐量。

[0053]

对图3的详细说明如下:

[0054]

(1)超前快速进位逻辑结构carry4的输入s为传输信号,来自6输入查找表的输出,应等于k

w xorf

l

。carry4的输入d为进位标志信号,来自5输入查找表或外部电路,应等于f

l

。k

l

{[-1:-4],0}+k

l

[-1:-5]的结果应该等于{carry,k[-1,-5]},其中,k

l

[-1:-5]=log2(f

l

[-1:-5]),carry是传递给指数部分的进位信号。图中,carry[0:3]和sum[0:3]是超前快速进位逻辑结构carry4的输出。

[0055]

(2)将f

l

进行对数转换,得到k

l

[-1:-5]=log(f

l

[-1:-5])。

[0056]

(3)每个6输入查找表由2个5输入查找表和一个多路选择器构成。在图3中,lut_1~lut_4上方的5输入查找表用于执行一个5输入函数:log(f

l

[-1:-5])xorlogic0。6输入查找表lut_1~lut_4下方的5输入查找表用于执行5输入函数:log(f

l

[-1:-5])xorlogic1。由此实现对数转换并得到carry4的传输信号。

[0057]

(4)通过与(2)相似的方法,用6输入查找表lut_5~lut_7实现反对数转换器。其中,f[-1:-5]=2

k[-1:-5]

。

[0058]

根据此实施例,8个6输入查找表可以有效地实现4位尾数和5位尾数的乘法,并在两个查找表的延迟内完成计算。

[0059]

图3~6为本发明实施例提供的其它精度下尾数计算和反对数转换模块的电路示意图。

[0060]

图3~7是流水线结构,保证了slfp乘法器的吞吐量。

[0061]

该运算单元实现除法的过程如下:将浮点数输入x1和x2写成slfp格式,也就是将重写成将重写成因此,除法计算可以通过对数域内的减法实现,可以通过对数域内的减法实现,尾数加法器用于进行对数域内尾数的减法计算,当k1≥k2时,借位信号borrow=0,尾数k=k

1-k2;否则,借位信号borrow=1,尾数k=1-k

1-k2。指数加法器用于进行指数位的减法计算,e=e

1-e2+bias

e-borrow,其中biase是输出数据的动态偏置。当x1=0时,输出为0;当x2=0时,输出最大值,即将指数和尾数的各位置为1。最后用反对数转换器将结果转换成浮点数。

[0062]

该运算单元实现幂函数的过程如下:将浮点数x写成slfp格式,也就是将2

e-bias

×

(1+f)重写成2

e-bias

×2k

;幂函数的运算可以通过对数域内的乘法实现,xa=2

a(e-bias)

×2ak

。浮点数通过对数转换器转换为对数格式后,分别进行指数和尾数的乘法计算,将结果用slfp格式表示,再通过反对数转换器转换成浮点数格式。

[0063]

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1