一种多图层拼接显示控制方法和装置与流程

1.本发明涉及视频处理技术领域,特别是涉及一种多图层拼接显示控制方法和装置。

背景技术:

2.随着计算机技术的发展,人们对于显示屏的分辨率期望越来越高,如逐渐期望8k超高清视频的传输与显示,高分辨率意味着大数据量,自然需要更高的数据处理频率,但基于现行的图层数据处理标准和现有的芯片制作工艺,想要制作出能够满足8k分辨率的视频显示控制器芯片仍存在挑战。

3.现有技术实现过程首先碰到的问题一是后端收敛频率过高,即数据处理频率要求高,使用常规的10nm左右的芯片无法满足其后端收敛的问题,且当显示屏需进行多图层的叠加显示时,图层的增加将直接导致所需处理数据量的增倍,这将进一步提高对芯片的数据处理能力的要求,而在成本、制造工艺等条件限制下,现有的芯片无法满足该要求,导致8k分辨率的超高清视频显示存在难以解决的瓶颈。

4.鉴于此,克服该现有技术所存在的缺陷是本技术领域亟待解决的问题。

技术实现要素:

5.本发明要解决的技术问题是现有技术中所制造的芯片的数据处理频率无法满足超高清高分辨率视频的处理需求,导致无法实现超高清高分辨率视频的显示。

6.本发明采用如下技术方案:

7.第一方面,本发明提供了一种多图层拼接显示控制方法,将显示屏划分为至少两块独立的显示区域,每块显示区域对应各自独立的显示处理模块,各个独立的显示处理模块由拼接控制模块进行统一的管理,所述方法包括:

8.拼接控制模块从各图层所对应内存中读取图层数据,若在读取到的单层或多层图层数据中,每一层图层数据均为图像数据时,由拼接控制模块自行进行图层数据的处理,根据显示屏的参考坐标系,对图层数据进行处理得到完整视频帧数据;

9.若在读取到的单层或多层图层数据中,至少存在一层图层数据为视频数据时,则根据显示区域的划分和对应图层数据的坐标信息,将每一层图层数据拆分为对应的第一数据和第二数据,并分别由第一显示驱动模块和第二显示驱动模块进行处理,得到对应显示区域的区域视频帧数据,由拼接控制模块对区域视频帧数据进行拼接得到完整视频帧数据;

10.所述拼接控制模块驱动显示屏的显示接口,进行所述完整视频帧数据的显示。

11.优选的,所述根据显示区域的划分和对应图层数据的坐标信息,将每一层图层数据拆分为对应的第一数据和第二数据,具体包括:

12.所述拼接控制模块根据图层数据的坐标信息和所述显示屏的参考坐标系,得到所述图层数据在所述参考坐标系中所对应的图像区域,计算所述图像区域位于第一显示区域

中的部分在所述第一显示区域中的第一区域占比,和所述图像区域位于第二显示区域中的部分在所述第二显示区域中的第二区域占比;

13.根据所述第一区域占比和所述第二区域占比,确定所述图层数据的拆分方式,从而将所述图层数据拆分为第一数据和第二数据。

14.优选的,当所述第一区域占比与第二区域占比之间的差值不大于预设差值时,所述根据所述第一区域占比和所述第二区域占比,确定所述图层数据的拆分方式,从而将所述图层数据拆分为第一数据和第二数据,具体包括:

15.拼接控制模块将所述图层数据发送给第一显示处理模块和第二显示处理模块;

16.所述第一显示处理模块从所述图层数据中拆分得到第一数据;

17.所述第二显示处理模块从所述图层数据中拆分得到第二数据。

18.优选的,当所述第一区域占比与第二区域占比之间的差值大于预设差值时,所述根据所述第一区域占比和所述第二区域占比,确定所述图层数据的拆分方式,从而将所述图层数据拆分为第一数据和第二数据,具体包括:

19.拼接控制模块根据所述第一区域占比和所述第二区域占比,确定对应的主显示处理模块和副显示处理模块,所述拼接控制模块将所述图层数据发送给主显示处理模块;

20.所述主显示处理模块对所述图层数据进行拆分,得到第一数据和第二数据,并向副显示处理模块发送所对应的第一数据或第二数据,以便于相应显示处理模块进行处理得到对应显示区域的区域视频帧数据;其中,以第一区域占比和第二区域占比中较大的一方所对应的显示处理模块作为主显示处理模块,以另一方所对应的显示处理模块作为副显示处理模块。

21.优选的,所述主显示处理模块对所述图层数据进行拆分,得到第一数据和第二数据,具体包括:

22.所述主显示处理模块根据所述显示屏的参考坐标系和图层数据中各像素点的坐标信息,将所述图层数据中的各像素点投射至所述参考坐标系,得到完整图层帧数据;

23.根据第一区域和第二区域的划分,将所述完整图层帧数据进行拆分得到所述第一数据和第二数据;或,

24.所述主显示处理模块根据第一区域和第二区域的划分以及图层数据中各像素点的坐标信息,将所述图层数据进行拆分得到第一中间数据和第二中间数据;

25.根据所述显示屏的参考坐标系,将所述第一中间数据中的各像素点投射至第一区域,得到第一数据,将所述第二中间数据中的各像素点投射至第二区域,得到第二数据。

26.优选的,所述分别由第一显示驱动模块和第二显示驱动模块进行处理,得到对应显示区域的区域视频帧数据,具体包括:

27.根据各图层数据的层级显示顺序,第一显示驱动模块将多个图层数据所对应的第一数据按照所述层级显示顺序进行图层叠加处理,得到第一区域视频帧数据;

28.第二显示驱动模块将多个图层数据所对应的第二数据按照所述层级显示顺序进行图层叠加处理,得到第二区域视频帧数据。

29.优选的,若用户设置有显示区域划分方式,则按照用户所设置的划分方式进行显示区域的划分;

30.若用户未设置显示区域划分方式,则按照左右均分的方式或上下均分的方式,将

显示屏划分为第一显示区域和第二显示区域;或,

31.按照像素点排列的奇偶性,将在水平排列方向上或在竖直排列方向上,位于奇数位置的像素点划分给第一显示区域,位于偶数位置的像素点划分给第二显示区域。

32.优选的,所述方法还包括支持至少双路输入视频的显示,具体包括:

33.各个显示处理模块分别从对应内存中读取对应显示区域的图层数据,并对各显示区域的图层数据进行处理得到对应的区域视频帧数据,由拼接控制模块对各区域视频帧数据进行拼接,以在单块显示屏中实现多视频的显示。

34.优选的,第一显示处理模块的第一工作参考时钟和第二显示处理模块的第二工作参考时钟同步;

35.所述第一工作参考时钟的频率和所述第二工作参考时钟的频率均为显示屏的需求时钟频率的一半。

36.第二方面,本发明还提供了一种多图层拼接显示控制装置,用于实现第一方面所述的多图层拼接显示控制方法,所述装置包括:

37.至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述处理器执行,用于执行第一方面所述的多图层拼接显示控制方法。

38.第三方面,本发明还提供了一种非易失性计算机存储介质,所述计算机存储介质存储有计算机可执行指令,该计算机可执行指令被一个或多个处理器执行,用于完成第一方面所述的多图层拼接显示控制方法。

39.本发明通过对图像数据和图层数据区分处理,将数据处理频率要求低的图像数据直接处理显示,将数据处理频率要求高的图层数据进行拆分,分别交由各自显示区域的显示处理模块进行处理,从而降低单个显示处理模块所需处理的数据量,降低对显示处理模块的数据处理频率要求,从而实现高分辨率超高清视频的显示。

附图说明

40.为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例中所需要使用的附图作简单地介绍。显而易见地,下面所描述的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

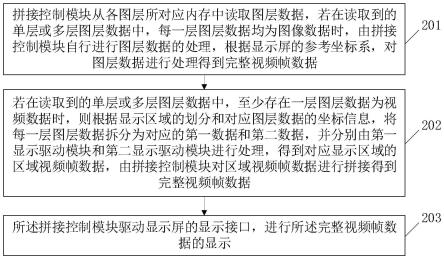

41.图1是本发明实施例提供的一种多图层拼接显示控制方法的流程示意图;

42.图2是本发明实施例提供的一种多图层拼接显示控制方法在处理图像数据时的示意图;

43.图3是本发明实施例提供的一种多图层拼接显示控制方法在处理图层数据时的示意图;

44.图4是本发明实施例提供的一种多图层拼接显示控制方法中显示区域划分的示意图;

45.图5是本发明实施例提供的一种多图层拼接显示控制方法的流程示意图;

46.图6是本发明实施例提供的一种多图层拼接显示控制方法的流程示意图;

47.图7是本发明实施例提供的一种多图层拼接显示控制方法的流程示意图;

48.图8是本发明实施例提供的一种多图层拼接显示控制方法的示意图;

49.图9是本发明实施例提供的一种多图层拼接显示控制方法在处理图层数据时的示意图;

50.图10是本发明实施例提供的一种多图层拼接显示控制方法的示意图;

51.图11是本发明实施例提供的一种多图层拼接显示控制方法的示意图;

52.图12是本发明实施例提供的一种多图层拼接显示控制装置的架构示意图。

具体实施方式

53.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

54.此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

55.现有技术中所制造的芯片的数据处理频率无法满足超高清高分辨率视频的处理需求,导致无法实现超高清高分辨率视频的显示。为了解决此问题,本发明实施例提供了一种多图层拼接显示控制方法,将显示屏划分为至少两块独立的显示区域,每块显示区域对应各自独立的显示处理模块,各个独立的显示处理模块由拼接控制模块进行统一的管理。

56.可以理解的是,在实际使用中,还可将所述显示屏划分为两块以上显示区域,如4块显示区域或更多块显示区域,每块显示区域对应各自的显示处理模块,从而可实现每块显示区域的视频显示。本实施例将以划分为两块独立的显示区域进行阐述,但需要在此说明的是,将显示屏划分为两块以上数量的显示区域同样是可行的,其同样应包含在本发明的保护范围内,本发明对此不做限制。所述显示处理模块在实际实现中可以是视频显示控制器。

57.所述多图层拼接显示控制方法如图1所示,包括:

58.在步骤201中,拼接控制模块从各图层所对应内存中读取图层数据,若在读取到的单层或多层图层数据中,每一层图层数据均为图像数据时,由拼接控制模块自行进行图层数据的处理,根据显示屏的参考坐标系,对图层数据进行处理得到完整视频帧数据,所述完整视频帧数据可直接输入显示接口进行显示,如图2所示。

59.其中,一个视频内容可能需要多个图层进行叠加显示,举例而言,当需对电脑的操作界面进行显示器显示时,当电脑进入待机状态,仅显示待机图片时,仅包含单个图层,而当电脑进入使用状态时,其可能包括电脑桌面、前端应用以及光标图层这三层图层。每个图层均对应一个内存,在该内存中存储对应的图层数据,如设置多个dma(direct memory access,直接存储器访问),每个dma对应一个图层的图层数据,为了描述的便利性,将每个图层的图层数据称作一层图层数据。

60.本实施例还提供了一种判断图层数据为图像数据或视频数据的可选的实施方式,具体包括,当图层数据的帧率大于预设帧率,则认为所述图层数据为图层数据,否则为图像数据。所述预设帧率由本领域技术人员根据经验分析得到。

61.所述图像数据又包括静态图像数据和动态图像数据,在此认为凡是低于预设帧率的图层数据均可视做图像数据进行处理,使用拼接控制模块进行处理即可满足其显示需

求。

62.所述根据显示屏的参考坐标系,对图层数据进行处理得到完整视频帧数据,具体包括:先对各图层数据进行处理得到对应的图层帧数据,将各图层帧数据进行图层的叠加,得到完整视频帧数据。将所述视频帧数据输入至显示接口,即可实现视频的显示。

63.在实际实现中,图层数据的坐标信息通常并非与显示屏完全适配,还需经过处理,如拉伸、缩放等操作,以将图层数据中各像素点的位置投射至显示屏的参考坐标系中,从而匹配显示屏的分辨率进行显示,其中还可能涉及图层数据的格式转换等操作,处理后的数据即为所述图层帧数据,由图层数据处理得到图层帧数据的过程为本领域技术人员的公知技术手段,在此不加以赘述。

64.在步骤202中,若在读取到的单层或多层图层数据中,至少存在一层图层数据为视频数据时,则根据显示区域的划分和对应图层数据的坐标信息,将每一层图层数据拆分为对应的第一数据和第二数据,并分别由第一显示驱动模块和第二显示驱动模块进行处理,得到对应显示区域的区域视频帧数据,由拼接控制模块对区域视频帧数据进行拼接得到完整视频帧数据,如图3所示。

65.其中,将划分得到的两块显示区域分别称作第一显示区域和第二显示区域,对应将第一区域的显示处理模块称作第一显示处理模块,将第二区域的显示处理模块称作第二显示处理模块。

66.所述图层数据为用于显示视频的数据的统称,其通常包括多个像素点信息,将这些像素点投射至显示屏的参考坐标系中时,一些像素点可能落于第一显示区域,另一些像素点落于第二显示区域,从而根据此进行第一数据和第二数据的拆分,即位于第一显示区域的所有像素点信息组成该图层数据的第一数据,位于第二显示区域的所有像素点信息组成该图层数据的第二数据。

67.所述将每一层图层数据拆分为对应的第一数据和第二数据可以由各显示驱动模块或拼接控制模块中的任意一个模块进行实现。

68.在此需要说明的是,本实施例中的第一数据和第二数据等限定性表述并非单独指代某一特定的数据,而是相对于图层数据而言的,即对于步骤202中的每一个图层数据,均被拆分为对应的第一数据和第二数据,举例而言,若存在图层a和图层b,图层a的图层数据被拆分为图层a所对应的第一数据a_1和第二数据a_2,图层b的图层数据被拆分为图层b所对应的第一数据b_1和第二数据b_2,在本实施例中第一数据a_1和第一数据b_1均以第一数据的形式进行描述,具体描述为哪一数据则由所在描述中所对应的图层或图层数据决定。

69.在步骤203中,所述拼接控制模块驱动显示屏的显示接口,进行所述完整视频帧数据的显示。

70.本实施例由至少两路独立的视频显示控制器(即上述的显示处理模块)输出左右两边独立图像,经过一个统一的拼接控制模块输出一路视频,该路视频可支持到8k分辨率独立显示。由拼接控制模块驱动dp1.4以上标准或者hdmi2.1以上标准的显示接口,实现显示器的超高清的显示。采用此方法,可以使2个独立的视频显示控制器可以降低一倍的工作时钟频率,同时两路视频显示控制器还可以独立的驱动两个显示接口,实现分屏独立显示,从而实现较大的灵活性。

71.本实施例通过拼接控制模块、第一显示处理模块和第二显示处理模块三方合作,

进行图像和视频的显示,其中,由于图像数据帧率低,数据量较低,所要求的数据处理频率不高,则由拼接控制模块直接处理,以减少流程的复杂性。而视频数据帧率较高,其数据量较大,所要求的数据处理频率相对较高,故而对数据进行拆分,并通过两个显示处理模块分别处理,从而满足其数据处理频率要求,如在显示屏分辨率过高,而单个硬件芯片的处理速度无法满足其处理现实需求的情况下,使用本实施例所述的方法。

72.其中,所述显示区域的划分可以由用户自定义设置,若用户设置有显示区域划分方式,则按照用户所设置的划分方式进行显示区域的划分;

73.若用户未设置显示区域划分方式,则按照左右均分的方式或上下均分的方式,将显示屏划分为第一显示区域和第二显示区域。

74.或按照像素点排列的奇偶性,将在水平排列方向上或在竖直排列方向上,位于奇数位置的像素点划分给第一显示区域,位于偶数位置的像素点划分给第二显示区域。所述水平排列方向和竖直排列方向是相对于显示屏而言的。

75.如所述显示屏的分辨率为7680

×

4320,即8k分辨率时,对显示屏划分所得到的第一显示区域的分辨率和第二显示区域的分辨率均为3840

×

4320。

76.在实际实现中,还存在多种可选的显示区域划分方式,如按照对应的区域面积比例进行划分,又或划定显示屏中的某一块区域为第一显示区域,该区域外的部分作为第二显示区域。

77.显示区域的划分方式还可根据所选用的显示处理模块的性能特性分析得到,如根据第一显示处理模块与第二显示处理模块所对应的用于存储区域视频帧数据的fifo的大小,将显示屏按照fifo大小的比例,进行显示区域划分,或按照显示处理模块的时钟频率进行显示区域的划分。举例而言,当第一显示处理模块的fifo空间大小与第二显示处理模块的fifo空间大小比例为2:1时,可将显示屏的三分之一划分为第二显示区域,将显示屏的三分之二划分为第二显示区域,同理,当第一显示处理模块的时钟频率与第二显示处理模块的时钟频率比例为2:1时,也可进行上述划分。

78.对应不同显示区域的划分方式或不同的图层数据,所拆分得到的第一数据和第二数据也不同。以对8k显示屏进行左右均分得到第一显示区域和第二显示区域为例,如图4所示,采用最终合并后的8k显示系统的坐标系作为一个统一的参考坐标系,显示器左上角为原点(0,0),自此开始水平向左为x轴方向,自此开始垂直向下为y轴方向,步长为整数1。若图层数据为基础图层,即覆盖显示屏全屏,则可按照图4所示的左侧视频分辨率为3840

×

4320,右侧视频的分辨率也为3840

×

4320的方式进行第一数据和第二数据的拆分,若视频内容仅由基础图层一层数据组成,则对左右两个视频进行无损的拼接处理后将会组成一个完整的8k分辨率视频。若涉及多个图层,则还需进行图层的叠加处理。

79.在实际应用场景中,在进行图层数据的拆分时,需对每个像素点所属的显示区域进行判定,其仍需要较大的数据处理能力,而为了降低生产成本,所述拼接控制模块的性能通常较低,可能无法满足数据拆分的需求,为了解决此问题,本实施例提供了以下优选的实施方式,即所述根据所述图层数据的坐标信息,将所述图层数据拆分为第一数据和第二数据,分别交由对应的第一显示处理模块和第二显示处理模块进行处理,得到对应的区域视频帧数据,并驱动对应的显示接口在对应的显示区域进行显示,如图5所示,具体包括:

80.在步骤301中,所述拼接控制模块根据图层数据的坐标信息和所述显示屏的参考

坐标系,得到所述图层数据在所述参考坐标系中所对应的图像区域,计算所述图像区域位于第一显示区域中的部分在所述第一显示区域中的第一区域占比,和所述图像区域位于第二显示区域中的部分在所述第二显示区域中的第二区域占比。

81.其中,在大多数情况下,若所述图层数据需要全屏显示,则所述图层数据的第一区域占比和第二区域占比均为1,但在实际使用中,也可能出现视频并不需要全屏显示的情况,如在进行投影时,若投影前设备的分辨率与投影后设备的分辨率差距大,且无法伸缩匹配,若进行拉伸显示,会导致投影的变形,而为了确保不发生形变,通常会牺牲分辨率,而只在显示屏的部分区域进行显示。或在一些情况下,如会议或广告投放时,可能存在在显示屏的部分区域放置静态图片(如会议标题文字图片或广告语图片),而在其他区域显示视频的情况,故由拼接控制模块根据图层数据进行判断,由于视频通常是以规则的四边形形状进行放映,故所述拼接控制模块仅需对图层数据中位于四边形各顶点的像素点数据投射至显示屏的参考坐标系中,即可得到对应的图像区域,从而无需对每个像素点数据进行处理,减少其数据处理的压力。

82.在步骤302中,根据所述第一区域占比和所述第二区域占比,确定所述图层数据的拆分方式,从而将所述图层数据拆分为第一数据和第二数据。

83.本实施例还针对上述步骤302提供了一种可选的实施方式,如图6所示,具体包括:

84.在步骤401中,当所述第一区域占比与第二区域占比之间的差值不大于预设差值时,拼接控制模块将所述图层数据发送给第一显示处理模块和第二显示处理模块;所述预设差值是由本领域技术人员根据经验分析得到的。

85.在步骤402中,所述第一显示处理模块从所述图层数据中拆分得到第一数据;所述第二显示处理模块从所述图层数据中拆分得到第二数据。

86.当第一区域占比与第二区域占比之间的差值不大于预设差值时,说明图层数据在第一显示区域和第二显示区域中所占用的区域面积比例相差不大,故将图层数据既发送给第一显示处理模块,又发送给第二显示处理模块,由这两个显示处理模块自行进行数据的拆分处理。

87.如图7所示,上述步骤302还包括:

88.在步骤501中,当所述第一区域占比与第二区域占比之间的差值大于预设差时,拼接控制模块根据所述第一区域占比和所述第二区域占比,确定对应的主显示处理模块和副显示处理模块,所述拼接控制模块将所述图层数据发送给主显示处理模块。

89.在步骤502中,所述主显示处理模块对所述图层数据进行拆分,得到第一数据和第二数据,并向副显示处理模块发送所对应的第一数据或第二数据,以便于相应显示处理模块进行处理得到对应显示区域的区域视频帧数据;其中,以第一区域占比和第二区域占比中较大的一方所对应的显示处理模块作为主显示处理模块,以另一方所对应的显示处理模块作为副显示处理模块。

90.其中,当以第一显示处理模块为主显示处理模块,第二显示处理模块为副显示处理模块时,所述并向副显示处理模块发送所对应的第一数据或第二数据,具体为:第一显示处理模块向第二显示处理模块发送第二数据。反之,当以第二显示处理模块为主显示处理模块,第一显示处理模块为副显示处理模块时,所述并向副显示处理模块发送所对应的第一数据或第二数据,具体为:第二显示处理模块向第一显示处理模块发送第一数据。

91.在此需要说明的是,本实施例中所有拆分得到第一数据和第二数据的描述,或与此相近的描述,均是为了体现本实施例中的数据拆分过程所做的替代性描述,其实际上还应包含有数据的处理过程,即图层数据并非直接包含第一数据和第二数据,而是可理解为由第一中间数据和第二中间数据组成,图层数据、第一中间数据和第二中间数据均无法直接提供给显示接口进行显示,而对第一中间数据处理可得到可被显示接口处理显示的第一数据,对第二中间数据处理可得到可被显示接口处理显示的第二数据,将第一数据和第二数据进行对应的图层叠加处理或拼接后即可提供给显示接口进行全显示屏的显示,即上述拆分不仅仅包括数据的拆分本身,还包括数据的转换、处理等中间过程,即所述主显示处理模块对所述图层数据进行拆分,得到第一数据和第二数据,具体包括:

92.所述主显示处理模块根据所述显示屏的参考坐标系和图层数据中各像素点的坐标信息,将所述图层数据中的各像素点投射至所述参考坐标系,得到完整图层帧数据;所述完整图层帧数据可理解为单个图层所对应的可供全显示屏显示的数据。

93.根据第一区域和第二区域的划分,将所述完整图层帧数据进行拆分得到所述第一数据和第二数据;或,

94.所述主显示处理模块根据第一区域和第二区域的划分以及图层数据中各像素点的坐标信息,将所述图层数据进行拆分得到第一中间数据和第二中间数据。

95.根据所述显示屏的参考坐标系,将所述第一中间数据中的各像素点投射至第一区域,得到第一数据,将所述第二中间数据中的各像素点投射至第二区域,得到第二数据。

96.当第一区域占比与第二区域占比之间的差值大于预设差值时,则认为图层数据在第一显示区域和第二显示区域中所占用的区域面积比例相差较大,则将图层数据发送给主显示处理模块进行处理,即图层数据在哪个区域占用面积比例较多,则将图层数据交由哪个显示处理模块处理,由主显示处理模块进行拆分处理,得到第一数据和第二数据,再将第一数据和第二数据交由对应显示处理模块处理。

97.即在上述各实施方式中,由图层数据处理得到完整视频帧数据需包含图层数据的拆分处理(包括像素点的映射等操作)、图层的叠加,以及显示区域数据的合并这三个过程。而在本优选实施方式中,由主显示处理模块既进行图层数据的拆分处理,并进行自身对应显示区域中图层的叠加,而副显示处理模块则只根据主显示处理模块拆分处理后的部分数据,进行图层的叠加。从而通过由主显示处理模块承担数据的拆分处理,将拆分处理的数据直接复用给副显示处理模块,从而减少整体所需处理的数据量,提高数据处理的效率。

98.举例而言,如图8所示,将显示屏按照左右均分得到第一显示区域和第二显示区域,若按照从底层到上层的顺序,存在两层图层数据,分别为图层数据layer1和图层数据layer2,layer1的图像区域覆盖显示屏整体,则拼接控制模块将图层数据layer1发送给第一显示处理模块和第二显示处理模块,从而进行后续处理。layer2的图像区域如图8中带阴影的矩形所示,其一部分位于第一显示区域,另一部分位于第二显示区域,若位于第一显示区域中的部分占第一显示区域总面积的比例(即第一区域占比)为位于第二显示区域中的部分占第二显示区域总面积的比例(即第二区域占比)为则第一区域占比与第二区域占比之间的差值为若大于预设差值,则以占用面积比例较多的一方,即对于layer2而言,

第一显示区域所对应的第一显示处理模块为主显示处理模块,第二显示处理模块为副显示处理模块。

99.则如图9所示,拼接控制模块将图层数据layer1和图层数据layer2发送给第一显示处理模块,第一显示处理模块将图层数据layer1拆分得到layer1的第一数据layer1_data1,将图层数据layer2拆分得到layer2的第一数据layer2_data1和layer2的第二数据layer2_data2,第一显示处理模块将layer1_data1和layer2_data1叠加得到第一区域视频帧数据,同时,还将拆分得到的第二数据layer2_data2发送给第二显示处理模块。

100.拼接控制模块将图层数据layer1发送给第二显示处理模块,第二显示处理模块将图层数据layer1拆分得到layer1的第二数据layer1_data2,第二显示处理模块将从第一显示处理模块接收到的layer2_data2和自身拆分得到的layer1_data2进行叠加处理得到第二区域视频帧数据,从而用于后续的区域数据拼接和显示。其中,在进行叠加得到第二区域视频帧数据时,layer1_data2在layer2_data2的下层,根据layer2_data2的透明度不同,第二区域视频帧数据在如图8所示的图像区域的像素点呈现layer1_data2被layer2_data2覆盖的颜色或layer1_data2与layer2_data2像素叠加后的颜色。同样的,在进行叠加得到第一区域视频帧数据时,layer1_data2在layer2_data2的下层。

101.作为一种可选的实施方式,第一显示处理模块与第二显示处理模块可设置共同的内存空间,所述第一显示处理模块将第二数据写入所述内存空间,由第二显示处理模块读取调用第二数据。第一显示处理模块拆分得到的第一数据可直接由自身进行存储、读取或调用。

102.在实际使用中,当所需显示的视频内容仅对应一个图层数据时,无需进行图层的叠加,该图层数据所对应的完整图层帧数据即为完整视频帧数据,可直接通过显示接口进行显示。而当所需显示的视频内容对应多个图层数据时,则存在以下可选的实施方式,即所述分别由第一显示驱动模块和第二显示驱动模块进行处理,得到对应显示区域的区域视频帧数据,具体包括:

103.根据各图层数据的层级显示顺序,第一显示驱动模块将多个图层数据所对应的第一数据按照所述层级显示顺序进行图层叠加处理,得到第一区域视频帧数据。

104.第二显示驱动模块将多个图层数据所对应的第二数据按照所述层级显示顺序进行图层叠加处理,得到第二区域视频帧数据。

105.作为一种可选的实施方式,所述拼接控制模块对区域视频帧数据进行拼接得到完整视频帧数据,具体包括:

106.第一显示驱动模块将第一区域视频帧数据写入第一fifo,第二显示驱动模块将第二区域视频帧数据写入第二fifo,拼接控制模块根据自身的工作时钟读取第一fifo中和第二fifo中的数据,以进行各显示区域数据的同步拼接,以便于拼接控制模块将拼接后的完整视频帧数据输入至显示接口进行显示。

107.其中,每一个显示处理模块对应一个fifo,用于存储对应的区域视频帧数据。

108.为了确保所述第一数据和第二数据分别在第一显示区域和第二显示区域的同步刷新显示,当对显示屏进行均分划分得到第一显示区域和第二显示区域时,存在一种可选的实施方式为:所述第一显示处理模块的第一工作参考时钟和所述第二显示处理模块的第二工作参考时钟同步。且所述第一工作参考时钟的频率和所述第二工作参考时钟的频率均

为显示屏的需求时钟频率的一半。如在显示屏为8k分辨率时,要确保该显示屏中视频的流畅放映,当其使用单个显示处理模块处理整个显示屏的图层数据时,其所需的数据处理频率需至少为1188mhz,即所述需求时钟频率为1188mhz,而当将显示屏均分划分为两个显示区域,使用第一显示处理模块和第二显示处理模块分别进行数据处理时,所对应的所述第一工作参考时钟的频率和所述第二工作参考时钟的频率均为594mhz,即数据处理频率减半即可满足8k分辨率的显示需求。而为了确保能够及时向显示接口输入完整视频帧数据,所述拼接控制模块的工作参考时钟频率与需求时钟频率一致,即为1188mhz,但由于拼接控制模块仅需进行图层数据的分配和区域数据的拼接,其相对第一显示处理模块和第二显示处理模块而言,无需对数据进行复杂的映射处理,故对其数据处理能力性能要求较低,相对更易实现1188mhz的处理频率。

109.在上述各实施方式的基础上,所述方法还包括支持至少双路输入视频的显示,具体包括:

110.各个显示处理模块分别从对应内存中读取对应显示区域的图层数据,并对各显示区域的图层数据进行处理得到对应的区域视频帧数据,由拼接控制模块对各区域视频帧数据进行拼接,以在单块显示屏中实现多视频的显示。

111.作为另一种可实现的实施方式,还可通过连接两个显示屏,每个显示屏对应独立的显示接口,各个显示处理模块分别从对应内存中读取对应显示区域的图层数据,并对各显示区域的图层数据进行处理得到对应的区域视频帧数据,通过对应显示屏独立的显示接口进行区域视频帧数据的显示,从而实现多路视频的输出显示。如2个独立的显示处理模块独立处理两路完全独立的显示屏,这2个独立的视频显示控制器支持各种规格的数据格式。可以独立完成2路视频的处理,如驱动hdmi(high definition multimedia interface,高清晰度多媒体接口)、dp(displayport,显示接口)和vga(video graphics array,视频图形阵列接口)等显示接口在各显示屏进行独立的视频显示,从而通过独立的驱动两个显示接口,实现分屏独立显示,实现较大的灵活性。

112.上述多图层拼接的显示方式和多显示屏独立显示的显示方式可通过在设备中设置多种处理模式实现切换,即提供两种处理模式,包括拼接模式和非拼接模式,在拼接模式下,将显示屏默认划分为左右两个显示区域(分别为第一显示区域和第二显示区域,在后续实施例中,也以左侧、右侧的描述方式进行区分描述),由各自对应的视频显示控制器完成配置坐标信息的转换,使2路视频显示控制器自动的完成图像处理和显示位置控制等。也可由用户设置进行显示区域的划分。

113.在此基础上视频显示控制器还可以实现多个叠加图层的实现,其中在进行图层叠加时,还需考虑边界的处理,其中,所需叠加的数据的处理与上述各实施方式中的图层数据的处理方式基于同一构思,在此不再赘述。在此仅对叠加图层的边界处理以举例的形式进行阐述,具体包括:

114.如图10所示,在左右两侧的显示区域均显示有相应基础图层的基础上,还存在一个叠加图层,需覆盖在下层基础图层上进行显示,其分辨率为2345

×

1234,它本身在左边屏幕和右边屏幕存在跨越左右边界的需要,因此在左侧显示配置过程中存在右侧出边界裁剪的配置需求,右侧显示配置过程中存在左侧出边界裁剪的配置需求。而对于axi 256bit的数据总线,单次取回来的像素数据需满足32byte对齐的要求,因此在处理显示左边区域的

视频时,对应从左边区域的右边界超出该区域位置多取出0-8个像素,在处理显示右边区域的视频时,对应从右边区域左边界超出该区域位置多取出0-7个像素。在配置过程中,计算好左右边界处的裁剪数据,根据需要动态计算实现叠加图层的动态裁剪;作为一种特殊的情景,硬件光标在跨越左右屏幕时,也存在出边界的情况,由于特殊性,硬件光标不支持裁剪功能,而是通过配置小于1920的起始坐标来实现,最终出边界部分会被当做消隐区数据进行处理。

115.最终实现的结果是,两路独立的视频显示控制器在同一个参考坐标系下完成配置后,独立的输出给到拼接控制模块,拼接控制模块将完成合并后的8k标准视频的输出。在此设计中,拼接过程要求每一个有效行数据在预计的固定时隙到达拼接控制模块,也就是要求2个独立的显示处理模块以及拼接控制模块处理的行频保持一致,最终实现的帧频也保持一致,因此对于2个独立的显示处理模块来讲,如图11所示,它们两个的工作参考时钟pclk_a和pclk_b保持一致,并且属于同一个时钟域,从频率上讲需要被设计为拼接控制模块的工作参考时钟pclk_c的一半,即pclk_a和pclk_b的频率均为pclk_c的一半,相位可以保持为异步。如pclk_a和pclk_b均为594mhz,pclk_c为1188mhz。

116.在拼接控制模块进行视频拼接时,2路独立的视频显示处理模块输入进来的图层数据,将会逐行的被写入到2个独立的异步fifo,写入侧时钟保持为pclk_a和pclk_b,关键的,需要保证视频a和视频b有效信号data_en在此拼接模式下保证几乎一致的有效时隙,此设计中2路独立的显示处理模块采纳了同一个开始计时的触发信号,因此能保证2路视频的data_en_a(即上述的第一数据)和data_en_b(即上述的第二数据)能够完全对齐,退一步讲,可以在有限的时钟数下不一致,只要后续的2个异步fifo的缓存空间大小能够容忍这个时间差异即可,该可容忍时间差由本领域技术人员根据视频的刷新流畅性需求分析得到。

117.在进行视频拼接时,可采用左侧视频的那一路异步fifo的almost_full信号标志作为合并帧时序参数重建的开始正常读取有效数据合并的时间触发条件,该almost_full信号有一个寄存器可以控制的afull_threshold水位线,该水位线由本领域技术人员根据经验分析设定,在拼接模式下,当该异步fifo的已有的缓存数据个数即valid_entries计数大于afull_threshold水位线时,开始触发almost_full信号。因此保证了在读取数据时两个异步fifo中的数据能够保证不存在上、下溢出的风险,在拼接后能够保持持续的正确的帧结构输出。

118.在拼接模式下能够实现最大8k分辨率的拼接显示功能,同时在非拼接模式下,可以实现最大4k分辨率的2路独立视频的显示功能,灵活性大,效益高。

119.基于与本发明实施例的统一构思,将显示屏划分为多块显示区域,对应多个显示处理模块分别进行对应数据处理显示同样是可行的,其同样应包含在本发明的保护范围内,举例而言,将16k显示屏,即15360

×

8640分辨率的显示屏划分为4个显示区域,对应4个显示处理模块,从而可以使用常规的10nm左右的芯片制造工艺制造多个显示处理模块,从而相对容易的通过4路图层数据的拼接实现16k超高清分辨率的驱动显示。

120.如图12所示,是本发明实施例的多图层拼接显示控制装置的架构示意图。本实施例的多图层拼接显示控制装置包括一个或多个处理器21以及存储器22。其中,图12中以一个处理器21为例。

121.处理器21和存储器22可以通过总线或者其他方式连接,图12中以通过总线连接为

例。

122.存储器22作为一种非易失性计算机可读存储介质,可用于存储非易失性软件程序和非易失性计算机可执行程序,如上实施例中的多图层拼接显示控制方法。处理器21通过运行存储在存储器22中的非易失性软件程序和指令,从而执行多图层拼接显示控制方法。

123.存储器22可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他非易失性固态存储器件。在一些实施例中,存储器22可选包括相对于处理器21远程设置的存储器,这些远程存储器可以通过网络连接至处理器21。上述网络的实例包括但不限于互联网、企业内部网、局域网、移动通信网及其组合。

124.所述程序指令/模块存储在所述存储器22中,当被所述一个或者多个处理器21执行时,执行上述实施例中的多图层拼接显示控制方法。

125.值得说明的是,上述装置和系统内的模块、单元之间的信息交互、执行过程等内容,由于与本发明的处理方法实施例基于同一构思,具体内容可参见本发明方法实施例中的叙述,此处不再赘述。

126.本领域普通技术人员可以理解实施例的各种方法中的全部或部分步骤是可以通过程序来指令相关的硬件来完成,该程序可以存储于一计算机可读存储介质中,存储介质可以包括:只读存储器(rom,read only memory)、随机存取存储器(ram,random access memory)、磁盘或光盘等。

127.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1