面向硅介质层互联的高速低延迟互联接口的制作方法

本技术涉及高速物理接口设计,特别是涉及一种面向硅介质层互联的高速低延迟互联接口。

背景技术:

1、在dennard几何缩放失效后,关于半导体技术路线图提出在延续摩尔定律的同时,关注基于多样化封装的拓展摩尔定律。单片集成升级到片上系统(system on chip,soc)是半导体产业的一个里程碑式的发展,但是当技术节点进入深亚纳米后,不仅难度上升,而且设计费用昂贵,导致很难在有限市场容量中回收投入。

2、更加严峻的是,在面对大数据等高算力爆炸式增长的应用时,传统同构处理器已很难满足计算要求,需要附加专用加速器进行异构计算(hetergeneous computing,hc),完成异构计算则需要对不同芯粒进行异构集成。同时,适用于高密集型数据应用的高带宽存储器(high bandwidth memory,hbm)也需要进行异构集成,因此,亟需设计一种面向硅介质层互联的高速低延迟互联接口(high-speed low-latency interconnect interface,hlii)。

3、然而,由于与面向传统pcb(printed circuit board)层互联或sip(system in apackage)集成方式的接口设计不同,硅介质层互联需要完成异构芯粒间的大规模io的高速互联,因此面向硅介质层互联的高速低延迟互联接口架构无法沿用传统高速接口的设计,其数据传输效率和功耗也面临挑战。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种面向硅介质层互联的高速低延迟互联接口。

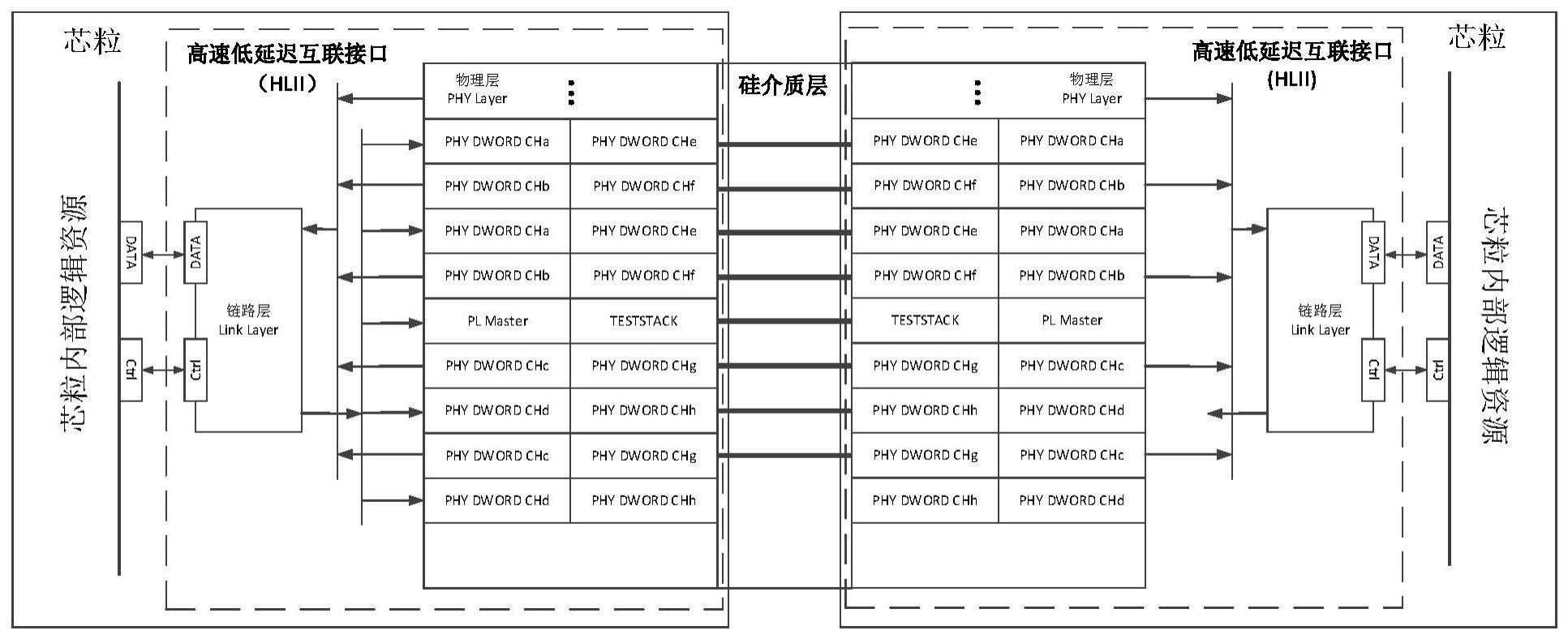

2、第一方面,本技术提供了一种面向硅介质层互联的高速低延迟互联接口,包括物理层以及,介于芯粒内部逻辑与所述物理层之间的链路层;

3、所述链路层,用于接收芯粒内部的信号,将芯粒内部的信号传输至物理层,以及,根据芯粒内部的信号,对所述物理层进行控制,其中,所述芯粒内部的信号包括数据信号,所述将芯粒内部的信号传输至物理层包括将数据信号进行数据转换后发送至所述物理层;

4、所述物理层,用于接收经由所述链路层传输的信号,将信号通过硅介质发射至另一个高速低延迟互联接口的物理层,以及,接收另一个高速低延迟互联接口物理层传输的信号,将信号传输至所述链路层,以由所述链路层接收后传输至芯粒内部。

5、在其中一个实施例中,所述芯粒内部的信号还包括配置信号和控制信号,所述对物理层进行控制包括对所述物理层进行数据转换、奇偶校验、训练、通道修复和指令流生。

6、在其中一个实施例中,所述物理层包括至少一个传输通道,所述链路层包括至少一个逻辑控制通道,其中,所述传输通道和所述逻辑控制通道的数量相同;

7、所述传输通道用于传输数据信号,所述传输数据信号的模式包括ddr传输模式和sdr传输模式;

8、所述逻辑控制通道用于对所述传输通道的数据流进行控制和调度。

9、在其中一个实施例中,每个所述传输通道包括多个传输子通道,每个所述传输子通道负责至少32bit的数据信号传输;

10、每个所述逻辑控制通道包括多个逻辑控制子通道,所述逻辑控制子通道和所述传输子通道一一对应,所述逻辑控制子通道用于控制和调度对应的传输子通道所传输的数据流。

11、在其中一个实施例中,所述传输子通道包括多个dword位片、发射时钟生成模块、接受时钟生成模块、dword fifo控制器、延迟线测试器和rx时钟驱动;

12、每个所述dword位片包括1个发送数据fifo、1个接收数据fifo、1个发送i/o和1个接收i/o;

13、所述发射时钟生成模块用于产生高速时钟;

14、所述接受时钟生成模块用于产生高速时钟和捕获读数据的时钟;

15、所述dword fifo控制器用于控制所述dword位片中的发送数据fifo和接收数据fifo;

16、所述延迟线测试器用于微调发送时钟上的延时,以将时钟集中于数据眼上;

17、所述rx时钟驱动用于增加时钟驱动。

18、在其中一个实施例中,所述逻辑控制子通道包括控制模块、延迟线控制器、dword环回bist、数据生成模块、数据检查模块;

19、所述控制模块用于控制数据路径,承载数据信号;

20、所述延迟线控制器用于dword延迟线的控制、校准和vt补偿;

21、所述dword环回bist用于回环和延迟线测试的bist逻辑;

22、所述数据生成模块和数据检查模块用于生成训练和测试的数据。

23、在其中一个实施例中,所述物理层还包括物理层matser和接口测试模块;

24、所述物理层matser用于为所述物理层提供全局时钟、复位信号和基准电压;

25、所述接口测试模块用于对高速低延迟互联接口进行功能性测试。

26、在其中一个实施例中,所述链路层还包括链路层master模块,所述链路层master模块包括配置模块、master状态寄存器、初始化引擎、训练控制器、复位与测试控制器、p1500控制器、指令流生成器和指令单元;

27、所述配置模块用于交互apb接口、tdr接口、jtag接口事务以进行csr的读写;

28、所述master状态寄存器包括所有能被整个接口共享的逻辑状态寄存器;

29、所述初始化引擎用于在硬件层面实现初始化流程并配合状态寄存器对高速低延迟互联接口进行初始化的操作;

30、所述训练控制器用于自动进行读延迟、读数据眼、写数据眼和基准电压训练;

31、所述测试控制器用于复位生成,校准i/o驱动的阻抗,提供数据接收i/o的全局基准电压、监控高速低延迟互联接口内部测试信号的测试输出i/o口和接口测试模块的i/o口;

32、所述p1500控制器用于生成测试用的p1500指令;

33、所述指令流生成器用于执行高速低延迟互联接口内部以及p1500命令的引擎;

34、所述指令单元用于完成高速低延迟互联接口内部指令地解码和分发工作。

35、第二方面,本技术还提供了一种面向硅介质层互联的高速低延迟互联拓扑结构,包括叠在硅介质层上的多个芯粒和每个芯粒对应的至少一个互联接口;

36、其中,所述互联接口为本技术第一方面所述的高速低延迟互联接口。

37、在其中一个实施例中,每个所述互联接口包括至少一个传输通道;多个所述互联接口的传输通道对称且相同,以支持多个互联接口之间的对接。

38、上述面向硅介质层互联的高速低延迟互联接口,包括物理层和链路层,链路层介于物理层与芯粒内部逻辑之间,链路层用于接收芯粒内部的信号,并可完成针对物理层的控制功能,物理层接收经过链路层传输的信号,例如链路层转换的数据信号,完成对该数据信号的发射与接收工作,例如将其通过硅介质发射至另一个高速低延迟互联接口的物理层,以及,接收另一个高速低延迟互联接口物理层传输的信号,将信号传输至所述链路层,以由所述链路层接收后传输至芯粒内部,完成面向硅介质层互联的高速低延迟互联接口间数据流的传输,以提供芯粒在硅介质层上无协议的高速数据传输,满足高效率数据传输和高性能功耗比等要求。

39、在部分实施例中,上述面向硅介质层互联的高速低延迟互联接口,可支持多个通道,每个通道支持数据并行传输,兼容ddr和sdr传输模式,其中每个通道中包含多个传输子通道,每个传输子通道可提供至少32bit数据传输。本技术的高速低延迟互联接口可被配置为1、2、4、8或更多通道模式以满足不同案例的设计需求。所有高速低延迟互联接口的通道都是对称且相同的,对于一个多通道的高速接口物理层,其可支持与多块计算芯片进行互联。

- 还没有人留言评论。精彩留言会获得点赞!