一种FLASH烧录系统的制作方法

一种flash烧录系统

技术领域

1.本实用新型涉及烧录系统,尤其涉及一种flash烧录系统。

背景技术:

2.传统芯片烧录方式有两种,一种是提前在smt前将程序烧录进芯片、另一种是smt后进行烧录。这两种烧录方式都离不开传统烧录工具-烧录编程器。目前现有的烧录器少则上百,多则上万,且烧录效率低下,而且还需要设计相应的工装治具配合烧录,而工装治具随着多次生产经常会出现接触不良,损坏。常见的烧录工具多为串口烧录器,而速率115200的uart串口的速率只有115kbps,另外还受到物理链路层的限制,限制烧写速率,严重影响产线生产效率。这样不仅导致生产成本过高,大大降低了生产效率,增加了产品制作周期。

3.因此,如何提供一种flash烧录工具,以提高烧录效率,降低成本,是本领域技术人员所亟待解决的技术问题。

技术实现要素:

4.为了解决现有技术中的问题,本实用新型提供了一种flash烧录系统。

5.本实用新型提供了一种flash烧录系统,包括flash烧录工具和设备产品终端,所述flash烧录工具通过spi接口与所述设备产品终端连接,所述flash烧录工具包括spi flash电路和第一连接器,所述设备产品终端包括第二连接器、mcu和nada flash,所述spi flash电路与所述第一连接器连接,所述第一连接器通过spi接口与所述第二连接器连接,所述第二连接器与所述mcu连接,所述mcu与所述nada flash连接,具有简易、低成本、快速烧录的优点。

6.作为本实用新型的进一步改进,所述设备产品终端还包括指示灯,所述mcu与所述指示灯连接。

7.作为本实用新型的进一步改进,所述spi flash电路包括nor flash芯片u1、上拉电阻r2、上拉电阻r3、上拉电阻r4、滤波电容c1和滤波电容c2,其中,所述滤波电容c1的一端接电源vp33,另一端与所述nor flash芯片u1的引脚4连接,所述nor flash芯片u1的引脚4接地,所述滤波电容c2与所述滤波电容c1并联,所述上拉电阻r2的一端接电源vp33,另一端与所述nor flash芯片u1的引脚7连接,所述上拉电阻r3的一端接电源vp33,另一端与所述nor flash芯片u1的引脚3连接,所述上拉电阻r4的一端接电源vp33,另一端与所述nor flash芯片u1的引脚1连接。

8.作为本实用新型的进一步改进,所述第一连接器包括接口j1,所述nor flash芯片u1的引脚1与所述接口j1的引脚4连接,所述nor flash芯片u1的引脚2与所述接口j1的引脚1连接,所述nor flash芯片u1的引脚6与所述接口j1的引脚3连接,所述nor flash芯片u1的引脚5与所述接口j1的引脚2连接。

9.作为本实用新型的进一步改进,所述第一连接器还包括开关k1,所述开关k1的一端与所述接口j1的引脚5连接,另一端接地。

10.作为本实用新型的进一步改进,所述接口j1的引脚5连接有上拉电阻r1。

11.作为本实用新型的进一步改进,所述nor flash芯片u1的型号为w25q128jvsiq。

12.作为本实用新型的进一步改进,所述mcu包括芯片uc1,所述芯片uc1的型号为nuc980dk61yc。

13.作为本实用新型的进一步改进,所述nada flash包括芯片und1,所述芯片und1的型号为s34ml02g200tfi000。

14.作为本实用新型的进一步改进,所述第二连接器包括接口jc3,所述接口jc3的引脚5连接有下拉电阻rc7,所述下拉电阻rc7的另一端接地。

15.本实用新型的有益效果是:提高了烧录效率,降低了成本。

附图说明

16.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的方案。

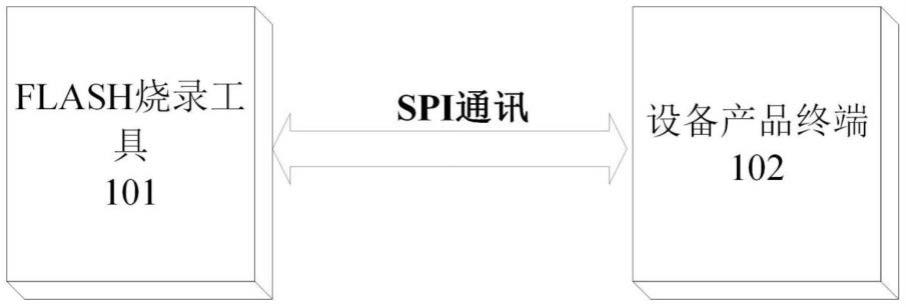

17.图1是本实用新型一种flash烧录系统的示意图。

18.图2是本实用新型一种flash烧录系统的内部结构示意图。

19.图3是本实用新型一种flash烧录系统的spi flash电路图。

20.图4是本实用新型一种flash烧录系统的第一连接器的电路图。

21.图5是本实用新型一种flash烧录系统的芯片uc1的电路图。

22.图6是本实用新型一种flash烧录系统的芯片und1的电路图。

23.图7是本实用新型一种flash烧录系统的第二连接器的电路图。

具体实施方式

24.需要说明的是,在不冲突的情况下,本实用新型中的实施例及实施例中的特征可以相互组合。

25.在本实用新型的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型保护范围的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本实用新型的描述中,除非另有说明,“多个”的含义是两个或两个以上。

26.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本实用新型中的具体含义。

27.下面结合附图说明及具体实施方式对本实用新型作进一步说明。

28.如图1至图7所示,一种flash烧录系统,flash为存储器,又称闪存,包括flash烧录工具101和设备产品终端102,所述flash烧录工具101通过spi接口103与所述设备产品终端102连接,所述flash烧录工具101包括spi flash电路1和第一连接器2,所述设备产品终端102包括第二连接器3、mcu 4和nada flash 5,所述spi flash电路1与所述第一连接器2连接,所述第一连接器2通过spi接口103与所述第二连接器3连接,所述第二连接器3与所述mcu 4连接,所述mcu 4与所述nada flash 5连接。

29.所述设备产品终端102还包括指示灯6,所述mcu 4与所述指示灯6连接。

30.所述spi flash电路包括nor flash芯片u1、上拉电阻r2、上拉电阻r3、上拉电阻r4、滤波电容c1和滤波电容c2,其中,所述滤波电容c1的一端接电源vp33,另一端与所述nor flash芯片u1的引脚4连接,所述nor flash芯片u1的引脚4接地,所述滤波电容c2与所述滤波电容c1并联,所述上拉电阻r2的一端接电源vp33,另一端与所述nor flash芯片u1的引脚7连接,所述上拉电阻r3的一端接电源vp33,另一端与所述nor flash芯片u1的引脚3连接,所述上拉电阻r4的一端接电源vp33,另一端与所述nor flash芯片u1的引脚1连接。

31.所第一连接器包括接口j1,所述nor flash芯片u1的引脚1与所述接口j1的引脚4连接,所述nor flash芯片u1的引脚2与所述接口j1的引脚1连接,所述nor flash芯片u1的引脚6与所述接口j1的引脚3连接,所述nor flash芯片u1的引脚5与所述接口j1的引脚2连接。

32.所述第一连接器还包括开关k1,所述开关k1的一端与所述接口j1的引脚5连接,另一端接地。

33.所述接口j1的引脚5连接有上拉电阻r1。

34.所述nor flash芯片u1的型号为w25q128jvsiq。

35.如图3所示,u1是烧录工具装置的一颗128m-bit的nor flash,主要用于存储产品所需烧录目标程序。/cs引脚1为片选,从设备选择。这是一个可选的引脚,用来选择主/从设备。它的功能是用来作为“片选引脚”,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。当/cs = 1时,该芯片设备不被选中,4个数据引脚为高阻态,此时设备功耗在临界水平。当cs = 0时,芯片被选中,可以对芯片读写,在读写指令之前,片选信号要从高电平变为低电平。/wp引脚3为写保护,当/wp 为低时,写保护信号有效,芯片可以在硬件上保护起来,此时无法给芯片写入数据。/hold引脚7接收到低电平时,且/cs=0,数据引脚为高阻态,芯片可以屏蔽总线的数据和时钟信号,当/hold为高电平时,可以继续恢复对芯片的操作。clk引脚6为时钟信号,作为主设备的输入,从设备的输入;so引脚2为主设备输入/从设备输出,so在从模式下发送数据,在主模式下接收数据;si引脚5为主设备输出/从设备输入,si在主模式下发送数据,在从模式下接收数据;其中r2、r3、r4为上拉电阻,c1、c2为nor flash供电引脚的滤波电容。

36.如图4所示,j1作为flash烧录工具与设备终端连接的烧录插针,其为设备终端提供spi通讯接口信号,其中r1作为上拉电阻,k1为开关,只要用于模式状态选择。

37.所述mcu包括芯片uc1,所述芯片uc1的型号为nuc980dk61yc。

38.如图5所示,uc1是设备终端的mcu控制器核心单元,主要负责设备终端各路管理单元及控制,其中mcu控制器采用了采用新塘nuc980dk61yc芯片,该cpu采用arm926ej-s 核

心,执行速度高达 300 mhz,内建 64 mb ddr ii 内存;外围集成1gb flash存储器、以太网等外设接口,采用基于自主可控操作linux系统。实现对交流模拟量信号采集功能,开关状态量信号采集功能,开关控制输出功能,本地和远程通信功能。

39.所述nada flash包括芯片und1,所述芯片und1的型号为s34ml02g200tfi000。

40.如图6所示,und1采用了一个大容量、高速存储的nada flash,其容量可达1gbit(128m x 8bit),主要用于存终端程序及存储各类终端抄读数据,其中i/o0~i/o7(引脚29-44)是nada flash的数据线与mcu连接,主要用来传输命令/地址、数据,仅在读操作的时候用来输出数据。cle引脚16为命令锁存使能,当cle为高时,在we#上升沿,命令通过i/o[7:0]锁存到命令寄存器,当不传输命令时,cle为低。ale引脚17为地址锁存使能,当ale为高时,在we#下降沿,地址信息通过i/o[7:0]锁存片内的地址寄存器。如果传输的不是地址信息,ale为低。ce引脚9为片选,一旦器件进入program或erase操作,ce可以变无效。re引脚8为读使能,在读取数据前,先使得ce有效。we引脚18为写使能,在写取数据前,先使得we有效,在we#上升沿命令/地址/数据锁存。wp引脚19为写保护,当wp为低时,所有的program和erase都被禁止。r/b引脚7为准备/忙状态,在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成。其中rnd1、rnd2、rnd3为上拉电阻,cnd1、cnd2、cnd3为nada flash供电引脚的滤波电容。

[0041]

所述第二连接器包括接口jc3,所述接口jc3的引脚5连接有下拉电阻rc7,所述下拉电阻rc7的另一端接地。

[0042]

如图7所示,jc3作为设备终端与flash烧录工具连接的烧录插座,其为flash烧录工具提供电源及spi通讯接口信号,其中rc7作为下拉电阻,只要用于设备终端启动模式状态。

[0043]

本实用新型提供的一种flash烧录系统,将flash烧录工具101插入设备产品终端102,设备产品终端102检测到spi模式后,通过spi通讯协议接口,将flash烧录工具101的程序烧录到设备产品终端102中的nada flash 5,即完成烧写;当flash烧录工具101插入设备产品终端102的第二连接器3后,设备产品终端102给flash烧录工具101提供了电源,同时,设备产品终端102启动模式检测到spi模式后,将flash烧录工具101的程序通过spi通讯传送到nada flash 5,通过设备产品终端102的指示灯6判断是否烧录成功。

[0044]

本实用新型提供的一种flash烧录系统,提供了一种flash烧录工具,这种工具与传统烧录器不同在于,无需外加电源适配器、也无需工装治具,而这个烧录工具成本仅仅只需几块钱,而且通过spi的接口进行烧写,目前spi协议最高的速率大于50mbps,相对于串口115kbps速率,可以看出串口烧录工具效率低,而串口烧录工具还需要考虑到兼容性问题,改进后的flash烧录工具只需通过插针连接方式插入产品接口即完成烧录,实现即插即烧的方式。本实用新型通过一个flash烧录工具插入产品设备进行烧录,大大的提高的使用上的方便性和烧录效率。而且烧录设置了产品设备的监测,提供了检验烧录效果。降低生产成本,提高了生产效率。

[0045]

以上内容是结合具体的优选实施方式对本实用新型所作的进一步详细说明,不能认定本实用新型的具体实施只局限于这些说明。对于本实用新型所属技术领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1