用于管芯到管芯互连的边带接口的制作方法

背景技术:

1、多芯片封装(multi-chip packaging,mcp)的进步使得性能增长和复杂产品的创造成为可能。针对短距离优化的高密度、低延时管芯到管芯互连能够实现高数据速率和很低的误码率(bit error rate,ber)。这种封装内的管芯到管芯链路可以寻求实现与封装迹线传输、链路状态机和链路状态转换相关的同步。用于交换此信息的机制用于执行连接设备的启动和操作。虽然可以通过主带传送该信息,但是这种通信减少了总带宽。

技术实现思路

技术特征:

1.一种装置,包括:

2.根据权利要求1所述的装置,其中,所述物理层电路装置用于:

3.根据权利要求2所述的装置,其中,在所述边带初始化期间,所述物理层电路装置用于禁用主带接口。

4.根据权利要求1所述的装置,其中,所述第二边带数据通道和所述第二边带时钟通道包括冗余边带对。

5.根据权利要求1所述的装置,其中,所述物理层电路装置用于:接收包括工作分配的边带消息,并且响应于所述工作分配而分配冗余边带通道作为所述工作边带的一部分。

6.根据权利要求1-5中任一项所述的装置,还包括封装,所述封装包括所述第一管芯和所述第二管芯,其中,所述互连包括用于耦合所述第一管芯和所述第二管芯的封装上互连。

7.根据权利要求6所述的装置,还包括封装衬底,所述封装衬底包括适配在硅桥内的所述封装上互连。

8.根据权利要求6所述的装置,还包括中介层,所述中介层包括所述封装上互连。

9.根据权利要求1-8中任一项所述的装置,其中,所述互连包括具有通用小芯片快速互连(ucie)架构的具有多协议能力的互连,所述第一互连协议包括外围组件快速互连(pcie)协议的flit模式,并且所述互连进一步用于传送第二互连协议的第二信息,所述第二互连协议包括计算快速链路(cxl)协议的flit模式。

10.一种方法,包括:

11.根据权利要求10所述的方法,还包括:

12.根据权利要求11所述的方法,还包括:基于所述第一结果具有所述第一值:

13.根据权利要求10所述的方法,其中,所述第一边带数据通道和所述第二边带数据通道中的另一个以及所述第一边带时钟通道和所述第二边带时钟通道中的另一个包括冗余边带对。

14.根据权利要求10所述的方法,还包括:

15.根据权利要求14所述的方法,其中,发送所述多次迭代包括:

16.根据权利要求14所述的方法,还包括:在检测到所述预定模式之后,停止发送边带初始化分组的所述多次迭代。

17.一种计算机可读存储介质,包括计算机可读指令,所述计算机可读指令在被执行时用于实现根据权利要求10至16中任一项所述的方法。

18.一种装置,包括用于执行根据权利要求10至16中任一项所述的方法的单元。

19.一种封装,包括:

20.根据权利要求19所述的封装,其中,在所述边带初始化期间,所述物理层电路装置用于:

21.根据权利要求19所述的封装,其中,所述物理层电路装置用于在所述第一管芯的复位流程之后执行所述边带初始化,所述第一管芯的复位流程独立于所述第二管芯的复位流程。

22.根据权利要求19所述的封装,其中,所述第二管芯包括加速器,其中,所述第一管芯用于根据外围组件快速互连(pcie)协议的flit模式或计算快速链路(cxl)协议的flit模式中的至少一个与所述第二管芯进行通信。

23.一种装置,包括:

24.根据权利要求23所述的装置,还包括:

25.根据权利要求23-24中任一项所述的装置,还包括:

技术总结

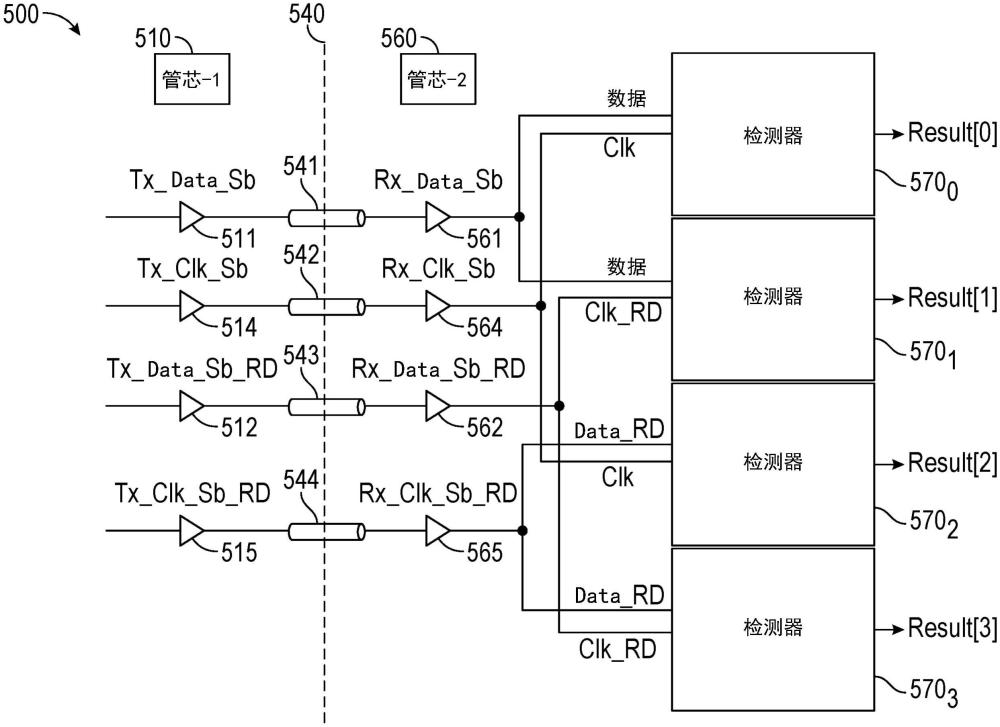

在一个实施例中,一种装置包括:管芯到管芯适配器,用于与协议层电路装置和物理层电路装置进行通信;以及物理层电路装置,耦合到管芯到管芯适配器,其中物理层电路装置用于接收第一信息并经由互连将第一信息输出到第二管芯。物理层电路装置可以包括:第一边带数据接收器,用于耦合到第一边带数据通道;以及第一边带时钟接收器,用于耦合到第一边带时钟通道;以及第二边带数据接收器,用于耦合到第二边带数据通道,以及第二边带时钟接收器,用于耦合到第二边带时钟通道。物理层电路装置可以分配工作边带,该工作边带包括:第一或第二边带数据通道中的一个;以及第一或第二边带时钟通道中的一个。描述并要求保护了其他实施例。

技术研发人员:N·兰卡,S·乔德里,D·达斯夏尔马,L·塞莎恩,Z·吴,G·帕斯达斯特

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!