基于PCIe的数据传输方法和装置与流程

本技术涉及数据传输,更具体地,涉及一种基于外围组件互连快件(peripheral component interconnect express,pcie)的数据传输方法和装置。

背景技术:

1、pcie作为第三代总线技术规范,它具备高带宽、低延时、灵活扩展、支持热插拔、错误处理和错误报告等特点,因此pcie总线被广泛地用于实现外设之间以及外设与主机之间的高速数据传输。

2、然而,当基于pcie总线传输数据量大的包时,虽然传输带宽接近原始带宽,但传输时延大;传输小数据量的数据时,传输带宽低,并且同时存在频繁响应中断信号和初始化直接内存访问(direct memory access,dma)控制器的现象,这导致cpu开销增大。

3、因此,如何进一步提高基于pcie的数据传输性能是亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种能够在提高基于pcie的数据传输性能的同时,降低实施成本的基于pcie的数据传输方法和装置。所述方法和装置通过以轮询的方式通知dma控制器从根复合体(root complex,rc)的内存中读取数据,并以轮询方式确定rc的内存中是否存在dma控制器写入的数据来提高基于pcie的数据传输性能。

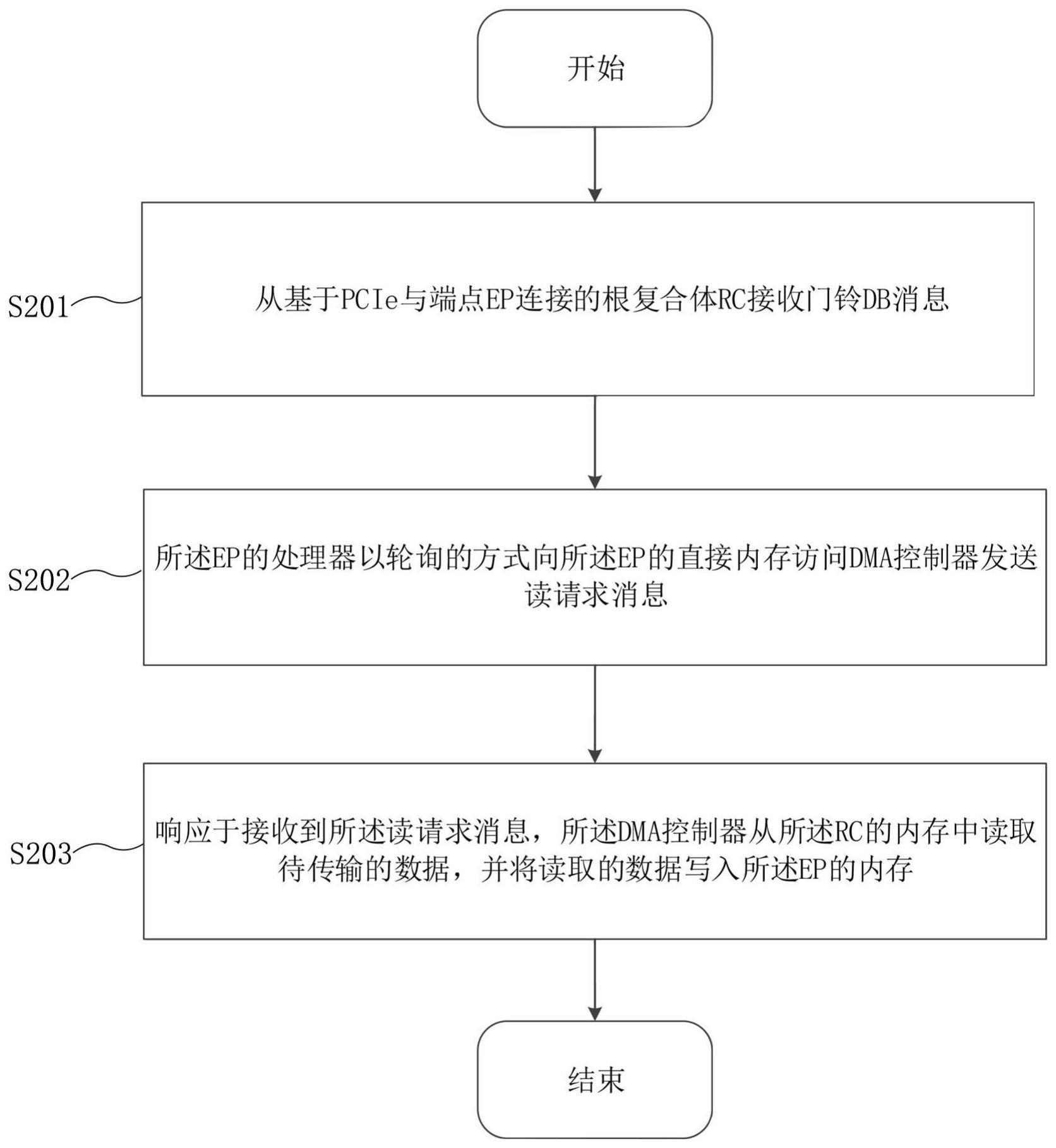

2、根据本公开的示例性实施例的一方面,提供了一种基于外围组件互连高速pcie的数据传输方法,包括:从基于pcie与端点(endpoint,ep)连接的根复合体rc接收门铃db消息;所述ep的处理器以轮询的方式向所述ep的直接内存访问dma控制器发送读请求消息;响应于接收到所述读请求消息,所述dma控制器从所述rc的内存中读取待传输的数据,并将读取的数据写入所述ep的内存。

3、根据本公开的实施例,当接收到db消息时,ep的处理器即轮询通知dma控制器从rc的内存中读取数据,这样,即便有db消息丢失,由于dma控制器被轮询通知从rc端的内存中读取数据,因此,与丢失的db消息相应的数据也会被dma控制器读取到,从而避免了数据丢失。另外,由于dma控制器被轮询通知从rc端的内存中读取数据,这样避免了dma控制器的频繁初始化,同时也不用频繁去响应后续的db消息,因为处理器在轮询通知dma控制器读取rc的内存中的数据,即便不响应后续db消息,与后续db消息相应的数据也会被dma控制器读取,这减少了频繁中断上下文切换带来的处理器额外开销和占用率,降低了数据传输的延迟。

4、可选地,所述方法还包括:当确定所述rc的内存中不再存在所述待传输的数据时,所述ep的处理器停止向所述dma控制器发送读请求消息。

5、可选地,所述方法还包括:当从所述rc的内存中读取的数据中包括数据结束符时,所述ep的处理器确定所述rc的内存中不再存在所述待传输的数据。

6、根据本公开的实施例,当从rc的内存读取到数据结束符时,说明书rc内存中已经不存在待传输的数据,因此可以停止向所述dma控制器发送读请求消息,从而避免不必要的轮询发送读请求消息的操作。

7、可选地,所述ep的处理器在可缓存模式下运行,所述方法还包括:响应于读取的数据被写入所述ep的内存,所述ep的处理器将所述ep的处理器的第一缓存中的数据置为无效后,将所述读取的数据从所述ep的内存写入所述第一缓存;和\或响应于接收到发送数据的请求,所述ep的处理器将待发送的数据写入所述ep的处理器的第二缓存;所述ep的处理器将所述待发送的数据从所述第二缓存刷入所述ep的内存;所述dma控制器将所述待发送的数据从所述ep的内存写入所述rc的内存。

8、根据本公开的实施例,在将ep的内存中的数据写入ep的缓存之前,将ep的缓存中的数据置无效,可以保证从ep的缓存中获取到的数据是来自ep的内存中的最新数据。另外,在发送数据时,将ep的处理器的第二缓存中的数据刷入ep的内存,可以保证第二缓存中的数据被写入到rc的内存中。

9、可选地,所述方法还包括:在将待发送的数据写入所述ep的缓存后,所述ep的处理器将数据结束符写入所述ep的处理器的第二缓存,以及将所述数据结束符从所述第二缓存刷入所述ep的内存。

10、根据本公开的实施例,由于第二缓存中的数据会被传输到rc的内存,因此通过将数据结束符写入第二缓存,这样rc的处理器从rc的内存中读取数据时,当读取到该数据结束符时,可确定rc的内存中不再存在数据,从而停止从rc的内存中读取数据。

11、可选地,所述dma控制器从所述rc的内存中读取数据的步骤包括:所述dma控制器以预设长度读取所述rc的内存中的数据包;其中,所述方法还包括:确定读取的数据包的计数是否是预定数量的整数倍,如果读取的数据包的计数是预定数量的整数倍,确定所述预设长度是否大于最近读取的预定数量的数据包中的具有最大长度的数据包的长度,当确定所述预设长度大于读取的预定数量的数据包中的具有最大长度的数据包的长度时,将所述预定长度更新为所述最大长度,如果读取的数据包的计数不是预定数值的整数倍,由所述ep的处理器基于读取的所述数据包的数据确定所述数据包的数据长度是否大于预设长度,当确定所述数据包的数据长度大于所述预设长度时,将所述预设长度更新为所述数据包的数据长度,以及当确定所述数据包的数据长度大于所述预设长度时,所述dma控制器以所述数据包的数据长度重新读取所述数据包。

12、根据本公开的实施例,通过更新预设长度,可以提高读取数据的效率。

13、根据本公开的实施例的另一方面,提供了一种基于外围组件互连高速pcie的数据传输方法,包括:接收从基于pcie与根复合体rc连接的端点ep发送的消息信号中断msi消息;所述rc的处理器以轮询的方式读取所述rc的内存中的数据,其中,所述rc的内存中的数据由所述ep的直接内存访问dma控制器写入。

14、根据本公开的实施例,由于rc的处理器响应于msi消息以轮询的方式从rc的内存中读取数据,这可以避免即便msi消息丢失,与该msi消息相应的数据也会被rc的处理器读取。另外,由于处理器轮询读取rc的内存中的数据,因此,可以不用频繁响应后续的msi消息,从而节省处理器开销,提高数据传输性能。

15、可选地,所述方法还包括:当确定所述rc的内存中不再存在数据时,所述rc的处理器停止以轮询的方式读取数据。

16、可选地,所述方法还可包括:当所述rc的处理器从所述rc的内存中读取的数据包括数据结束符时,所述rc的处理器确定所述rc的内存中不再存在数据。

17、可选地,所述rc的处理器在可缓存模式下运行,所述方法还包括:响应于以轮询的方式读取所述rc的内存中的数据,所述rc的处理器将rc的处理器的第三缓存中的数据置为无效后,将所述读取的数据写入所述第三缓存中;和\或响应于接收到发送数据的请求,所述rc的处理器将待发送的数据写入所述rc的处理器的第四缓存中;所述rc的处理器将所述待发送的数据从所述rc的第四缓存刷入所述rc的内存;所述rc的处理器向所述ep发送门铃db消息。

18、根据本公开的实施例,在将rc的内存中的数据写入rc的第三缓存之前,将rc的第三缓存中的数据置无效,可以保证从rc的第三缓存中获取到的数据是来自rc的内存的最新数据。另外,在发送数据时,将rc的处理器的第四缓存中的数据输入rc的内存,可以保证第四缓存中的数据能够被写入到ep的内存中。

19、可选地,所述方法还包括:在将所述数据写入所述rc的第四缓存后,所述rc的处理器将数据结束符写入所述rc的第四缓存,以及将所述数据结束符从所述第四缓存刷入rc的内存。

20、根据本公开的实施例,由于第四缓存中的数据会被传输到rc的内存,因此通过将数据结束符写入第四缓存,这样dma从rc的内存中读取数据时,当读取到该数据结束符时,可确定rc的内存中不再存在数据,此时dma而停止从rc的内存中读取数据。

21、根据本公开的实施例的另一方面,提供了一种端点ep,所述ep基于外围组件互连高速pcie与根复合体rc连接,其中,所述ep包括:接收单元,被配置为从基于pcie与端点ep连接的根复合体rc接收门铃db消息;处理器,被配置为以轮询的方式向所述ep的直接内存访问dma控制器发送读请求消息;所述dma控制器,被配置为响应于接收到所述读请求消息,从所述rc的内存中读取待传输的数据,并将读取的数据写入所述ep的内存。

22、可选地,所述处理器还被配置为:当确定所述rc的内存中不再存在所述待传输的数据时,停止向所述dma控制器发送读请求消息。

23、可选地,所述处理器还被配置为:当从所述rc的内存中读取的数据中包括数据结束符时,确定所述rc的内存中不再存在所述待传输的数据。

24、可选地,所述处理器在可缓存模式下运行,所述处理器还被配置为:响应于读取的数据被写入所述ep的内存,将所述处理器的第一缓存中的数据置为无效后,将所述读取的数据从所述ep的内存写入所述第一缓存;和\或响应于接收到发送数据的请求,将待发送的数据写入所述处理器的第二缓存,将所述待发送的数据从所述第二缓存刷入所述ep的内存,以及其中,所述dma控制器还被配置为:将所述待发送的数据从所述ep的内存写入所述rc的内存。

25、可选地,所述处理器还被配置为:在将待发送的数据写入所述ep的处理器的第二缓存后,将数据结束符写入所述ep的处理器的第二缓存,以及将所述数据结束符从所述第二缓存输入所述ep的内存。

26、可选地,所述dma控制器被配置为:以预设长度读取所述rc的内存中的数据包;以及其中,所述处理器还被配置为:确定读取的数据包的计数是否是预定数量的整数倍,如果读取的数据包的计数是预定数量的整数倍,确定所述预设长度是否大于最近读取的预定数量的数据包中的具有最大长度的数据包的长度,当确定所述预设长度大于读取的预定数量的数据包中的具有最大长度的数据包的长度时,将所述预定长度更新为所述最大长度,如果读取的数据包的计数不是预定数值的整数倍,基于读取的所述数据包的数据确定所述数据包的数据长度是否大于预设长度,当确定所述数据包的数据长度大于所述预设长度时,将所述预设长度更新为所述数据包的数据长度,以及其中,所述dma控制器还被配置为:当确定所述数据包的数据长度大于所述预设长度时,以所述数据包的数据长度重新读取所述数据包。

27、根据本公开的实施例的另一方面,提供了一种根复合体rc,所述rc基于外围组件互连高速pcie与端点ep连接,其中,所述rc包括:接收单元,被配置为:接收从所述ep发送的消息信号中断msi消息;处理器,被配置为以轮询的方式读取所述rc的内存中的数据,其中,所述rc的内存中的数据由所述ep的直接内存访问dma控制器写入。

28、可选地,所述处理器还被配置为:当确定所述rc的内存中不再存在数据时,停止以轮询的方式读取数据。

29、可选地,所述处理器在可缓存模式下运行,所述处理器还被配置为:响应于以轮询的方式读取所述rc的内存中的数据,将rc的处理器的第三缓存中的数据置为无效后,将所述读取的数据写入所述第三缓存中;和\或响应于接收到发送数据的请求,将待发送的数据写入所述rc的处理器的第四缓存中;将所述待发送的数据从所述rc的第四缓存刷入所述rc的内存;以及向所述ep发送门铃db消息。

30、可选地,所述处理器还被配置为:在将所述数据写入所述rc的第四缓存后,将数据结束符写入所述rc的第四缓存,以及将所述数据结束符从所述第四缓存刷入所述rc的内存。

31、可选地,所述处理器还被配置为:当所述rc的处理器从所述rc的内存中读取的数据包括数据结束符时,确定所述rc的内存中不再存在数据。

32、根据本公开的实施例的另一方面,提供了一种一种存储有计算机程序的非暂时性计算机可读存储介质,其中,当所述计算机程序被处理器执行时使得所述处理器执行如上所述的基于pcie的数据传输方法。

33、根据本公开的实施例的另一方面,提供了一种电子装置,包括:处理器;存储器,存储有计算机程序,当所述计算机程序被处理器执行时,使得所述处理器执行如上所述的基于pcie的数据传输方法。

- 还没有人留言评论。精彩留言会获得点赞!