一种神经网络处理器的时间成本计算方法、系统及可读存储介质与流程

本发明涉及模拟器领域,具体涉及一种神经网络处理器的时间成本计算方法、系统及可读存储介质。

背景技术:

1、构架编译器的框架系统在神经网络处理器的矢量单元上的性能数据是指导性能调优的关键。芯片设计师基于性能数据暴露的架构缺陷进行架构调优,使得构架编译器的框架系统具有更高效的处理能力。然而,在成品芯片上采集获得的神经网络处理器的矢量单元上的性能数据存在滞后性,无法指导芯片设计阶段对架构的优化。在设计阶段,即没有成品芯片的情况下针对复杂的神经网络处理器的矢量单元的工作流程进行模拟,并获得准确的神经网络处理器的矢量单元性能数据,尤其是性能数据中的时间成本,是制约神经网络处理器架构设计性能优化的关键因素。

技术实现思路

1、为解决现有技术难以针对神经网络处理器的矢量单元复杂工作流程获得准确的性能数据的技术问题,本发明提出一种神经网络处理器的时间成本计算方法、系统和可读存储介质,实现在芯片设计阶段获取准确的性能数据以指导芯片架构优化的效果。

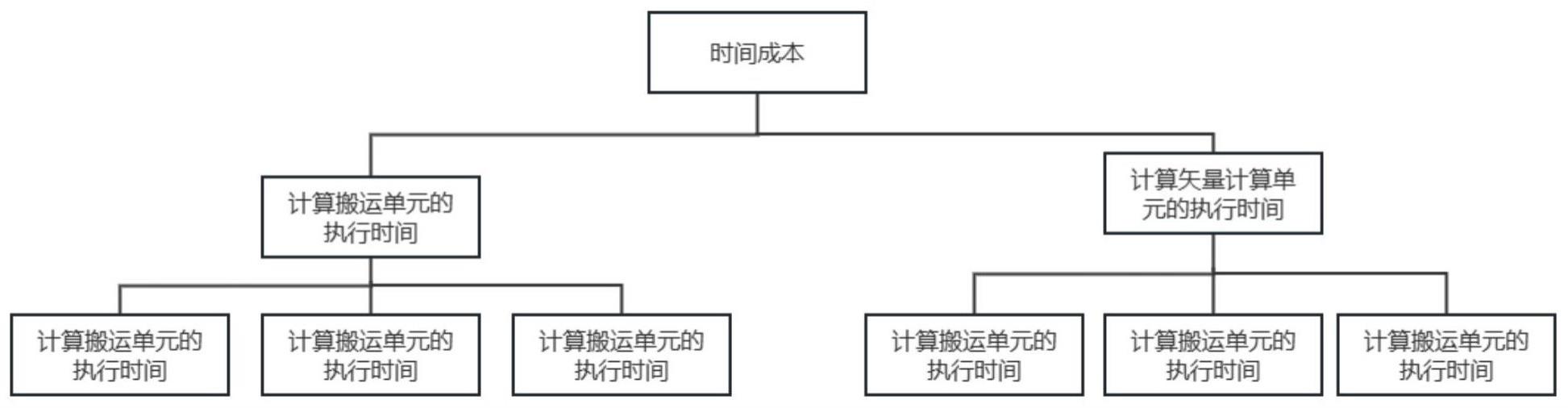

2、本发明提供一种神经网络处理器的时间成本计算方法,所述神经网络处理器的时间成本计算方法基于行为级模拟器,计算搬运单元的执行时间,及,矢量计算单元的执行时间;

3、所述计算搬运单元的执行时间包括:搬运单元执行搬运时间,搬运单元更新时间,搬运单元发出解除等待指令时间;

4、所述矢量计算单元的执行时间包括:矢量计算单元执行计算时间,矢量计算单元更新时间,矢量计算单元发出解除等待指令时间;

5、其中,所述计算搬运单元的执行时间与计算所述矢量计算单元的执行时间为并行执行。

6、优选的,基于所述搬运单元处于执行搬运状态计算所述搬运单元执行搬运时间,所述搬运单元处于执行搬运状态的时间成本计算包括:将搬运单元执行当前搬运所需的周期数推送至用于保存搬运完成时刻点的缓存的末尾,作为当前搬运的结束时刻。

7、优选的,基于所述搬运单元处于更新状态计算所述搬运单元更新时间,所述搬运单元处于更新状态为:

8、所述搬运单元未开始搬运或搬运完成,且,所述搬运单元当前没有搬运指令配置,且所述搬运单元至少已完成一次搬运;

9、或,所述搬运单元收到来自所述矢量计算单元或来自与所述搬运单元搬运数据相反方向的其他搬运单元发出的解除等待指令。

10、优选的,所述搬运单元处于更新状态的时间成本计算包括:更新用于保存搬运完成时刻点的缓存的头部的值至用于统计搬运执行时间的寄存器,并删除用于保存搬运完成时刻点的缓存的头部的值。

11、优选的,基于所述搬运单元处于发出解除等待指令状态计算所述搬运单元发出解除等待指令状态时间,所述搬运单元处于发出解除等待指令状态的时间成本计算包括:保存所述搬运单元发出解除等待指令的真实周期数至用于存储所述执行单元握手所需数据的缓存。

12、优选的,基于所述矢量计算单元处于更新状态计算所述矢量计算单元更新时间,所述矢量计算单元处于更新状态的时间成本计算包括:将用于存储矢量计算单元与搬运单元握手所需数据的缓存中的数据,更新至用于统计执行时间的寄存器。

13、优选的,基于所述矢量计算单元处于解除等待指令状态计算所述矢量计算单元发出解除等待指令时间,所述矢量计算单元处于发出解除等待指令状态的时间成本计算包括:

14、当在矢量计算单元的流水线解析获得当前指令为发出解除等待指令,记录当前时刻的用于统计执行时间的寄存器的值。

15、优选的,所述搬运单元包括将芯片外数据搬运到芯片内存储的指令,及将芯片内的存储数据搬运到芯片外的指令。

16、本发明还提供一种神经网络处理器的时间成本计算系统,包括:

17、行为级模拟器,

18、用于计算搬运单元的执行时间的第一时间成本计算单元,

19、用于计算矢量计算单元的执行时间的第二时间成本计算单元;

20、所述第一时间成本计算单元被配置为执行计算搬运单元执行搬运时间,搬运单元更新时间,搬运单元发出解除等待指令时间;

21、所述第二时间成本计算单元被配置为执行计算矢量计算单元执行计算时间,矢量计算单元更新时间,矢量计算单元发出解除等待指令时间;

22、其中,所述第一时间成本计算单元和所述第二时间成本计算单元为并行执行。

23、本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现如前述的方法。

24、本发明实施方式相对于现有技术而言,本发明提供的神经网络处理器的时间成本计算方法、系统和可读存储介质,利用行为级模拟器,在芯片设计阶段就并行执行多个指令,以分别计算不同指令类型的指令的执行时间,在行为级模拟器上就获得准确的、与对应指令在芯片上执行时间相同的时间成本,实现了在芯片设计阶段准确获得芯片性能参数,以为芯片设计师在设计阶段基于以时间成本为主的性能数据暴露的架构缺陷进行架构调优提供数据基础。

25、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:

1.一种神经网络处理器的时间成本计算方法,其特征在于,基于行为级模拟器,计算搬运单元的执行时间,及,矢量计算单元的执行时间;

2.根据权利要求1所述的神经网络处理器的时间成本计算方法,其特征在于,基于所述搬运单元处于执行搬运状态计算所述搬运单元执行搬运时间,所述搬运单元处于执行搬运状态的时间成本计算包括:将搬运单元执行当前搬运所需的周期数推送至用于保存搬运完成时刻点的缓存的末尾,作为当前搬运的结束时刻。

3.根据权利要求1所述的神经网络处理器的时间成本计算方法,其特征在于,基于所述搬运单元处于更新状态计算所述搬运单元更新时间,所述搬运单元处于更新状态为:

4.根据权利要求3所述的神经网络处理器的时间成本计算方法,其特征在于,所述搬运单元处于更新状态的时间成本计算包括:更新用于保存搬运完成时刻点的缓存的头部的值至用于统计搬运执行时间的寄存器,并删除用于保存搬运完成时刻点的缓存的头部的值。

5.根据权利要求1所述的神经网络处理器的时间成本计算方法,其特征在于,基于所述搬运单元处于发出解除等待指令状态计算所述搬运单元发出解除等待指令状态时间,所述搬运单元处于发出解除等待指令状态的时间成本计算包括:保存所述搬运单元发出解除等待指令的真实周期数至用于存储所述执行单元握手所需数据的缓存。

6.根据权利要求1所述的神经网络处理器的时间成本计算方法,其特征在于,基于所述矢量计算单元处于更新状态计算所述矢量计算单元更新时间,所述矢量计算单元处于更新状态的时间成本计算包括:将用于存储矢量计算单元与搬运单元握手所需数据的缓存中的数据,更新至用于统计执行时间的寄存器。

7.根据权利要求1所述的神经网络处理器的时间成本计算方法,其特征在于,基于所述矢量计算单元处于解除等待指令状态计算所述矢量计算单元发出解除等待指令时间,所述矢量计算单元处于发出解除等待指令状态的时间成本计算包括:

8.根据权利要求1-7任一所述的神经网络处理器的时间成本计算方法,其特征在于,所述搬运单元包括将芯片外数据搬运到芯片内存储的指令,及将芯片内的存储数据搬运到芯片外的指令。

9.一种神经网络处理器的时间成本计算系统,其特征在于,包括:

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,

技术总结

本发明涉及一种神经网络处理器的时间成本计算方法、系统及可读存储介质,基于行为级模拟器,计算搬运单元的执行时间,及,矢量计算单元的执行时间;所述计算搬运单元的执行时间包括:搬运单元执行搬运时间,搬运单元更新时间,搬运单元发出解除等待指令时间;所述矢量计算单元的执行时间包括:矢量计算单元执行计算时间,矢量计算单元更新时间,矢量计算单元发出解除等待指令时间;其中,所述计算搬运单元的执行时间与计算所述矢量计算单元的执行时间为并行执行。芯片设计阶段利用行为级模拟器获得指令与真实芯片上的执行时间相同的时间成本,获得了准确的性能数据,为芯片架构优化提供数据基础。

技术研发人员:王东

受保护的技术使用者:深圳云天励飞技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!