一种激励文件的生成方法及系统与流程

本文涉及集成电路测试技术,尤指一种激励文件的生成方法及系统。

背景技术:

1、激励文件用于产生模拟激励,在应用fpga进行数字系统设计时,通过将有效并切合实际的激励文件产生的模拟激励加入到数字系统设计中观察其响应,并将输出响应与期望值相比较能够对数字系统设计进行功能与时序的有效验证。

2、目前的激励文件主要通过用户根据设计手动编写其基本架构,随后根据观察结果不断修改各模块,得到最终的激励文件。

3、这种激励文件的生成方法完全依靠人工方式进行,生成难度较大,且花费时间较多,激励文件的生成效率十分低下。

技术实现思路

1、本申请提供了一种激励文件的生成方法及系统,能够自动生成激励文件,降低操作难度,减少了花费时间,提高激励文件的生成效率。

2、本申请提供了一种激励文件的生成方法,包括:

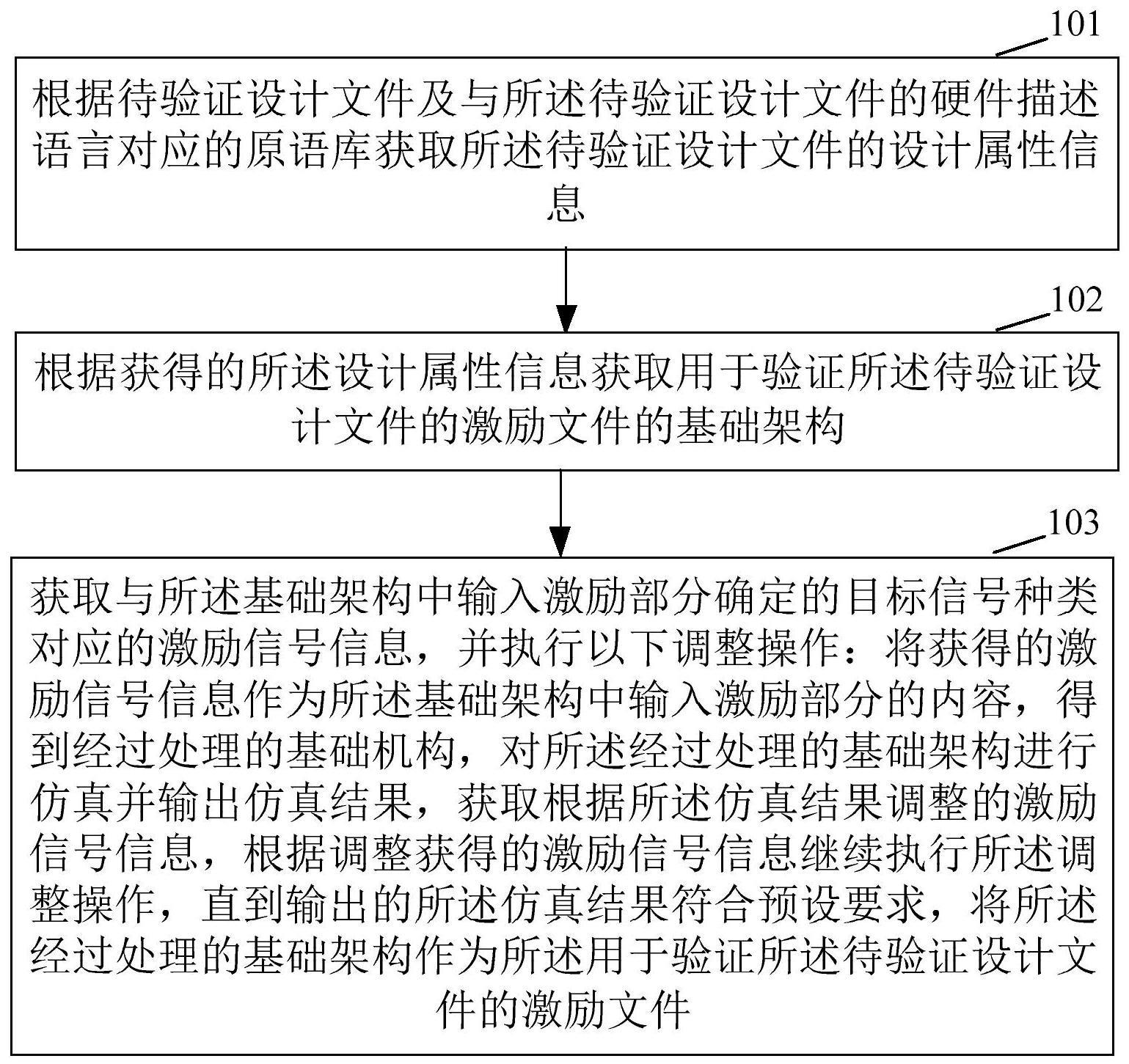

3、根据待验证设计文件及与所述待验证设计文件的硬件描述语言对应的原语库获取所述待验证设计文件的设计属性信息;

4、根据获得的所述设计属性信息获取用于验证所述待验证设计文件的激励文件的基础架构;

5、获取与所述基础架构中输入激励部分确定的目标信号种类对应的激励信号信息,并执行以下调整操作:将获得的激励信号信息作为所述基础架构中输入激励部分的内容,得到经过处理的基础架构,对所述经过处理的基础架构进行仿真并输出仿真结果,获取根据所述仿真结果调整的激励信号信息,根据调整获得的激励信号信息继续执行所述调整操作,直到输出的所述仿真结果符合预设要求,将所述经过处理的基础架构作为所述用于验证所述待验证设计文件的激励文件。

6、另一方面,本申请提供了一种激励文件的生成系统,包括:分析模块、架构模块和处理模块;

7、所述分析模块,用于根据待验证设计文件及与所述待验证设计文件的硬件描述语言对应的原语库获取所述待验证设计文件的设计属性信息;

8、所述架构模块,用于根据获得的所述设计属性信息获取用于验证所述待验证设计文件的激励文件的基础架构;

9、所述处理模块,用于取与所述基础架构中输入激励部分确定的目标信号种类对应的激励信号信息,并执行以下调整操作:将获得的激励信号信息作为所述基础架构中输入激励部分的内容,得到经过处理的基础架构,对所述经过处理的基础架构进行仿真并输出仿真结果,获取根据所述仿真结果调整的激励信号信息,根据调整获得的激励信号信息继续执行所述调整操作,直到输出的所述仿真结果符合预设要求,将所述经过处理的基础架构作为所述用于验证所述待验证设计文件的激励文件。

10、与相关技术相比,本申请包括自动生成激励文件的基础架构,并通过获取不断调整的激励信号信息调整基础架构中输入激励部分的内容,最终生成用于验证所述待验证设计文件的激励文件,从而实现了激励文件的自动生成,降低了激励文件的生成难度,减少了激励文件的生成时间,极大程度地提高了激励文件的生成效率。

11、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

技术特征:

1.一种激励文件的生成方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述设计属性信息包括:所述待验证设计文件的输入输出端口、所述待验证设计文件所要实现的功能和所述待验证设计文件对应原语的实现逻辑;

3.根据权利要求2所述的方法,其特征在于,所述根据获得的所述设计属性信息获取用于验证所述待验证设计文件的激励文件的基础架构,包括:

4.根据权利要求1所述的方法,其特征在于,与所述目标信号种类对应的激励信号信息包括:与所述目标信号种类对应的激励信号的输出时间、与所述目标信号种类对应的激励信号的输出周期、与所述目标信号种类对应的激励信号的赋值。

5.根据权利要求4所述的方法,其特征在于,当所述目标信号种类包括两种或两种以上,与所述目标信号种类对应的激励信号信息还包括:与所述目标信号种类对应的激励信号的输出方式,其中,所述输出方式包括:串行输出或并行输出。

6.根据权利要求1或4或5所述的方法,其特征在于,所述目标信号种类包括以下至少一种:时钟信号、控制信号和数据信号,其中,所述控制信号包括:复位信号、使能信号、控制写信号、控制读信号。

7.根据权利要求1所述的方法,其特征在于,所述待验证设计文件的硬件描述语言包括:硬件描述语言verilog或超高速集成电路硬件描述语言vhdl。

8.根据权利要求3所述的方法,其特征在于,所述根据所述待验证设计文件的功能和所述待验证设计文件对应原语的实现逻辑的原则,采用聚类分析方法从所述待验证设计文件所涉及的信号种类中确定所述激励文件用于验证所述待验证设计文件的激励信号,包括:

9.一种激励文件的生成系统,其特征在于,包括:分析模块、架构模块和处理模块;

10.根据权利要求9所述的系统,其特征在于,所述系统通过统一建模语言uml建模技术实现可视化。

技术总结

一种激励文件的生成方法及系统,根据待验证设计文件及与待验证设计文件的硬件描述语言对应的原语库获取待验证设计文件的设计属性信息;根据获得的设计属性信息获取用于验证待验证设计文件的激励文件的基础架构;获取与基础架构中输入激励部分确定的目标信号种类对应的激励信号信息,并执行以下调整操作:将获得的激励信号信息作为输入激励部分的内容,得到经过处理的基础架构,对其进行仿真并输出仿真结果,获取根据仿真结果调整的激励信号信息,根据调整获得的激励信号信息继续执行调整操作,直到仿真结果符合预设要求,将经过处理的基础架构作为激励文件。本公开实施例能够自动生成激励文件,降低操作难度,减少花费时间,提高生成效率。

技术研发人员:毕京晓,李杨,赵方亮,杜金凤,王常慧

受保护的技术使用者:山东高云半导体科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!