用飞行中预取服务于CPU需求请求的制作方法

此大体上涉及数字数据处理,且更确切地说,涉及高速缓存操作。

背景技术:

1、常规数字数据处理器以非常快的时钟操作,且通常执行指令的速度比其从通用存储器中召回的速度快。对将指令提供到数字数据处理器的问题的已知解决方案称为指令高速缓存。数字数据处理系统以物理及计算接近性对需要指令控制的数据要素提供小的快速存储器。此小的快速存储器存储所需指令的子集。数字数据处理器常常循环地工作。如果指令循环的全部或大部分存储在高速缓存中,则数字数据处理器可保持以比从通用存储器重新调用要快的速率用指令馈送。

2、由于这些高速缓存方案,在实际需要之前确定将使用何指令是有帮助的。此类预取使得高速缓存能够预测对于指令的需要。在需要时,预取的指令可能已经存储在高速缓存中。

3、许多预取技术存在一些问题。举例来说,由cpu提取的需求可能在对相同指令的预取待决的同时发生。

技术实现思路

1、一种数字数据处理设备包含:中央处理单元核心;以及一级指令高速缓存。所述中央处理单元核心响应于程序指令而执行数据处理操作。所述中央处理单元核心在需要时经由请求地址发布对额外程序指令的指令请求。所述一级指令高速缓存在一级高速缓存行中暂时存储程序指令的子集。在所述中央处理单元请求请求地址处的指令时,所述一级指令高速缓存确定其是否在所述请求地址处存储所述指令。如果是,则所述一级指令高速缓存供应所述所请求程序指令。如果否,则所述一级指令高速缓存将所述请求地址供应到另一存储器以获得高速缓存服务。

2、所述包含分支预测器,其预测程序分支的所采取/未采取状态。在指令请求时,所述分支预测器计算且供应在指令存取之后在预测支路将脱离线性路径之前所请求的线性后续指令的数目的指令计数。

3、预取单元接收所述指令请求地址及所述指令计数。所述预取单元依序产生对在所述所请求指令之后的线性后续指令的高速缓存预取请求直到所述指令计数。

4、程序存储器控制器确定所述一级指令高速缓存是否存储所请求指令或所预取指令。如果所述高速缓存存储所请求指令,则将其从所述高速缓存供应到所述中央处理单元核心。如果所述高速缓存存储所预取指令,则所述程序存储器控制器不采取动作。

5、如果所述高速缓存不存储所请求指令或所预取指令,则所述程序控制器从另一存储器请求高速缓存服务。所述程序存储器控制器确定为所述请求地址分配的高速缓存通道。在所述高速缓存服务待决时,所述请求地址、所述对应的所分配高速缓存通道及请求识别码存储在记分板条目中。

6、在由指令请求触发预取的情况下,有可能在高速缓存系统正服务于对在所述高速缓存中未命中的后续指令的待决预取的同时出现对相同指令的指令请求。在此情境中,产生对所述指令请求的高速缓存服务请求会造成冗余操作。此举否定了待决预取的价值。常规上,通过比较指令请求的指令请求地址与记分板中所有条目的请求地址来检测特定高速缓存危险。由于地址大小及记分板条目的数目,此可能需要相当大的电力。如果检测到高速缓存危险,则修改记分板条目以将待决预取改变为需求提取。因此,通过返回到待决预取来服务于稍后出现的指令请求。如果未检测到危险,则程序存储器控制器请求对所述需求请求的高速缓存服务。

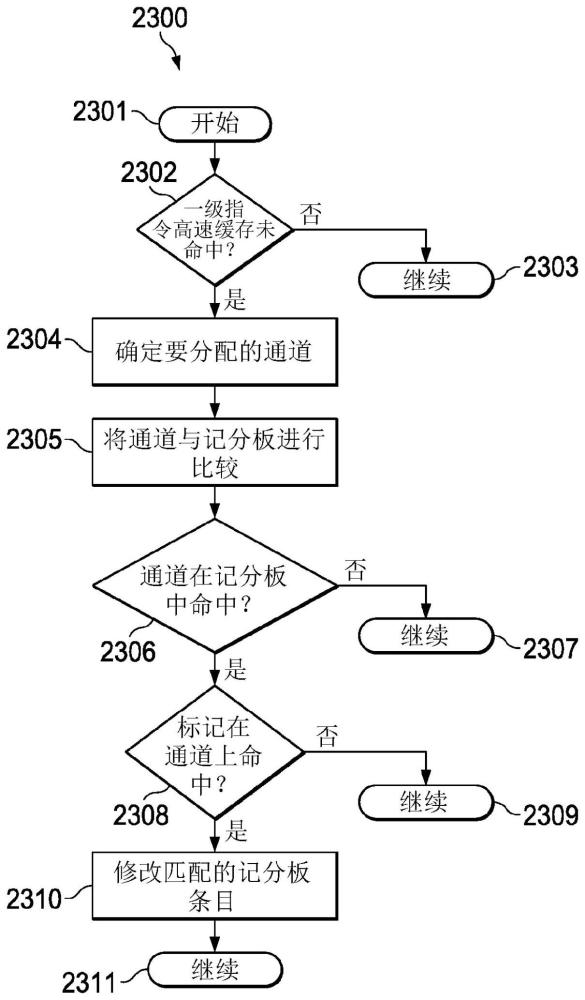

7、在所描述的实施例中,以节省电力的方式检测此指令危险。所述程序存储器控制器在确定高速缓存未命中时确定所述高速缓存通道。此所确定高速缓存通道存储在用于所述高速缓存服务请求的所述记分板条目中。在产生危险的条件(对于与待决预取相同的指令,需求请求未命中高速缓存)下,所述需求请求与所述预取将分配到相同通道。所述程序存储器控制器比较所述需求请求的所述所分配通道与所有所述记分板条目的所分配通道。仅在所述所分配通道匹配时才发生高速缓存危险。在通道比较之后,将所述需求请求地址仅与具有匹配通道的那些记分板条目的请求地址进行比较。在此时间期间不对其它地址比较器供电。此用以减少检测此高速缓存危险所需要的电力。

技术特征:

1.一种方法,其包括:

2.根据权利要求1所述的方法,其进一步包括响应于基于对所述指令的所述预取请求待决并且不导致包含所述指令的所述传回的所述确定的所述需求提取请求,禁止发出来自所述第二级的对所述指令的请求。

3.根据权利要求1所述的方法,其进一步包括将来自所述传回的所述指令存储在所述第一级中,其中,响应于所述需求提取请求,在将所述指令存储在所述第一级中之前执行向所述处理核心提供所述指令。

4.根据权利要求1所述的方法,其中:

5.根据权利要求1所述的方法,其进一步包括响应于与所述预取请求相关联的所述传回从所述记分板中删除与所述预取请求相关联的所述第一条目。

6.根据权利要求1所述的方法,其进一步包括:

7.根据权利要求1所述的方法,其进一步包括通过提供所述传回经由所述第二级以服务对来自所述第二级的对所述指令的预取请求。

8.根据权利要求1所述的方法,其中所述高速缓存结构的所述第一级是一级(l1)高速缓存,且所述高速缓存结构的所述第二级是二级(l2)高速缓存。

9.根据权利要求1所述的方法,其中:

10.根据权利要求9所述的方法,其进一步包括,对于所述预取请求组中的每个预取请求:

11.一种装置,其包括:

12.根据权利要求11所述的装置,其中所述存储器控制器进一步可操作以:

13.根据权利要求11所述的装置,其中所述存储器控制器进一步可操作以基于对所述指令的所述预取请求待决且不导致包括所述指令的传回的确定来响应于所述需求提取请求以禁止发出来自所述第二级高速缓存的对所述指令的请求。

14.根据权利要求11所述的装置,其中所述存储器控制器进一步可操作以,在提供所述指令至所述处理器核心后,存储来自所述传回的所述指令在所述第一级高速缓存中。

15.根据权利要求11所述的装置,其中所述多个条目中的每个条目进一步包括请求/预取指示符;及

16.根据权利要求11所述的装置,其中:

17.根据权利要求11所述的装置,其中所述存储器控制器进一步可操作以响应于所述返回从所述记分板中删除所述第一条目。

18.根据权利要求11所述的装置,其中所述第一级高速缓存是一级(l1)高速缓存,而所述二级高速缓存是二级(l2)高速缓存。

19.根据权利要求11所述的装置,其中,所述第一级高速缓存是一级指令(l1i)高速缓存,并且所述第二级高速缓存是包括指令和数据的二级(l2)高速缓存。

20.根据权利要求11所述的装置,其进一步包括所述二级高速缓存。

21.一种方法,其包括:

22.根据权利要求21所述的方法,其进一步包括确定所述预取请求是否在所述第一高速缓存级中未命中,其中基于在所述第一高速缓存级中未命中的所述预取请求来执行所述服务请求的所述生成。

23.根据权利要求21所述的方法,其进一步包括确定所述需求请求是否在所述第一高速缓存级中未命中,其中基于在所述第一高速缓存级中未命中的所述需求请求来执行所述需求请求是否与所述预取请求相关联的所述确定。

24.根据权利要求23所述的方法,其中所述需求请求是否在所述第一高速缓存级中未命中的所述确定包括:

25.根据权利要求21所述的方法,其进一步包括基于响应于所述服务请求的所述接收的所述数据组,从所述记分板存储器中删除所述指示。

26.根据权利要求21所述的方法,其进一步包括在所述提供所述服务请求之后,使经分配以存储所述数据组的所述第一高速缓存级的行无效。

27.根据权利要求21所述的方法,其中所述指示指定与所述预取请求相关联的通道和与所述预取请求相关联的地址。

28.根据权利要求21所述的方法,其中所述提供所述数据组将所述数据组提供给处理器且基于所述记分板存储器中的所述指示来执行,所述指示指定所述服务请求与所述需求操作相关联。

29.根据权利要求21所述的方法,其中:

30.根据权利要求21所述的方法,其进一步包括存储所述数据组在所述第一高速缓存级的高速缓存存储器中。

31.一种装置,其包括:

32.根据权利要求31所述的装置,其中:

33.根据权利要求31所述的装置,其中:

34.根据权利要求33所述的装置,其中所述高速缓存控制器经配置以确定所述需求请求是否在所述第一高速级缓存中未命中通过:

35.根据权利要求31所述的装置,其中所述高速缓存控制器经配置以基于响应于所述服务请求所接收的所述数据组,从所述记分板存储器中删除所述指示。

36.根据权利要求31所述的装置,其中所述高速缓存控制器经配置以在提供所述服务请求之后使经分配以存储所述数据组的所述第一级高速缓存的行无效。

37.根据权利要求31所述的装置,其中指示指定与所述预取请求相关联的通道和与所述预取请求相关联的地址。

38.根据权利要求31所述的装置,其中所述高速缓存控制器经配置以基于所述记分板存储器中的所述指示将所述数据组提供至所述处理器核心,所述指示指定所述服务请求与所述需求操作相关联。

39.根据权利要求31所述的装置,其中:

40.根据权利要求31所述的装置,其中所述高速缓存控制器经配置以将所述数据组存储在所述第一级高速缓存中。

技术总结

本申请涉及用飞行中预取服务于CPU需求请求。为高速缓存中的未命中的指令请求可能在高速缓存系统正服务于对相同指令的待决预取时发生。常规上,通过比较记分板中所有条目的请求地址来检测特定高速缓存危险。程序存储器控制器将所分配通道存储在所述记分板中。程序存储器控制器比较(2305)需求请求的所述所分配通道与所有记分板条目的所述所分配通道。仅在所述所分配通道匹配(2306)时才发生所述高速缓存危险。在通道比较(2305,2306)之后,将需求请求地址仅与具有匹配通道的那些记分板条目的所述请求地址进行比较(2308)。在此时间期间不对其它地址比较器供电。此用以减少检测此高速缓存危险所需要的电力。

技术研发人员:O·奥洛罗德,R·文卡塔苏巴拉尼亚

受保护的技术使用者:德州仪器公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!