一种基于SRAM的数字域存内计算方法及装置

本技术涉及神经网络,特别是涉及一种基于sram的数字域存内计算方法及装置。

背景技术:

1、随着神经网络技术的不断发展,网络参数规模逐渐增大,伴随着摩尔定律的逐渐放缓,硬件的发展速度远远落后于网络的发展速度。因此,为了应对人们日益升高的带宽需求,存内计算技术应运而生。存内计算作为一种新兴的计算架构,将计算与存储相融合,使得计算能够在存储单元内部完成。在并行处理大量矩阵向量乘法的操作上,由于其方法本身具有高并行度以及高能量效益等有益效果,存内计算具有明显的优势。

2、存内计算大致分为数字域存内计算和模拟域存内计算,在目前的基于sram结构的数字域存内计算架构中,通常采用多个精确加法器所构建的加法器树来对sram(staticrandom-access memory,静态随机存取存储器)阵列的的乘法结果进行累加以完成数据的计算,虽然此方法能够实现较高精度的数据运算,但其由于精确加法器树的结构较为复杂,使得整个加法器树的结构在整个cim(computing-in-memory,存内计算)宏中占据了大量的面积和功耗,一定程度上降低了数字域存内计算所带来的优势。

3、在现有技术中,通常通过在加法器树中直接采用或门来替代精确全加器,此方法虽然能够减少加法器树所占据的面积和功耗,但由于此方法相对于传统的精确全加器而言逻辑过于简单,直接的替换使得数据运算的精度较差。因此,在采取此方法时,所得到的数据运算结果往往具有较大的运算误差。

4、因此,如何在加法器树不占据大量面积和功耗的情况下,保证数据域存内计算的精确性,成为本领域技术人员急需解决的技术问题。

技术实现思路

1、基于上述问题,为了在不占据加法器树大量面积和功耗的情况下,保证数据域存内计算的精确性,本技术提供了一种基于sram的数字域存内计算方法及装置。

2、本技术实施例公开了如下技术方案:

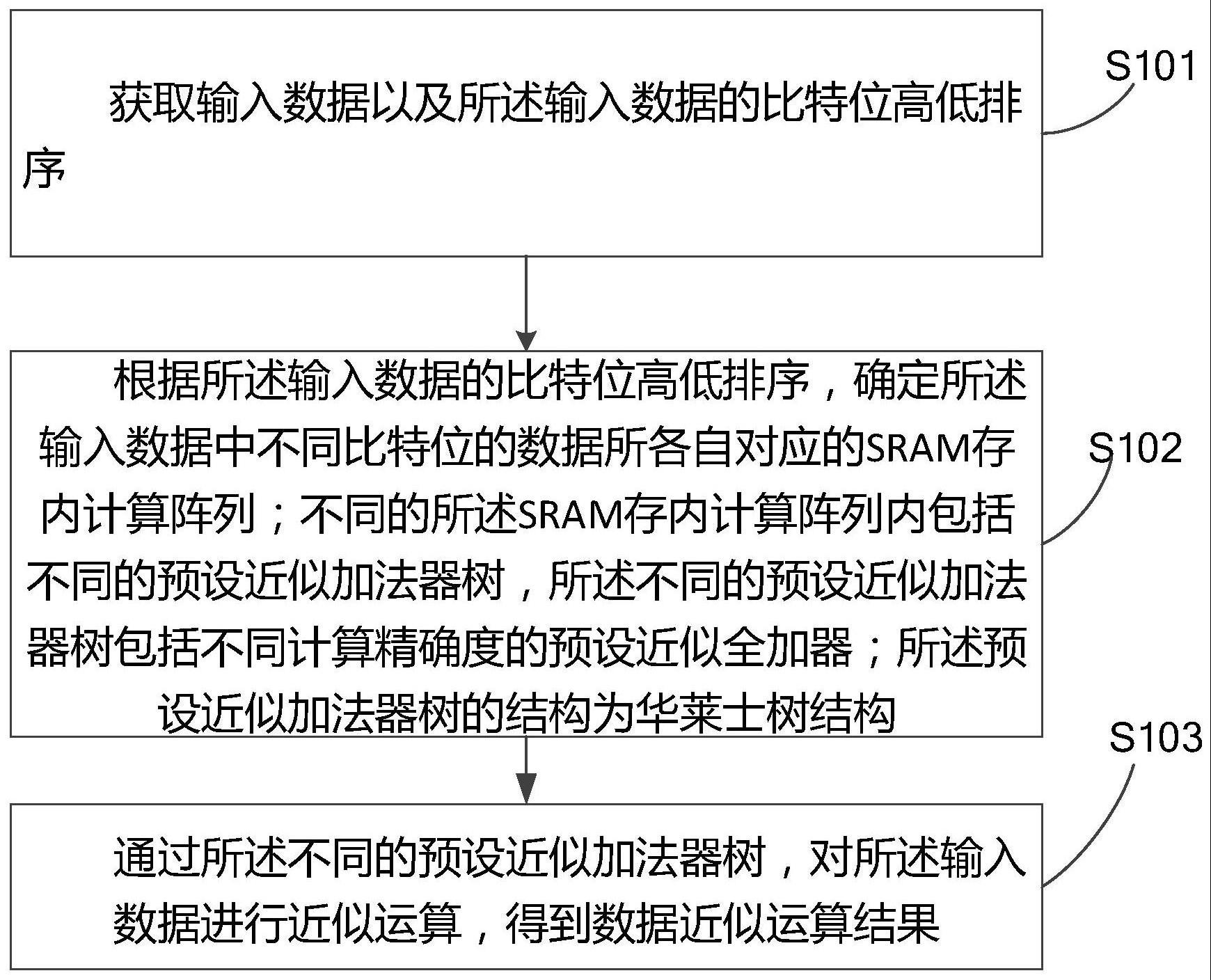

3、第一方面,本技术公开了一种基于sram的数字域存内计算方法,包括:

4、获取输入数据以及所述输入数据的比特位高低排序;

5、根据所述输入数据的比特位高低排序,确定所述输入数据中不同比特位的数据所各自对应的sram存内计算阵列;不同的所述sram存内计算阵列内包括不同的预设近似加法器树,所述不同的预设近似加法器树包括不同计算精确度的预设近似全加器;所述预设近似加法器树的结构为华莱士树结构;

6、通过所述不同的预设近似加法器树,对所述输入数据进行近似运算,得到数据近似运算结果。

7、可选的,所述获取输入数据之后,还包括:

8、按照预设数据划分规则,对所述输入数据进行数据划分,得到第一数据集和第二数据集。

9、可选的,所述预设近似加法器树,包括:或门和传统全加器;

10、所述或门用于对所述第一输入数据集进行数据压缩,得到压缩数据,并将所述压缩数据发送至所述传统全加器;

11、所述预设近似全加器用于对所述第二输入数据集进行近似运算,得到近似运算数据,并将所述近似运算数据发送至所述传统全加器;

12、所述传统全加器用于根据所述压缩数据和所述近似运算数据,生成所述数据近似运算结果。

13、可选的,所述预设近似全加器至少包括:第一预设近似全加器和第二预设近似全加器;所述第一预设近似全加器的门级电路包括:异或门、与门以及第一或门;

14、所述与门的第一输入端为加数输入端,第二输入端为被加数输入端,所述与门的输出端连接第一或门的第一输入端;

15、所述第一或门的第二输入端为低位进位输入端,输出端为所述门级电路的高位进位输出端;

16、所述异或门第一输入端为加数输入端,第二输入端为被加数输入端,输出端为所述门级电路的和输出端。

17、可选的,所述第二预设全加器的门级电路包括:第二或门;

18、所述第二或门的第一输入端为加数输入端,第二输入端为被加数输入端,所述第二或门的输出端为所述第二预设加法器的门级电路的和输出端。

19、可选的,所述根据所述输入数据的比特位高低排序,确定所述输入数据中不同比特位的数据所各自对应的sram存内计算阵列,具体包括:

20、在所述输入数据中,对所述比特位高低排序高于预设阈值的数据采用包括所述第一预设近似全加器的sram存内计算阵列;

21、在所述输入数据中,对所述比特位高低排序低于所述预设阈值的数据采用包括所述第二预设近似全加器的sram存内计算阵列。

22、第二方面,本技术公开了一种基于sram的数字域存内计算装置,包括:

23、获取模块,用于获取输入数据以及所述输入数据的比特位高低排序;

24、加法器树确定模块,用于根据所述输入数据的比特位高低排序,确定所述输入数据中不同比特位的数据所各自对应的sram存内计算阵列;不同的所述sram存内计算阵列内包括不同的预设近似加法器树,所述不同的预设近似加法器树包括不同计算精确度的预设近似全加器;所述预设近似加法器树的结构为华莱士树结构;

25、数据近似运算模块,用于通过所述不同的预设近似加法器树,对所述输入数据进行近似运算,得到数据近似运算结果。

26、可选的,所述数字域存内计算装置,还包括:

27、数据划分模块,用于按照预设数据划分规则,对所述输入数据进行数据划分,得到第一数据集和第二数据集。

28、可选的,所述预设近似加法器树,包括:或门和传统全加器;

29、所述或门用于对所述第一输入数据集进行数据压缩,得到压缩数据,并将所述压缩数据发送至所述传统全加器;

30、所述预设近似全加器用于对所述第二输入数据集进行近似运算,得到近似运算数据,并将所述近似运算数据发送至所述传统全加器;

31、所述传统全加器用于根据所述压缩数据和所述近似运算数据,生成所述数据近似运算结果。

32、可选的,所述预设近似全加器至少包括:第一预设近似全加器和第二预设近似全加器;所述第一预设近似全加器的门级电路包括:异或门、与门以及第一或门;

33、所述与门的第一输入端为加数输入端,第二输入端为被加数输入端,所述与门的输出端连接第一或门的第一输入端;

34、所述第一或门的第二输入端为低位进位输入端,输出端为所述门级电路的高位进位输出端;

35、所述异或门第一输入端为加数输入端,第二输入端为被加数输入端,输出端为所述门级电路的和输出端。

36、相较于现有技术,本技术具有以下有益效果:本技术提供了一种基于sram的数字域存内计算方法及装置,首先获取输入数据以及输入数据的比特位高低排序,并根据输入数据的比特位高低排序,确定与其各自对应的sram存内计算阵列。其中,不同的sram存内计算阵列内包括不同的预设近似加法器树,不同的预设近似加法器树包括不同计算精确度的预设近似全加器;且加法器树的结构为华莱士树结构。最后通过预设近似加法器树,对所述输入数据进行近似运算,即可得到数据近似运算结果。通过上述方法,结合预设近似全加器以及华莱士树结构的应用,在降低加法器树面积和功耗的同时,能够根据输入数据的比特位高低排序,选择不同精确度的预设近似加法器树来进行数据的计算,从而在保证加法器树不占据大量面积和功耗的前提下,提升计算的精确性。

- 还没有人留言评论。精彩留言会获得点赞!