一种时钟与通信接口复用引脚的装置及方法与流程

本发明涉及通信,更具体地,涉及一种时钟与通信接口复用引脚的装置及方法。

背景技术:

1、数字电路工作以时钟为基础,时钟在电路中起着同步的作用。在芯片设计中,时钟可分为内部时钟和外部时钟。内部时钟集成在芯片内部,一般精度较低;外部时钟使用独立时钟源,通过芯片引脚为芯片提供时钟,一般精度较高。在使用高精度时钟的场景下需要外部时钟,即从芯片引脚输入高精度时钟信号。此外,仅在测试情况下使用的时钟,可用外部时钟,无需芯片内部集成,可降低芯片成本。

2、数字通信接口是芯片与外界交互的关键通道,一般在一个或多个引脚上施加激励信号实现数据交互。现有数字通信接口和外部时钟之间相互独立,使用独立的引脚。但是在设计中可能存在引脚数量不足的问题。同时通信接口与系统模块工作在各自的时钟域,存在跨时钟域问题。

3、因此,期待一种时钟与通信接口复用引脚的方法及装置,以节省芯片引脚和规避跨时钟域问题。

技术实现思路

1、本发明的目的是提出一种时钟与通信接口复用引脚的装置及方法,在芯片设计中节省引脚,同时,规避系统模块与接口模块之间的时钟异步问题。

2、基于上述目的,本发明提供了一种时钟与通信接口复用引脚的方法,包括:

3、系统时钟与通信接口的时序相结合,主机发出连续或间歇性的所述系统时钟,主机依据所述系统时钟的相位、电平、周期数产生满足一定通信协议时序的信号,基于所述通信协议时序的信号进行数据传输,并在数据传输的有效期间,统计所述系统时钟的周期数;当达到预期时钟周期数后,结束数据传输,从而实现从机的系统时钟输入引脚与通信接口的时钟引脚共用一个引脚以及,从机中,系统时钟与所述通信接口使用同一时钟。

4、可选方案中,所述通信协议为spi ,所述方法包括:

5、spi主机产生不受片选信号控制的spi从机需要的系统时钟,数据传输前所述系统时钟保持不停翻转;

6、spi主机检测所述系统时钟,并控制片选信号配合spi的模式在所述系统时钟为高电平或低电平时翻转;

7、在片选有效期内,spi主机和spi从机进行数据传输;

8、在数据传输的有效期间,计数时钟周期的个数;达到预期时钟周期后,结束数据传输。

9、spi主机发起数据传输时,相位检测模块检测时钟的电平,根据工作模式在所述系统时钟信号为高电平或者低电平时控制片选信号生效;spi主机结束数据传输结束时,相位检测模块检测时钟的电平,根据工作模式在所述系统时钟信号为高电平或者低电平时控制片选信号无效。

10、可选方案中,根据选择的spi时钟极性的不同,片选信号在时钟高电平或低电平期间翻转。spi主机发起数据传输时,相位检测模块检测时钟的电平,根据工作模式在所述系统时钟信号为高电平或者低电平时控制片选信号翻转为生效。spi主机结束数据传输结束时,相位检测模块检测时钟的电平,根据工作模式在所述系统时钟信号为高电平或者低电平时控制片选信号翻转为无效。

11、可选方案中,所述通信协议为i2c,所述方法包括:

12、i2c主机产生i2c从机需要的系统时钟,数据传输前所述系统时钟保持不停翻转;

13、i2c主机检测所述系统时钟,并在所述系统时钟为高电平时控制sda信号翻转以产生start信号和stop 信号;

14、在所述start信号和所述stop信号期间,所述i2c主机和所述i2c从机进行数据传输;在数据传输的有效期间,计数时钟周期的个数;达到预期时钟周期后,结束数据传输。

15、i2c主机开始数据传输时,等待相位检测模块检测到scl为高电平时,在sda信号线上输出下降沿,以产生start信号;i2c主机结束数据传输时,等待相位检测模块检测到scl为高电平时,在sda信号线上输出上升沿,以产生stop信号。

16、本发明还提供了一种基于spi协议的时钟与通信接口复用引脚的装置,包括:

17、设置在spi主机中的:

18、时钟发生器,用于产生spi从机需要的系统时钟和sck信号;

19、片选信号发生器,产生符合spi时序要求的片选信号;

20、时钟计数器,计算片选信号有效的时间内所述系统时钟的周期数;

21、时钟相位检测器,用于检测所述系统时钟的相位或电平;

22、读写控制器,产生读或写命令;

23、设置在所述spi从机中的:

24、时钟门控,在片选信号无效时屏蔽spi从机中读写控制器的时钟;

25、读写控制器,产生读或写命令;

26、spi从机中的所述读写控制器与所述spi从机使用同一系统时钟。

27、可选方案中,所述时钟发生器连接于所述时钟计数器的输入和所述时钟相位检测器的输入;所述时钟计数器的输出和所述时钟相位检测器的输出连接于所述片选信号发生器的输入。

28、可选方案中,所述时钟门控的输入端连接于所述片选信号发生器的输出端和所述时钟发生器的输出端,所述时钟门控的输出端连接于所述spi从机中的所述读写控制器。

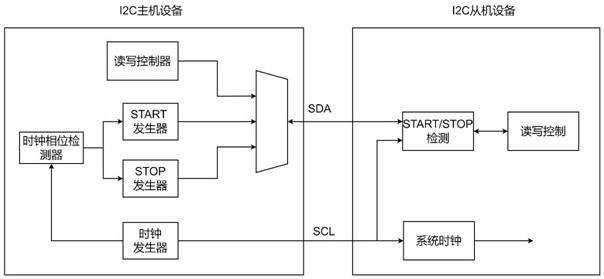

29、本发明还提供了一种基于i2c协议的时钟与通信接口复用引脚的装置,包括:

30、设置在i2c主机中的:

31、时钟发生器,用于产生i2c从机需要的系统时钟和scl信号;

32、时钟相位检测器,用于检测所述系统时钟的相位或电平;

33、start发生器,用于产生i2c通信中的start信号;

34、stop发生器,用于产生i2c通信中的stop信号;

35、读写控制器,执行读或写操作;

36、设置在i2c从机中的:

37、start/stop信号检测器,用于检测start/stop信号;

38、读写控制器,执行读或写操作;

39、i2c从机中的所述读写控制器与所述i2c从机使用同一系统时钟。

40、可选方案中,所述时钟发生器连接于所述时钟相位检测器的输入;所述时钟相位检测器的输出连接于所述start发生器的输入和所述stop发生器的输入;

41、选择模块,连接于所述start发生器的输出和所述stop发生器的输出以及所述i2c主机中的所述读写控制器和所述i2c从机中的所述start/stop信号检测器。

42、可选方案中,所述start/stop信号检测器连接于所述时钟发生器和所述i2c从机中的所述读写控制器。

43、本发明通过时钟信号与通信接口(spi/i2c)时序的结合达到复用引脚的效果,设计中减少引脚数量,在引脚数量受限的情况下,实现通信接口和外部时钟同时存在。

44、本发明具有其它的特性和优点,这些特性和优点从并入本文中的附图和随后的具体实施方式中将是显而易见的,或者将在并入本文中的附图和随后的具体实施方式中进行详细陈述,这些附图和具体实施方式共同用于解释本发明的特定原理。

- 还没有人留言评论。精彩留言会获得点赞!