基于关键值真值表的数字电路仿真方法及装置与流程

本公开涉及数字电路领域,具体而言,涉及一种基于关键值真值表的数字电路仿真方法及装置。

背景技术:

1、数字电路是用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。逻辑门是数字逻辑电路的基本单元。数字电路可以分为组合逻辑电路和时序逻辑电路两大类。

2、eda仿真器可以对电路的功能行为进行模拟,而不需要建立实际的电路(这过程可能繁琐而昂贵),因此它是一种很有实用价值的工具。在构建实际的电路之前,对设计进行仿真验证,可以大大地提高设计效率。这是由于,设计人员可以在构建电路之前,预先观察、研究电路的行为,而不必为电路的物理实现付出时间和经济的成本。尤其是集成电路,在物理上实现电路所需的光掩模等电子工艺成本不菲,而集成电路的高复杂性又在面包板上面难以实现,用传统的方法研究电路的行为较为困难。因此,几乎所有的集成电路设计都较为依赖仿真。最著名的模拟仿真是spice,而最著名的数字电路仿真器都是基于verilog或vhdl的。

3、数字电路是以二值数字逻辑为基础的,其工作信号是离散的数字信号,所以在一个数字电路中存在大量的以布尔逻辑表示的布尔函数,它们是数字电路中特别重要的组成部分。显然对于数字电路进行仿真需要计算大量的布尔函数,如果通过真值表获得布尔函数的值,则需要计算大量的布尔函数的真值表,布尔函数很多,此计算量也比较大。

4、在所述背景技术部分公开的上述信息仅用于加强对本申请的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、有鉴于此,本申请提供一种基于关键值真值表的数字电路仿真方法及装置,能够在数字电路仿真过程中加快真值表的获取效率,简化真值表占用空间,压缩真值表大小,进而提高布尔函数的计算时间,减少系统整体仿真时间。

2、本申请的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本申请的实践而习得。

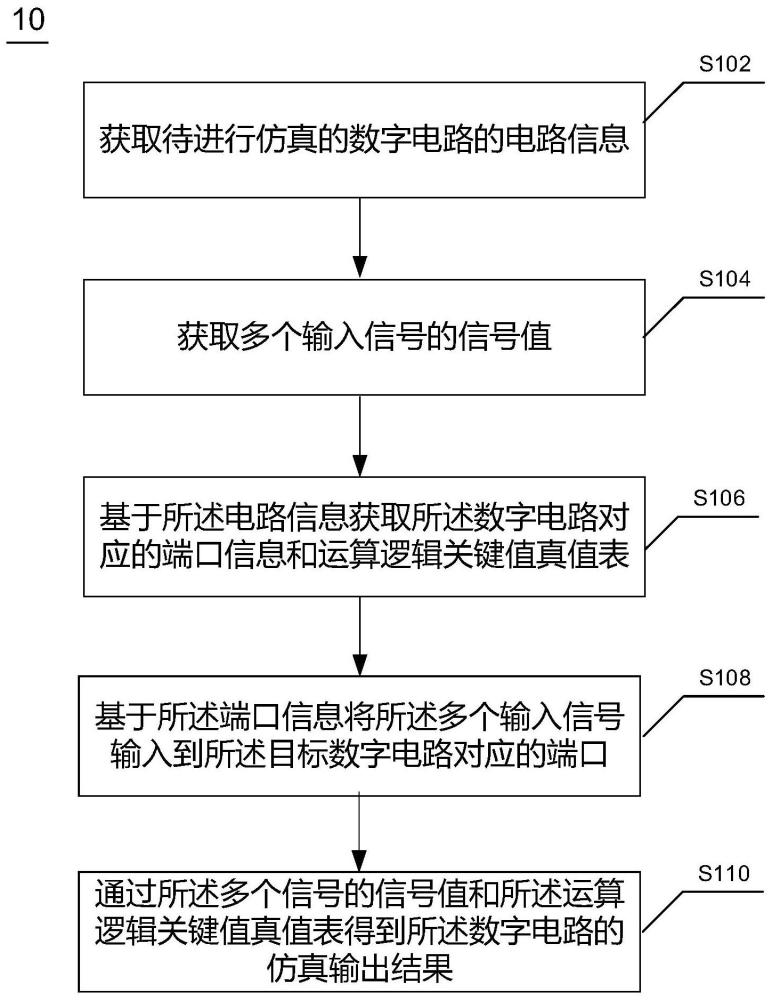

3、根据本申请的一方面,提出一种基于关键值真值表的数字电路仿真方法,该方法包括:获取待进行仿真的数字电路的电路信息;获取多个输入信号的信号值;基于所述电路信息获取所述数字电路对应的端口信息和运算逻辑关键值真值表;基于所述端口信息将所述多个输入信号输入到所述目标数字电路对应的端口;通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果。

4、在本申请的一种示例性实施例中,还包括:获取所述数字电路对应的布尔函数;解析所述布尔函数生成表达式树;基于所述表达式树生成所述运算逻辑关键值真值表。

5、在本申请的一种示例性实施例中,基于所述表达式树生成所述运算逻辑关键值真值表,包括:确定所述表达式树的根节点的目标值;基于所述目标值遍历所述表达式树;在遍历的过程中基于逻辑关系推算出所述布尔函数的运算逻辑关键值组合;通过所述运算逻辑关键值组合生成所述运算逻辑关键值真值表。

6、在本申请的一种示例性实施例中,基于所述目标值遍历所述表达式树,包括:将所述目标值作为所述表达式树的根节点对应的数值;基于所述目标值通过优先搜索算法遍历所述表达式树。

7、在本申请的一种示例性实施例中,在遍历的过程中基于逻辑关系推算出所述布尔函数的运算逻辑关键值组合,包括:在遍历表达式树的过程中,获取根节点的数值;根据所述根节点的数值和其对应的运算类型推算下层节点的数值;逐一遍历下层节点直至遍历到底层叶子节点为止;根据遍历结果生成所述运算逻辑关键值组合。

8、在本申请的一种示例性实施例中,逐一遍历下层节点直至遍历到底层叶子节点为止,包括:在逐一遍历下层节点的过程中,获取当前节点;在当前节点不为叶子节点时,根据所述当前节点的数值和其对应的运算类型推算下层节点的数值;遍历至底层叶子节点为止。

9、在本申请的一种示例性实施例中,根据遍历结果生成所述运算逻辑关键值组合,包括:由遍历结果中提取所述表达式树中所有的分支;将每个分支包含的叶子节点的数值作为该分支的运算逻辑关键值组合。

10、在本申请的一种示例性实施例中,通过所述运算逻辑关键值组合生成所述运算逻辑关键值真值表,包括:将所述运算逻辑关键值组合按照预设顺序排列;将所述目标值作为输出值;通过按照预设顺序排列的运算逻辑关键值组合和所述输出值生成所述运算逻辑关键值真值表。

11、在本申请的一种示例性实施例中,通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果,包括:逐行提取所述运算逻辑关键值真值表中的关键值组合;将所述多个信号的信号值和所述关键值组合比对以得到所述数字电路的仿真输出结果。

12、根据本申请的一方面,提出一种基于关键值真值表的数字电路仿真装置,该装置包括:电路模块,用于获取待进行仿真的数字电路的电路信息;信号模块,用于获取多个输入信号的信号值;真值表模块,用于基于所述电路信息获取所述数字电路对应的端口信息和逻辑关键值真值表;输入模块,用于基于所述端口信息将所述多个输入信号输入到所述目标数字电路对应的端口;输出模块,用于通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果。

13、根据本申请的一方面,提出一种电子设备,该电子设备包括:一个或多个处理器;存储装置,用于存储一个或多个程序;当一个或多个程序被一个或多个处理器执行,使得一个或多个处理器实现如上文的方法。

14、根据本申请的一方面,提出一种计算机可读介质,其上存储有计算机程序,该程序被处理器执行时实现如上文中的方法。

15、根据本申请的基于关键值真值表的数字电路仿真方法及装置,通过获取待进行仿真的数字电路的电路信息;获取多个输入信号的信号值;基于所述电路信息获取所述数字电路对应的端口信息和运算逻辑关键值真值表;基于所述端口信息将所述多个输入信号输入到所述目标数字电路对应的端口;通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果的方式,能够在数字电路仿真过程中加快真值表的获取效率,简化真值表占用空间,压缩真值表大小,进而提高布尔函数的计算时间,减少系统整体仿真时间。

16、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种基于关键值真值表的数字电路仿真方法,其特征在于,包括:

2.如权利要求1所述的数字电路仿真方法,其特征在于,还包括:

3.如权利要求2所述的数字电路仿真方法,其特征在于,基于所述表达式树生成所述运算逻辑关键值真值表,包括:

4.如权利要求3所述的数字电路仿真方法,其特征在于,基于所述目标值遍历所述表达式树,包括:

5.如权利要求3所述的数字电路仿真方法,其特征在于,在遍历的过程中基于逻辑关系推算出所述布尔函数的运算逻辑关键值组合,包括:

6.如权利要求5所述的数字电路仿真方法,其特征在于,逐一遍历下层节点直至遍历到底层叶子节点为止,包括:

7.如权利要求5所述的数字电路仿真方法,其特征在于,根据遍历结果生成所述运算逻辑关键值组合,包括:

8.如权利要求3所述的数字电路仿真方法,其特征在于,通过所述运算逻辑关键值组合生成所述运算逻辑关键值真值表,包括:

9.如权利要求1所述的数字电路仿真方法,其特征在于,通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果,包括:

10.一种基于关键值真值表的数字电路仿真装置,其特征在于,包括:

技术总结

本公开涉及一种基于关键值真值表的数字电路仿真方法及装置。该方法包括:获取待进行仿真的数字电路的电路信息;获取多个输入信号的信号值;基于所述电路信息获取所述数字电路对应的端口信息和运算逻辑关键值真值表;基于所述端口信息将所述多个输入信号输入到所述目标数字电路对应的端口;通过所述多个信号的信号值和所述运算逻辑关键值真值表得到所述数字电路的仿真输出结果。本申请涉及的基于关键值真值表的数字电路仿真方法及装置,能够在数字电路仿真过程中加快真值表的获取效率,简化真值表占用空间,压缩真值表大小,进而提高布尔函数的计算时间,减少系统整体仿真时间。

技术研发人员:刘治强,史峰

受保护的技术使用者:北京芯思维科技有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!