一种基于图表的FPGA触发条件配置方法与流程

本发明涉及芯片设计领域,尤其是涉及一种基于图表的fpga触发条件配置方法。

背景技术:

1、芯片设计领域中,生成数据波形需要配置探针的采集触发条件。已有的触发条件配置(如vivado)不支持带逻辑符组合的形式,无法做到多信号混合逻辑的复杂条件配置,使得用户在触发条件调试过程中无法实现多信号相互影响的情况,大大限制了触发条件的调试性。因此需要设计一种图形界面高可用、高动态、高安全性的触发条件配置方法,对齐每个信号独立设置触发条件信息,在视觉上更符合人类直觉,能够解决用户数据合法性审查的痛点,所有输入的数据和操作配置均是可靠且合法的。可以随时暂停采样操作,也可以随时添加新的触发条件,拥有非常强的即时调试能力,且支持多条件混合的触发条件,还可以对特殊的情况进行单独配置条件,大大提升采样效率。

技术实现思路

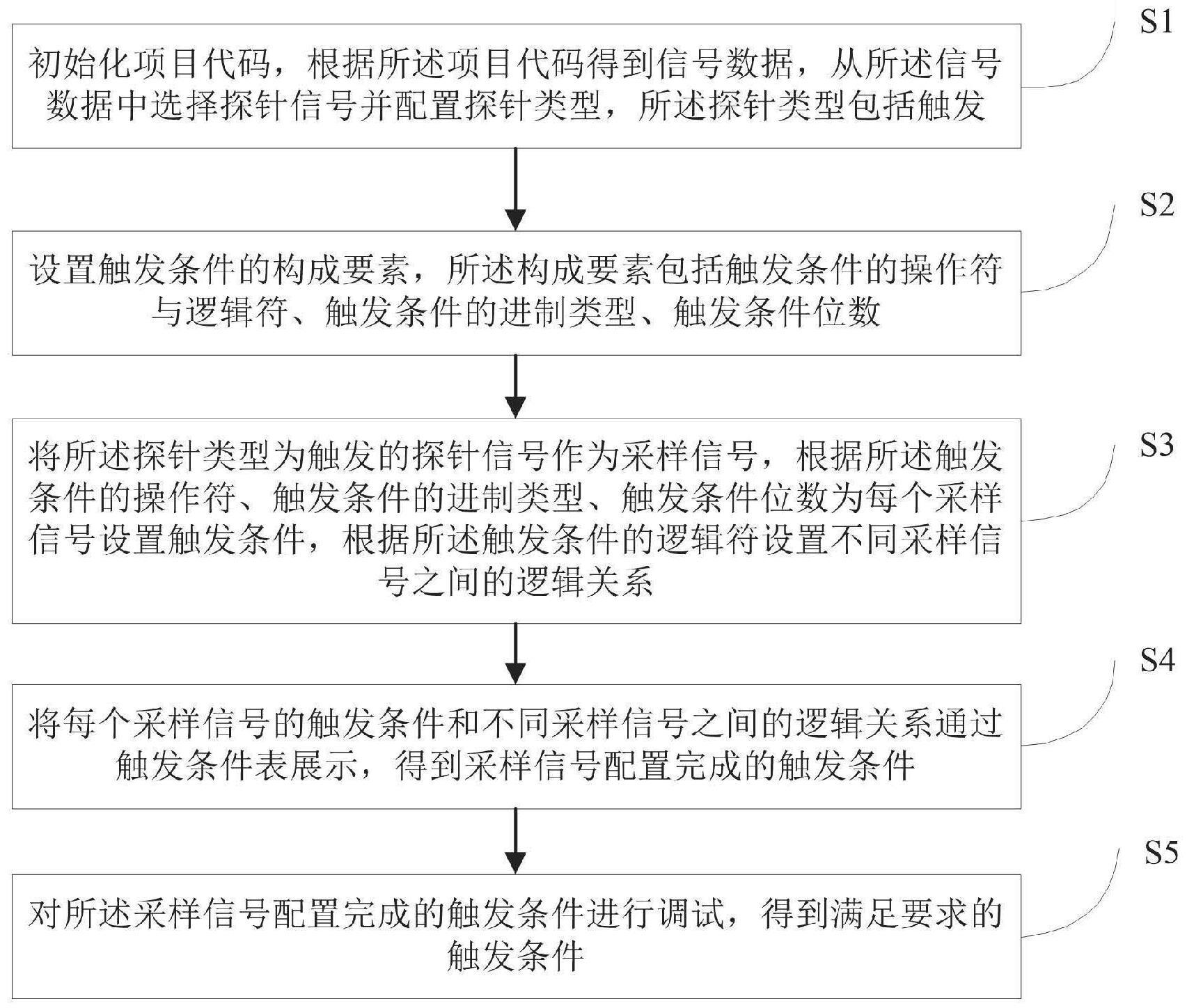

1、针对现有的触发条件配置(如vivado)不支持带逻辑符组合的形式,无法实现多信号混合逻辑的复杂条件配置这一技术问题,本发明提供了一种基于图表的fpga触发条件配置方法,包括如下步骤:

2、s1、初始化项目代码,根据项目代码得到信号数据,从信号数据中选择探针信号并配置探针类型,探针类型包括触发;

3、s2、设置触发条件的构成要素,构成要素包括触发条件的操作符与逻辑符、触发条件的进制类型、触发条件位数;

4、s3、将探针类型为触发的探针信号作为采样信号,根据触发条件的操作符、触发条件的进制类型、触发条件位数为每个采样信号设置触发条件,根据触发条件的逻辑符设置不同采样信号之间的逻辑关系;

5、s4、将每个采样信号的触发条件和不同采样信号之间的逻辑关系通过触发条件表展示,得到采样信号配置完成的触发条件;

6、s5、对采样信号配置完成的触发条件进行调试,得到满足要求的触发条件。

7、优选地,s1具体包括:

8、s11、初始化项目代码,将用verilog编程语言编写的项目代码编译成fpga硬件使用的格式代码,得到初始化后的项目代码;

9、s12、根据初始化后的项目代码生成需要采样的信号数据,将需要采样的信号数据导入fpga波形采样系统,经过处理,输出每个信号的位宽并生成总信号树;

10、s13、设置探针类型,在总信号树中根据用户需求选择探针信号,并为探针信号配置探针类型,探针类型包括触发。

11、优选地,s2中触发条件的操作符具体包括:==、!=、<、<=、>、>=。

12、优选地,s2中触发条件的逻辑符具体包括:and、nand、nor、or。

13、优选地,s2中触发条件的进制类型具体包括:二进制(b)、八进制(o)、十进制有符号(s)、十进制无符号(u)、十六进制(h)。

14、优选地,s2中触发条件位数和采样信号的位宽对应。

15、优选地,s3根据触发条件的操作符、触发条件的进制类型、触发条件位数为每个采样信号设置触发条件,具体包括:为每个采样信号新增、编辑或删除触发条件。

16、优选地,s4中将每个采样信号的触发条件和不同采样信号之间的逻辑关系通过触发条件表展示,触发条件表的字段包括采样信号名称、操作符、基数、实际值和编辑。

17、上述一种基于图表的fpga触发条件配置方法,首先初始化项目代码,根据初始化后的项目代码得到信号数据,从信号数据中选择探针信号并配置探针类型,将探针类型配置为触发的探针信号作为采样信号;设置触发条件的构成要素,根据触发条件构成要素中的操作符、触发条件的进制类型和触发条件位数为每个采样信号设置触发条件,根据触发条件构成要素中的逻辑符设置不同采样信号之间的逻辑关系,由此得到采样信号配置完成的触发条件;对配置完成的触发条件进行调试,得到满足要求的触发条件。该方法支持大数据量情况下的逻辑组合,用户可根据实际情况任意组合无限量的信号触发条件,提升采样效率。

技术特征:

1.一种基于图表的fpga触发条件配置方法,其特征在于,包括如下步骤:

2.如权利要求1所述的基于图表的fpga触发条件配置方法,其特征在于,所述s1具体包括:

3.如权利要求2所述的基于图表的fpga触发条件配置方法,其特征在于,所述s2中触发条件的操作符具体包括:==、!=、<、<=、>、>=。

4.如权利要求3所述的基于图表的fpga触发条件配置方法,其特征在于,所述s2中触发条件的逻辑符具体包括:and、nand、nor、or。

5.如权利要求4所述的基于图表的fpga触发条件配置方法,其特征在于,所述s2中触发条件的进制类型具体包括:二进制(b)、八进制(o)、十进制有符号(s)、十进制无符号(u)、十六进制(h)。

6.如权利要求5所述的基于图表的fpga触发条件配置方法,其特征在于,所述s2中触发条件位数和所述采样信号的位宽对应。

7.如权利要求6所述的基于图表的fpga触发条件配置方法,其特征在于,所述s3根据所述触发条件的操作符、触发条件的进制类型、触发条件位数为每个采样信号设置触发条件,具体包括:为每个采样信号新增、编辑或删除触发条件。

8.如权利要求7所述的基于图表的fpga触发条件配置方法,其特征在于,所述s4中将每个采样信号的触发条件和不同采样信号之间的逻辑关系通过触发条件表展示,所述触发条件表的字段包括采样信号名称、操作符、基数、实际值和编辑。

技术总结

本发明公开了一种基于图表的FPGA触发条件配置方法,初始化项目代码,根据初始化后的项目代码得到信号数据,从信号数据中选择探针信号并配置探针类型;将探针类型配置为触发的探针信号作为采样信号;设置触发条件的构成要素,根据触发条件构成要素中的操作符、触发条件的进制类型和触发条件位数为每个采样信号设置触发条件,根据触发条件构成要素中的逻辑符设置不同采样信号之间的逻辑关系,由此得到采样信号配置完成的触发条件;对配置完成的触发条件进行调试,得到满足要求的触发条件。该方法支持大数据量情况下的逻辑组合,用户可根据实际情况任意组合无限量的信号触发条件,提升采样效率。

技术研发人员:请求不公布姓名

受保护的技术使用者:湖南泛联新安信息科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!