DMA数据传输控制系统的制作方法

本发明涉及数据传输,特别涉及一种dma数据传输控制系统。

背景技术:

1、在当前的pc(personal computer,个人计算机)与fpga(field program gateway,现场可编程的门阵列)的pcie(peripheral component interconnect express,高速串行总线)数据通信中,目前有三种ip(intellectual property,知识产权)核模块,分别是pcie intergrated block、axi bridge pcie、dma/bridge pcie。

2、第一种:pcie intergrated block是最基础的pcie硬核,实现的是pcie的物理层、链路层和事务层,提供给用户的是以交互系统接口定义的tlp(transaction layerpacket,事务层数据)包。用户如果需要给pc发数据,则在逻辑端组好mem_wr事务包送到axis接口上,同样要从pc获取数据,就要发送mem_rd事务包,然后获取到complete事务包,再从complete事务包中提取出数据。然而,这是方式传输数据过程较为繁琐。

3、第二种:axi bridge pcie的作用类似于一座桥,一座fpga端直通上位机内存的桥,用户如需读写上位机内存空间,只需要操作这个ip核的s_axi接口,就可以像读写普通axi接口的bram/ddr一样读写上位机内存。对于采集卡而言,fpga收到数据后,只需要根据上位机配下来的写内存地址寄存器,就可以将数据以 axi memory接口标准发往上位机,然后产生中断让cpu(central processing unit,中央处理器)从相应内存地址去读取数据,这种方式ip就省去了组事务层包的烦恼,只要把数据发上去即可,组包的事ip会解决。然而,这种方式需要cpu参与数据的传输过程,增加了cpu的工作压力。

4、第三种:dma/bridge pcie,该ip核不但能够把事务层的组包解包完成,还能把需要dma处理的任务也完成。因此,该方式是一种效率较高的开发方法。然而,在申请传输较大内存的数据时,需要申请较多的内存块,导致产生较多的物理地址,容易出现数据传输错误的情况。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的目的在于提出一种dma数据传输控制系统,以减小中央处理器的工作压力,提高数据传输速度。

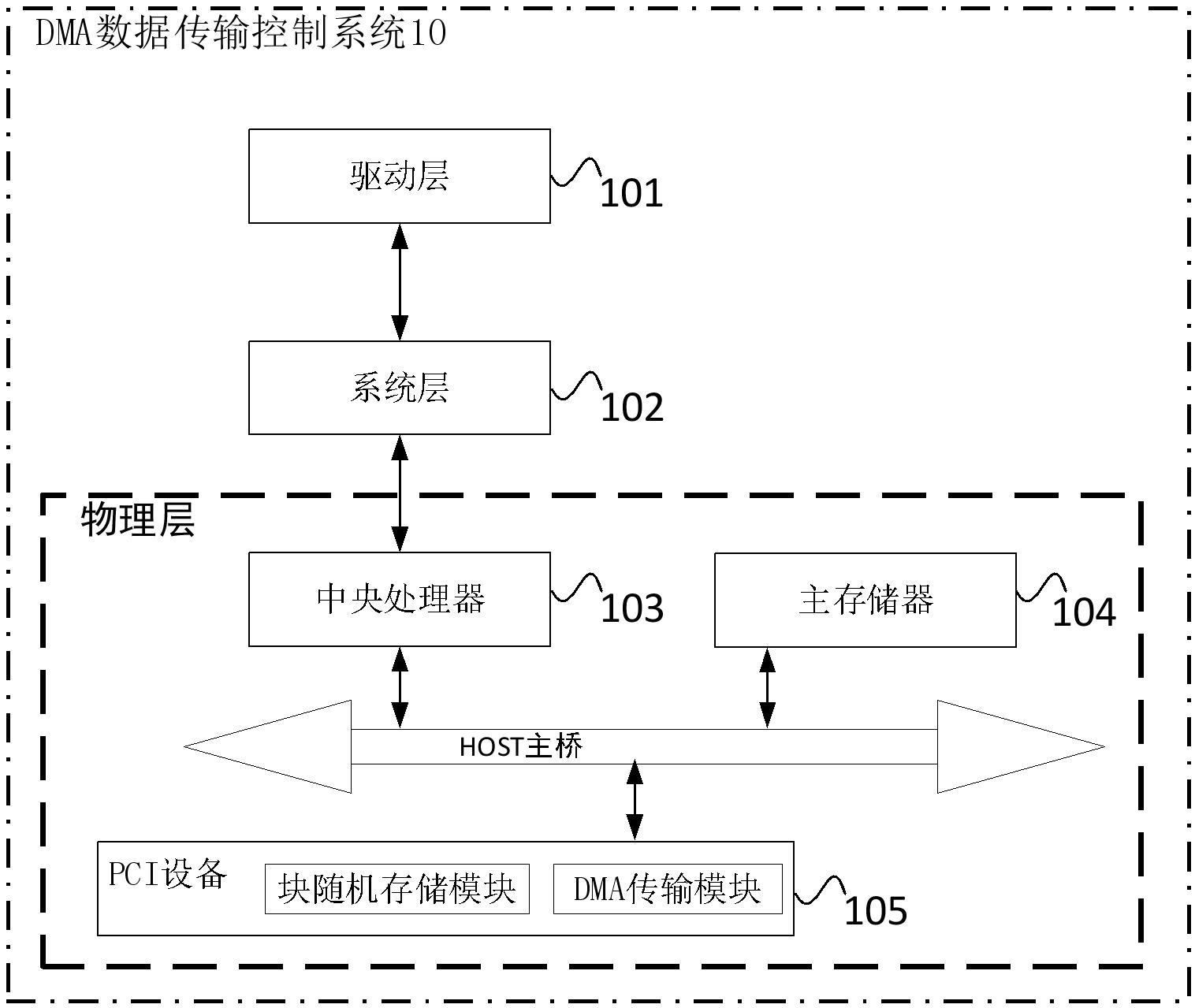

2、为达到上述目的,本发明实施例提出了一种dma数据传输控制系统,所述系统包括:驱动层、系统层、中央处理器、主存储器、pci设备。所述驱动层,用于生成第一内存申请指令,并在环形缓存空间申请成功后,生成内存描述符;所述系统层,与所述驱动层连接,用于接收所述第一内存申请指令,并生成第二内存申请指令;所述中央处理器,分别与所述系统层、主存储器连接,用于接收并执行所述第二内存申请指令,以申请所述主存储器内的所述环形缓存空间;所述主存储器,与所述中央处理器连接,用于提供所述环形缓存空间;所述pci设备,分别与所述中央处理器、所述主存储器连接,所述pci设备包括块随机存储模块和dma传输模块,所述块随机存储模块用于存储所述环形缓存空间的内存描述符,所述dma传输模块用于根据所述内存描述符向所述环形缓存空间传输数据;其中,所述内存描述符的个数为n个,且2≤n≤50,所述内存描述符用于描述物理地址连续的内存空间的起始物理地址及存储空间大小信息,n个所述内存描述符所描述的存储空间大小之和等于所述环形缓存空间的大小。

3、另外,本发明实施例的dma数据传输控制系统还可以具有如下附加技术特征:

4、根据本发明的一个实施例,所述环形缓存空间的大小记为第一目标值,所述中央处理器在申请所述主存储器内的所述环形缓存空间时,具体用于:以第二目标值申请物理地址连续的内存空间,其中,所述第二目标值的初始值为预设值,所述第二目标值小于所述第一目标值;当申请失败后,更新所述第二目标值,并返回所述以第二目标值申请物理地址连续的内存空间的步骤,其中,更新后的第二目标值小于更新前的第二目标值;当申请成功后,获取申请到的内存空间的物理地址,并判断累积申请到的存储空间大小是否达到所述第一目标值;若是,则确定申请完成;若否,则返回所述以第二目标值申请物理地址连续的内存空间的步骤。

5、根据本发明的一个实施例,所述中央处理器在更新所述第二目标值时,具体用于:计算所述第二目标值的半值;将所述半值作为更新后的第二目标值。

6、根据本发明的一个实施例,所述中央处理器在计算所述第二目标值的半值之后,还具体用于:计算所述第一目标值与所述累积申请到的内存空间大小之间的差值,并判断所述差值是否小于所述半值;若是,则将所述差值作为更新后的第二目标值;若否,则执行所述将所述半值作为更新后的第二目标值的步骤。

7、根据本发明的一个实施例,所述pci设备、所述中央处理器、所述主存储器通过访问通道连接;其中,所述访问通道为host主桥,所述pci设备通过pci接口连接所述host主桥。

8、根据本发明的一个实施例,所述主存储器包括地址映射页表,所述地址映射页表用于记录物理地址和虚拟地址的对应信息;所述系统层包括内存申请模块,所述内存申请模块用于接收所述驱动层发送的所述第一内存申请指令,并生成基于机器语言的所述第二内存申请指令;所述中央处理器包括内存管理模块,所述内存管理模块用于执行所述第二内存申请指令并反馈申请结果给所述内存申请模块,其中,若申请成功,则所述申请结果为申请到的物理地址连续的内存空间的起始物理地址及存储空间大小信息,将所述申请到的物理地址连续的内存空间的起始物理地址依据所述地址映射页表转化为虚拟地址后再反馈给所述内存申请模块,若申请失败,则所述申请结果为空白信息,并将所述空白信息反馈给所述内存申请模块;所述驱动层还用于生成环形缓存列表,所述环形缓存列表包括申请到的物理上连续的内存空间的虚拟地址及存储空间大小信息。

9、根据本发明的一个实施例,所述系统还包括:应用层,与所述驱动层连接,用于接收用户指令及对所述环形缓存空间中存储的数据进行调用。

10、根据本发明的一个实施例,所述dma传输模块还用于对n个所述内存描述符进行排序,且依次循环往复依据n个所述内存描述符向所述环形缓存空间传输数据;其中,所述dma传输模块每传输固定量的数据就向所述应用层发送一次中断信息,所述应用层依据所述中断信息和所述环形缓存列表调用所述环形缓存空间中存储的数据。

11、根据本发明的一个实施例,所述应用层还用于下发停止dma传输指令和退出程序指令;所述dma传输模块还用于接收所述停止dma传输指令,从而停止向所述环形缓存空间传输数据;所述驱动层还用于接收所述退出程序指令,从而释放申请到的所述环形缓存空间,并由所述系统层进行回收。

12、根据本发明的一个实施例,所述pci设备还包括axi bridge pcie ip核,所述axibridge pcie ip核用于将所述dma传输模块输出的数据打包成tlp数据包,并将所述tlp数据包发送给所述主存储器;其中,所述tlp数据包包含所述中断信息。

13、本发明实施例的dma数据传输控制系统,在数据传输过程不需要驱动层、系统层、中央处理器持续地下发物理地址,节约了计算资源,减小了中央处理器的工作压力,数据传输也更加流畅,能够实现更快的数据传输速度,同时,在申请较大内存时,内存块个数少,空间利用率较高。

- 还没有人留言评论。精彩留言会获得点赞!