一种基于FIFO存储器的轮询读写方法和装置与流程

本发明涉及数据缓存,尤其涉及一种基于fifo存储器的轮询读写方法和装置。

背景技术:

1、fifo(first input first output,先入先出)存储器通常都是由dpram或者spram和一部分控制逻辑构建而成,其主要特点是先写入fifo存储器的数据会被先读出,同时对外输出满信号(full信号)和空信号(empty信号)等状态信号,外部逻辑电路根据上述状态信号来进行正确的读写操作。在fpga(field programmable gate array,现场可编程逻辑门阵列)和芯片设计中,例化fifo存储器时经常面临两方面的问题:一是,fifo存储器容量大小受到限制的问题;二是,面积过大的fifo存储器在后端布线过程中容易出现拥塞及timing的问题。

2、现有技术中一般通过级联的方式来解决上述问题,即采用多个小容量fifo存储器级联以增加容量,从第一级的小容量fifo存储器开始,当前的小容量fifo存储器写满后,将数据通路切换到下一级的小容量fifo存储器。采用上述方式,虽然实现了大容量fifo存储器的功能,但是其控制逻辑复杂,需要用到大量的组合逻辑,使用不方便。

技术实现思路

1、鉴于上述的分析,本发明实施例旨在提供一种基于fifo存储器的轮询读写方法和装置,用以解决现有技术中通过级联小容量fifo存储器实大容量fifo存储器的功能导致控制逻辑复杂的技术问题。

2、一方面,本发明实施例提供了一种基于fifo存储器的轮询读写方法,所述方法包括:

3、将fifo存储器组电连接在输入控制单元与输出控制单元之间,所述fifo存储器组包括至少两个并联的小容量fifo存储器;

4、在所述fifo存储器组中写入数据时,所述输入控制单元按照轮询机制依次对各所述小容量fifo存储器执行单个数据的写入操作;

5、从所述fifo存储器组中读出数据时,所述输出控制单元按照轮询机制依次对各所述小容量fifo存储器执行单个数据的读出操作。

6、基于上述方法的进一步改进,所述方法还包括:

7、所述输入控制单元根据所述小容量fifo存储器的存储状态判断所述fifo存储器组是否为满状态;

8、若所述小容量fifo存储器均为满状态,则所述fifo存储器组为满状态;

9、所述fifo存储器组为满状态时,所述输入控制单元不允许在所述fifo存储器组中写入数据。

10、基于上述方法的进一步改进,所述方法还包括:

11、所述输出控制单元根据所述小容量fifo存储器的存储状态判断所述fifo存储器组是否为空状态;

12、若所述小容量fifo存储器均为空状态,则所述fifo存储器组为空状态;

13、所述fifo存储器组为空状态时,所述输出控制单元不允许从所述fifo存储器组中读出数据。

14、基于上述方法的进一步改进,在所述fifo存储器组中写入数据时,所述输入控制单元按照轮询机制依次对各所述小容量fifo存储器执行单个数据的写入操作,包括:

15、在所述fifo存储器组中写入数据时,所述输入控制单元通过第一循环计数器为写入所述fifo存储器组中的数据进行计数,并按照所述第一循环计数器的计数值顺序对各所述小容量fifo存储器执行单个数据的写入操作。

16、基于上述方法的进一步改进,从所述fifo存储器组中读出数据时,所述输出控制单元按照轮询机制依次对各所述小容量fifo存储器执行单个数据的读出操作,包括:

17、所述输出控制单元通过第二循环计数器为从所述fifo存储器组中读出的数据进行计数,并按照所述第二循环计数器的计数值顺序对各所述小容量fifo存储器执行单个数据的读出操作。

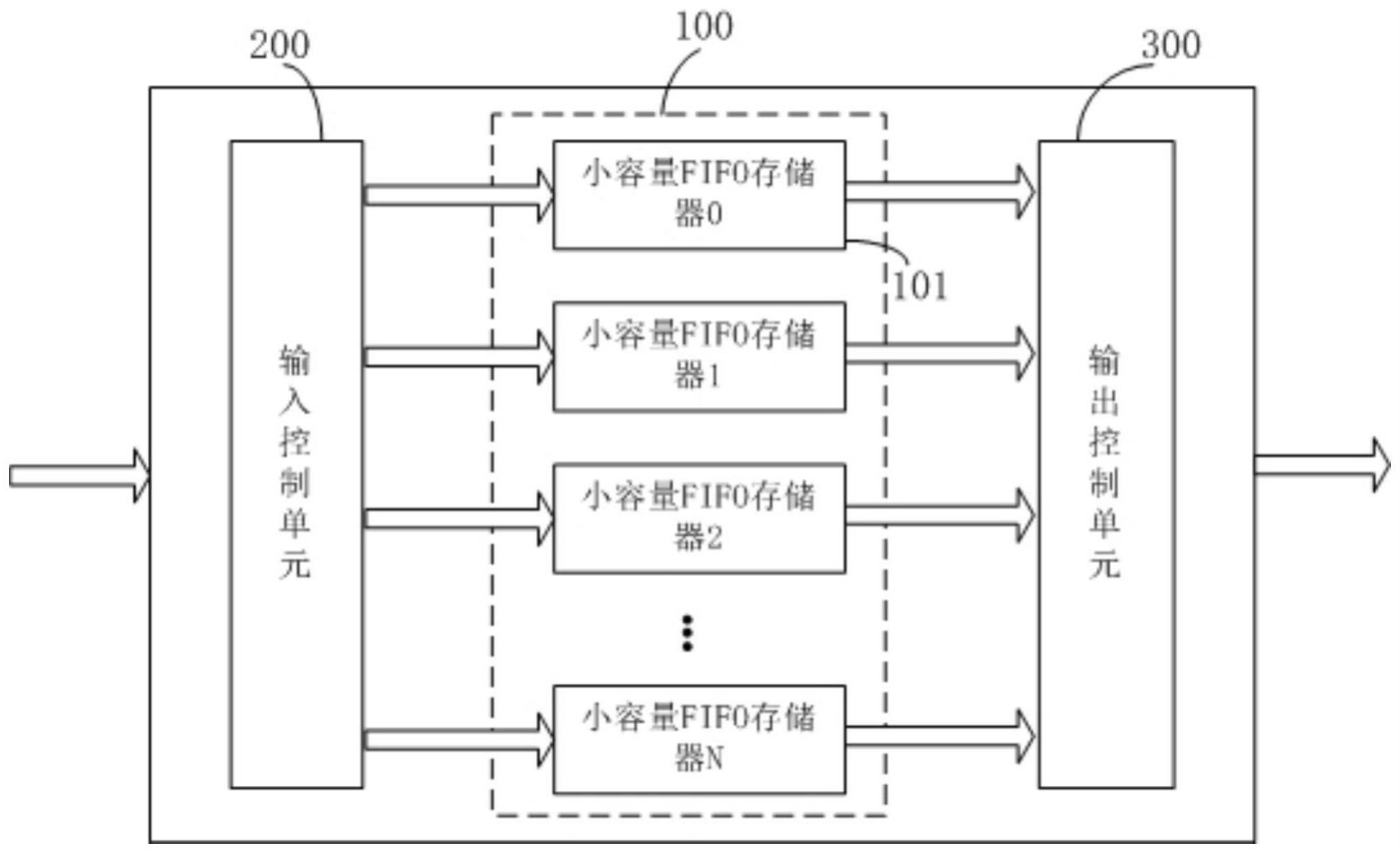

18、另一方面,本发明实施例提供了一种基于fifo存储器的轮询读写装置,所述装置包括:

19、所述fifo存储器组,包括至少两个并联的小容量fifo存储器;

20、输入控制单元,与所述fifo存储器组电连接,所述输入控制单元配置为在所述fifo存储器组中写入数据时,按照轮询机制依次对各所述小容量fifo存储器执行单个数据的写入操作;以及

21、输出控制单元,与所述fifo存储器组电连接,所述输出控制单元配置为从所述fifo存储器组中读出数据时,按照轮询机制依次对各所述小容量fifo存储器执行单个数据的读出操作。

22、基于上述装置的进一步改进,所述输入控制单元中设置有第一与逻辑模块,

23、所述第一与逻辑模块配置为在所述小容量fifo存储器均为满状态时,判断所述fifo存储器组为满状态;

24、所述fifo存储器组为满状态时,所述输入控制单元不允许在所述fifo存储器组中写入数据。

25、基于上述装置的进一步改进,所述输出控制单元中设置有第二与逻辑模块,

26、所述第二与逻辑模块配置为在所述小容量fifo存储器均为空状态时,判断所述fifo存储器组为空状态;

27、所述fifo存储器组为空状态时,所述输出控制单元不允许从所述fifo存储器组中读出数据。

28、基于上述装置的进一步改进,所述输入控制单元中设置有第一循环计数器,所述第一循环计数器配置为写入所述fifo存储器组中的数据进行计数,所述输入控制单元按照所述第一循环计数器的计数值顺序对各所述小容量fifo存储器执行单个数据的写入操作;

29、基于上述装置的进一步改进,所述输出控制单元中设置有第二循环计数器,所述第二循环计数器配置为从所述fifo存储器组中读出的数据进行计数;所述输出控制单元按照所述第二循环计数器的计数值顺序对各所述小容量fifo存储器执行单个数据的读出操作。

30、与现有技术相比,本发明至少可实现如下有益效果之一:

31、1、在例化fifo存储器容量受限的条件下,本发明实施例中,通过轮询读写多个(至少两个)并联的小容量fifo存储器的方式实现大面积fifo存储器的功能,实现方式简单,降低了控制逻辑的复杂度,并且保留了标准fifo存储器读写接口的特性。

32、2、同时,本发明通过多个小容量fifo存储器实现了大容量fifo存储器的功能,连接方式简单,小容量fifo存储器的个数易于扩展,从而降低了后端布线的难度,为fpga和芯片设计提供了更大的灵活性,应用范围广、通用性强。

33、3、本发明实施例中,通过所有的小容量fifo存储器的当前的存储状态判断fifo存储器组的存储状态,判断逻辑简单。当所有的小容量fifo存储器均存满数据时,表示fifo存储器组存储数据已满,此时则不允许写入数据,避免数据溢出;当所有的小容量fifo存储器均未存有数据时,表示fifo存储器组存储数据已空,此时则不允许读出数据,避免读数据错误。

34、本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!