一种基于PCIE互联的多核异构芯片、启动方法和系统与流程

本技术涉及芯片启动,特别是涉及一种基于pcie互联的多核异构芯片、启动方法和系统。

背景技术:

1、随着自动驾驶、人工智能等技术的不断发展,对计算能力的需求也越来越高。在一些高算力需求的场景下,单个芯片的计算能力无法满足需求。

2、例如,在自动驾驶领域,需要对车辆周围的环境进行实时感知和处理,这就需要匹配高效的传感器和计算平台。又如,在人工智能领域,需要进行大规模的数据处理和模型训练,也需要高性能的计算平台。因此,在一些具有高性能计算需求的场景中,可以通过多个子芯片构成的多核异构芯片进行联合计算,提高整个系统的计算能力,完成计算任务。

3、相关技术中,如图1所示,多核异构芯片中的每个子芯片(子芯片-1、子芯片-2、……、子芯片-n),分别独立地加载相应的启动镜像并运行,这需要在电路板上为每个子芯片预留独立的存储介质,来存储相应的启动软件包和启动镜像。因此,采用这种方法,电路布局的复杂程度大,多个启动软件包(启动软件包-1、启动软件包-2、……、启动软件包-n)的管理难度大,并且,由于需要多个存储介质(第二存储介质-1、第二存储介质-2、……、第二存储介质-n,以及第一存储介质-1、第一存储介质-2、……、第一存储介质-n),导致成本高。

技术实现思路

1、为了解决现有技术中存在的至少一个问题,本技术的目的在于提供一种基于pcie互联的多核异构芯片、启动方法和系统,不仅能够降低电路布局的复杂程度,减少芯片管脚的使用,提高芯片的适用性,而且实现了仅用一个启动软件包的多子芯片联合计算,有效降低了启动软件包的管理难度,此外还减少了存储介质的数量,有助于降低成本。

2、为实现上述目的,本技术提供了一种基于pcie互联的多核异构芯片启动方法,多核异构芯片包括通过pcie互联的第一子芯片和第二子芯片;所述多核异构芯片被配置有第一存储介质,所述第一存储介质存储有一个启动软件包,所述启动软件包中包括所述第一子芯片的第一启动镜像和所述第二子芯片的第二启动镜像;所述第一子芯片被配置有第二存储介质;

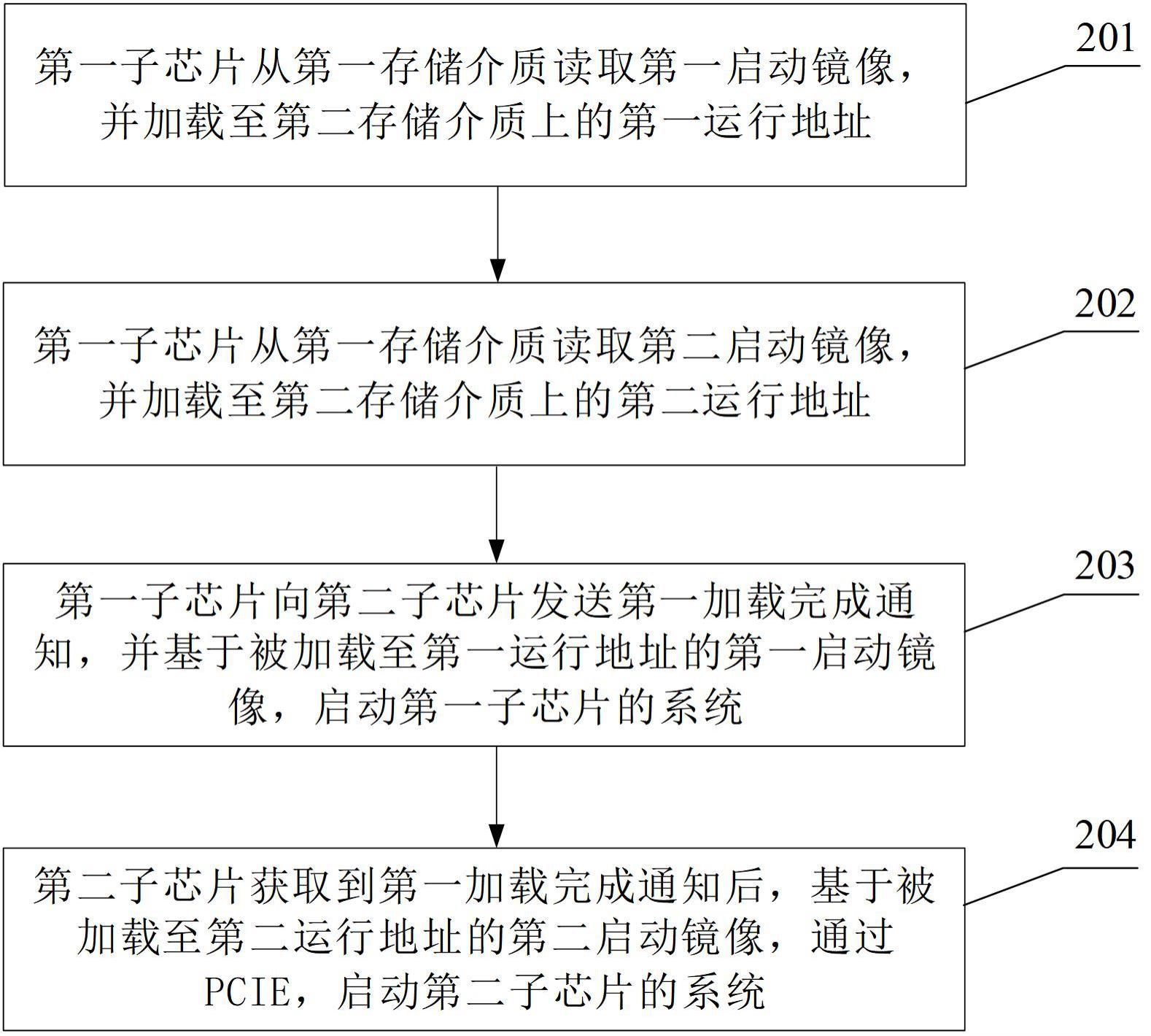

3、所述方法,包括,

4、所述第一子芯片从所述第一存储介质读取所述第一启动镜像,并加载至所述第二存储介质上的第一运行地址;

5、所述第一子芯片从所述第一存储介质读取所述第二启动镜像,并加载至所述第二存储介质上的第二运行地址;

6、所述第一子芯片向所述第二子芯片发送第一加载完成通知,并基于被加载至所述第一运行地址的第一启动镜像,启动所述第一子芯片的系统;

7、所述第二子芯片获取到所述第一加载完成通知后,基于被加载至所述第二运行地址的第二启动镜像,通过pcie,启动所述第二子芯片的系统。

8、进一步地,所述第一子芯片从所述第一存储介质读取所述第一启动镜像的步骤前,所述方法还包括,

9、所述第一子芯片初始化所述第二存储介质;

10、所述第一子芯片在所述第二存储介质中配置出第一存储空间和第二存储空间;并在所述第一存储空间中配置所述第一运行地址,在所述第二存储空间中配置所述第二运行地址。

11、更进一步地,所述第一子芯片向所述第二子芯片发送第一加载完成通知的步骤前,所述方法还包括,

12、所述第一子芯片将对应的pcie端配置为终端模式;

13、所述第二子芯片将对应的pcie端配置为根复合体模式;

14、所述第一子芯片将所述第二存储介质的第二存储空间,通过相应的基地址寄存器空间,映射至所述第二子芯片的pcie端。

15、进一步地,所述第一子芯片向所述第二子芯片发送第一加载完成通知的步骤,包括,

16、响应于所述第二启动镜像加载完成后,所述第一子芯片将所述第一子芯片上的第一寄存器的标志位置位;

17、所述第二子芯片通过pcie读取所述第一寄存器;

18、响应于读取到所述第一寄存器的标志位处于复位状态,所述第二子芯片处于等待模式;在所述等待模式中,所述第二子芯片循环读取所述第一寄存器;

19、响应于读取到所述第一寄存器的标志位处于置位状态,所述第二子芯片退出所述等待模式,并获取所述第二运行地址。

20、进一步地,所述第二子芯片启动所述第二子芯片的系统的步骤前,所述方法包括,

21、所述第二子芯片对相应的基地址寄存器空间配置pcie映射区域,并配置系统运行参数。

22、进一步地,所述多核异构芯片还包括,与所述第二子芯片pcie互联的第三子芯片;所述启动软件包中还包括所述第三子芯片的第三启动镜像;所述方法还包括,

23、所述第一子芯片从所述第一存储介质读取所述第三启动镜像,并加载至所述第二存储介质上的第三运行地址;

24、所述第一子芯片通过pcie,将第二加载完成通知发送至所述第二子芯片;

25、所述第二子芯片通过pcie,将接收到的第二加载完成通知,发送至所述第三子芯片;

26、第三子芯片接收到第二加载完成通知,基于被加载至所述第三运行地址的第三启动镜像,通过pcie,启动所述第三子芯片的系统。

27、更进一步地,所述第一子芯片从所述第一存储介质读取所述第三启动镜像的步骤前,所述方法还包括,

28、所述第一子芯片在所述第二存储介质中配置出第三存储空间,并在所述第三存储空间中配置所述第三运行地址。

29、更进一步地,所述第一子芯片在所述第二存储介质中配置出第三存储空间的步骤后,所述方法还包括,

30、所述第一子芯片将所述第二存储介质的第三存储空间,通过相应的基地址寄存器空间,映射至所述第二子芯片的pcie端;

31、所述第二子芯片将相应的基地址寄存器空间中映射的第三存储空间,映射至所述第三子芯片的pcie端。

32、为实现上述目的,本技术还提供的一种基于pcie互联的多核异构芯片,包括通过pcie互联的第一子芯片和第二子芯片;所述多核异构芯片被配置有第一存储介质,所述第一存储介质存储有一个启动软件包,所述启动软件包中包括所述第一子芯片的第一启动镜像和所述第二子芯片的第二启动镜像;所述第一子芯片被配置有第二存储介质;其中,

33、所述第一子芯片用于,从所述第一存储介质读取所述第一启动镜像,并加载至所述第二存储介质上的第一运行地址,以及从所述第一存储介质读取所述第二启动镜像,并加载至所述第二存储介质上的第二运行地址;

34、所述第一子芯片还用于,所述第二启动镜像加载完成后,向所述第二子芯片发送第一加载完成通知,并基于被加载至所述第一运行地址的第一启动镜像,启动所述第一子芯片的系统;

35、所述第二子芯片用于,获取到所述第一加载完成通知后,基于被加载至所述第二运行地址的第二启动镜像,通过pcie,启动所述第二子芯片的系统。

36、为实现上述目的,本技术还提供的一种基于pcie互联的多核异构芯片启动系统,包括,

37、第一存储介质,与多核异构芯片相配置,存储有一个启动软件包,所述启动软件包中包括第一子芯片的第一启动镜像和第二子芯片的第二启动镜像;

38、第二存储介质,与所述第一子芯片相配置;

39、多核异构芯片,包括通过pcie互联的第一子芯片和第二子芯片;其中,

40、所述第一子芯片用于,从所述第一存储介质读取所述第一启动镜像,并加载至所述第二存储介质上的第一运行地址,以及从所述第一存储介质读取所述第二启动镜像,并加载至所述第二存储介质上的第二运行地址;

41、所述第一子芯片还用于,所述第二启动镜像加载完成后,向所述第二子芯片发送第一加载完成通知,并基于被加载至所述第一运行地址的第一启动镜像,启动所述第一子芯片的系统;

42、所述第二子芯片用于,获取到所述第一加载完成通知后,基于被加载至所述第二运行地址的第二启动镜像,通过pcie,启动所述第二子芯片的系统。

43、为实现上述目的,本技术还提供的一种电子设备,包括存储器和处理器,所述存储器中存储有计算机指令,所述处理器被配置为运行所述指令以执行如上所述的基于pcie互联的多核异构芯片启动方法。

44、为实现上述目的,本技术还提供的一种计算机可读存储介质,其上存储有计算机指令,当计算机指令运行时执行如上所述的基于pcie互联的多核异构芯片启动方法的步骤。

45、本技术的一种基于pcie互联的多核异构芯片、启动方法和系统,通过多核异构芯片被配置有第一存储介质、pcie互联的第一子芯片和第二子芯片,第一存储介质存储有一个启动软件包,启动软件包中包括第一子芯片的第一启动镜像和第二子芯片的第二启动镜像,第一子芯片被配置有第二存储介质;并通过第一子芯片从第一存储介质分别读取第一启动镜像和第二启动镜像,分别对应加载至第二存储介质上的第一运行地址和第二运行地址;以及通过第一子芯片向第二子芯片发送第一加载完成通知,基于被加载至第一运行地址的第一启动镜像,启动第一子芯片的系统;并通过第二子芯片获取到第一加载完成通知后,基于被加载至第二运行地址的第二启动镜像,通过pcie启动第二子芯片的系统。由此,不仅能够降低电路布局的复杂程度,减少芯片管脚的使用,提高芯片的适用性,而且实现了仅用一个启动软件包的多子芯片联合计算,有效降低了启动软件包的管理难度,此外还减少了存储介质的数量,有助于降低成本。

46、本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。

- 还没有人留言评论。精彩留言会获得点赞!