时钟门控组件、多路复用器组件以及分频组件的制作方法

本发明涉及一种半导体装置。

背景技术:

1、随着计算机、通信和广播的逐渐融合,对专用集成电路(application specificintegrated circuit,asic)和专用标准产品(application specific standard product,assp)的需求由于对片上系统(system-on-chip,soc)的需求而改变。另外,趋向于更轻、更薄、更紧凑和更高性能信息技术(information technology,it)装置是驱动soc的发展的一个因素。

2、soc是具有各种功能的功能块(例如,知识产权(intellectual property,ip)块)借助于半导体处理技术的发展集成到其上的单芯片。

3、随着soc的集成密度、大小和操作速度增加,功率消耗更大程度上变成一个设计因素。当soc消耗大量功率时,soc的温度可能升高。如果温度升高太大,则soc可能发生故障或可能受损。

4、因此,需要一种soc以及可以防止soc消耗太多功率的驱动soc的方法。

技术实现思路

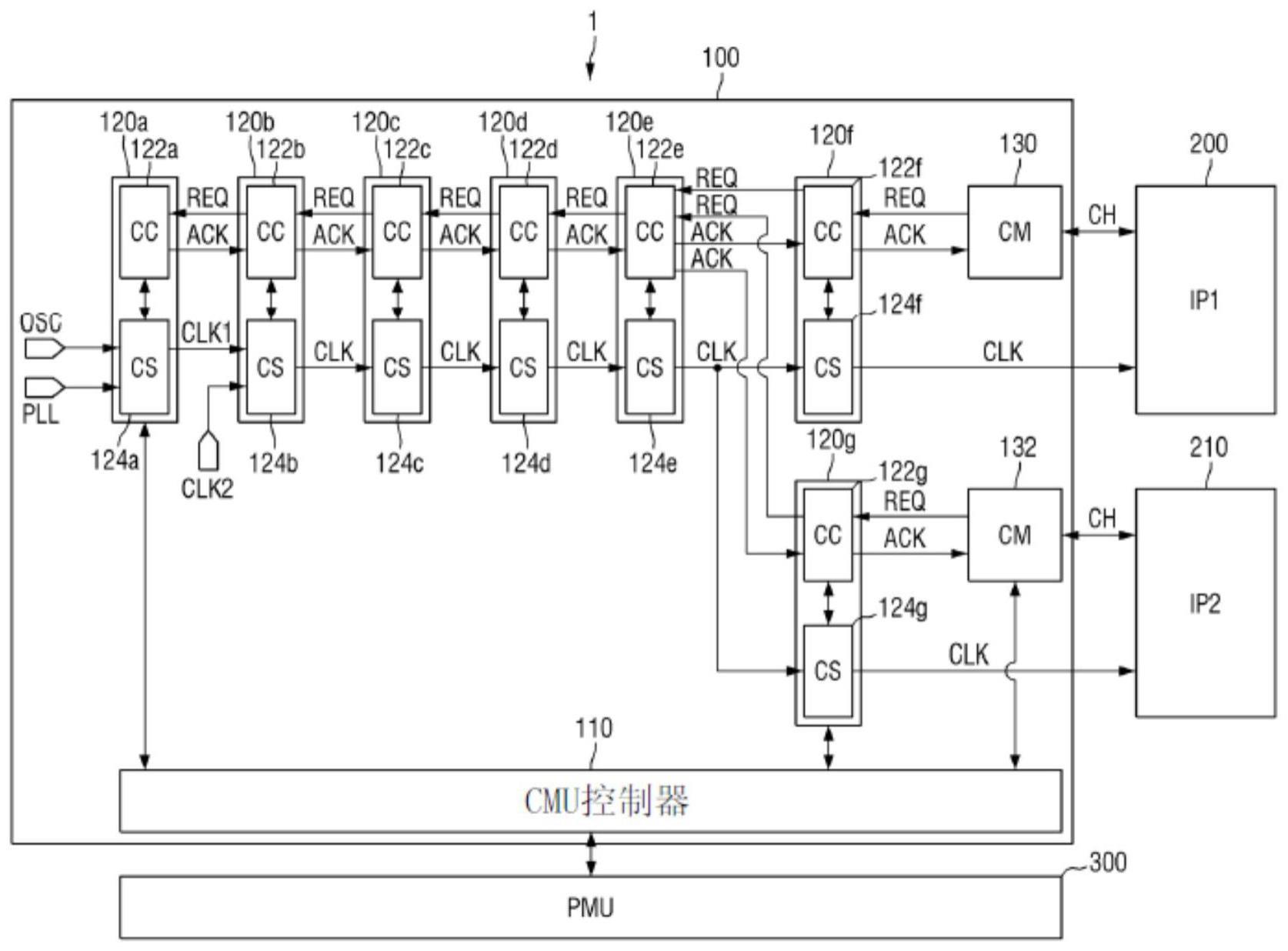

1、根据本发明概念的示例性实施例,片上系统(system on chip,soc)包含多个知识产权(intellectual property,ip)块和时钟管理单元(clock management unit,cmu),所述时钟管理单元被配置成对ip块的至少一个执行时钟门控。ip块和cmu使用完全握手方法彼此连接。

2、根据本发明概念的示例性实施例,时钟门控组件包含时钟控制电路,所述时钟控制电路被配置成产生操作时钟信号;以及信道管理(channel management,cm)电路,所述信道管理电路被配置成从外部装置接收跨越通信信道的请求信号并且将所述请求信号转发到时钟控制电路。时钟控制电路被配置成根据请求信号选择性地将操作时钟信号提供到外部装置并且将确认(ack)信号提供到cm电路。

3、根据本发明概念的示例性实施例,时钟多路复用器组件包含时钟控制电路,所述时钟控制电路被配置成基于第一选择信号而选择第一时钟信号和第二时钟信号中的一个、基于所述选定时钟信号而产生操作时钟信号并且响应于请求信号而选择性地输出所述操作时钟信号;以及信道管理(channel management,cm)电路,所述信道管理电路被配置成从外部装置接收跨越通信信道的请求信号并且将所述请求信号转发到所述时钟控制电路。

4、根据本发明概念的示例性实施例,时钟分频组件包含时钟控制电路,所述时钟控制电路被配置成对输入时钟信号执行分频操作以产生分频时钟信号、基于所述分频时钟信号而产生操作时钟信号并且响应于请求信号而将所述操作时钟信号选择性地输出到外部装置;以及信道管理(channel management,cm)电路,所述信道管理电路被配置成从外部装置接收跨越通信信道的请求信号并且将所述请求信号转发到所述时钟控制电路。

5、根据本发明概念的示例性实施例,操作时钟管理单元(clock management unit,cmu)的方法包含:cmu确定从知识产权(intellectual property,ip)块接收的请求信号是否指示ip块需要进入活动模式和休眠模式中的选定的一个;当请求信号指示ip块需要进入活动模式时,cmu将激活层处的确认(ack)信号和时钟信号输出到ip块;以及当时钟请求信号指示ip块需要进入休眠模式时,cmu将去激活层处的ack信号输出到ip块并且停止将时钟信号输出到ip块。

6、根据本发明概念的示例性实施例,时钟管理单元(clock management unit,cmu)包含控制器电路,所述控制器电路被配置成基于从锁相环或振荡器产生的输出而输出第一时钟信号;多路复用电路,所述多路复用电路被配置成输出所述第一时钟信号和第二时钟信号中的一个;第一时钟分频电路,所述第一时钟分频电路被配置成对所述多路复用电路的输出执行第一分频操作以产生第三时钟信号;速止电路,所述速止电路被配置成选择性地停止第三时钟信号的脉冲以产生第四时钟信号;第二时钟分频电路,所述第二时钟分频电路被配置成对所述速止电路的输出执行第二分频操作以产生第五时钟信号;以及第一时钟门控电路,所述第一时钟门控电路被配置成选择性地输出所述第五时钟信号。

技术特征:

1.一种时钟门控组件,其包括:

2.根据权利要求1所述的时钟门控组件,其特征在于,

3.一种时钟多路复用器组件,其包括:

4.根据权利要求3所述的时钟多路复用器组件,其特征在于,所述时钟控制电路被配置成响应于所述请求信号而将确认信号提供到所述信道管理电路。

5.根据权利要求3所述的时钟多路复用器组件,其特征在于,所述时钟电路包含有限状态机,所述有限状态机被配置成将所述请求信号输出到提供所述第一时钟信号的第一时钟源以及提供所述第二时钟信号的第二时钟源。

6.一种时钟分频组件,其包括:

7.根据权利要求6所述的时钟分频组件,其特征在于,所述时钟控制电路包括:

技术总结

本发明提供一种时钟门控组件、一种时钟多路复用器组件以及一种时钟分频组件。片上系统包含多个知识产权块和时钟管理单元,时钟管理单元被配置成对知识产权块中的至少一个执行时钟门控。知识产权块和时钟管理单元使用完全握手方法彼此连接。完整握手方法可以包含以下项中的至少一个:知识产权块将请求信号发送到时钟管理单元以开始提供时钟信号或停止提供时钟信号;以及响应于接收请求信号,时钟管理单元将确认信号发送到对应知识产权块。本发明的片上系统的消耗功率低,且本发明的驱动片上系统的方法可以防止片上系统消耗太多功率。

技术研发人员:李宰坤,金硪灿,宋陈煜,李栽荣,崔然植

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!