面向FPGA平台的NANDFlashBCH纠检错模块的制作方法

本发明涉及计算机存储器,具体涉及一种面向fpga平台的nand flashbch纠检错模块。

背景技术:

1、随着移动终端的普及和云技术的快速发展,对大容量数据存储设备的需求越来越大。nand flash是目前应用最广的一种非易失性存储介质,凭借其较高的存储密度,较低的成本,极大的容量,广泛地应用于u盘、固态硬盘和数码相机等电子产品中。随着技术的更新迭代,越来越多的计算模块和soc ip也集成了nand flash芯片作为大容量存储单元。

2、在航天型号任务中,系统级的智能和自主能力提升依赖于算法的更新和应用,这也需要单机计算平台具备高算力,大数据量,快速存储的要求。nand flash以其快速读写能力和存储容量大等特征,也成为满足航天智能计算的理想存储介质,未来的深空探测/空间自主感知领域需要面对更加恶劣的辐射的工作环境,对存储数据的可靠性和持续性有着更高的要求。

3、由于nand flash结构的特殊性,在对其进行擦除和写入操作时,可能产生数据位的翻转,从而造成数据存储的错误,影响用户程序运行。传统的冗余备份策略一方面需要更多的存储芯片,增加设备成本、体积和功耗,另一方面同一规格,批次和制程存储芯片,容易产生相同的翻转状态,造成多份数据同时失真,使得单纯依靠多备份存储的方式也存在一定隐患。在对空间目标的感知和探测过程中,nand flash需要引入自身的错误校验机制,以增强其抵抗空间环境效应的能力。传统的单bit纠错能力,不能满足嵌入式cpu/gpu/dsp对数据存储的可靠性需求。现有的研究多是从算法级对nand flash纠检错进行设计,并未进行逻辑实现层面的探究。实际的工程化应用中软件实现各种编码/解码的效率较低,亟需探索利用硬件并行的bch算法实现。

4、以某nand flash为例,其具备1gb的存储能力,读写速度快。但其手册要求每540kb具备4位的ecc(error correction code)功能。现有的国产和进口该型号nand flash只包含对数据存取的接口,并没有独立的纠错功能,因此其ecc功能的实现依赖于额外的软件或硬件实现。基础的ecc算法具备1位的纠错和2位的检错能力,并不能满足该款存储芯片的纠错需求,而且对每个字节都添加ecc编解码的方式占用大量的额外存储空间。因此,需要选择具备更高性能的纠错算法来完成。高端的信道纠错算法如ldpc等具备较高的软件和硬件开发难度,且尽管纠错能力显著,其需要的校验码数量也非常多,逻辑资源占用较多。在每页只有4096字节+224字节的基础上,额外预留的224字节不能存储大量的ldpc算法的校验位。bch码是线性循环分组码的一种,1959年由bose,chaudhuri,hocqueenghem三人提出,具有编解码简单,纠错能力强,构造方便等特点,适合对中短码长的数据进行纠错。bch码是一种重要的纠错码,常用于存储器、通信和数字电视等领域中,可以有效地纠正数据中的一定数量的错误。在nand flash存储器中,由于存在擦除操作,可能会导致数据位翻转,因此需要使用bch码进行纠错。在fpga芯片中实现bch码纠错算法,需要设计合适的电路结构和算法实现。同时,还需要考虑到fpga芯片的资源限制和性能要求,以实现高效、可靠的纠错功能。因此,相关技术领域的设计还十分缺乏。

技术实现思路

1、有鉴于此,本发明提供了一种面向fpga平台的nand flash bch纠检错模块,能够部署在fpga等可编程逻辑电路上,且存储占用小、并行化程度高、数据吞吐率高以及逻辑资源占用少。

2、为实现上述目的,本发明技术方案如下:

3、一种面向fpga平台的nand flash bch纠检错模块,包括编码器和译码器,其中编码负责将指定存储长度的数据位除以bch码的生成多项式,得到的余数为数据的校验码;编码器实现电路中,m为编码器并行度,每次输入m位数据,输出编码多项式的高m位数据,m+n为信息码编码多项式的长度;在完成数据输入后,得到余式为校验位数据;对于一个页来说,其数据存储区域为索引0到4095的存储字节,4096位至4105位的十个字节存储块信息,其校验位存储在4106开头后的地址空间中。

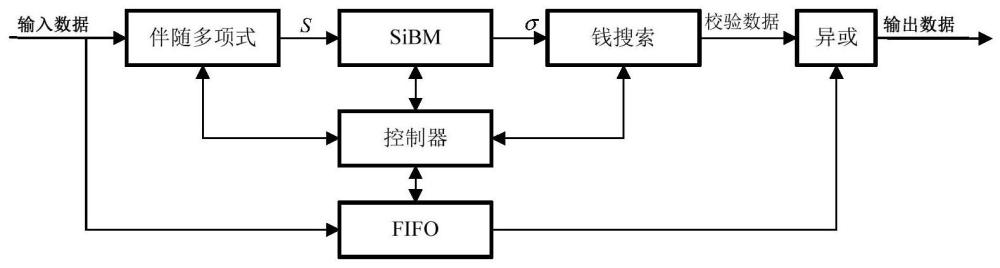

4、译码器包括伴随多项式计算、错误位置多项式计算以及钱搜索模块,其中伴随多项式计算用于检测数据是否存在位翻转的错误;错误位置多项式计算采用sibm算法,用于从伴随多项式确定错误位置多项式的系数;钱搜索将错误位置多项式根的求解转化为对本原多项式根的幂的验证。

5、其中,模块系统部署架构中,整个soc平台负责对包括nand flash和ddr存储单元的管理和交互;其中,ps/dsp单元发起对数据的请求和写入操作,pl负责中间接口的转换和存储器访问时序的生成;pl形成的接口模块不仅需要在生成访问时序的同时,运行bch算法的编解码运算;

6、在写入数据过程中,ps端以axi总线的时序生成对数据的读写操作,首先经过axi转emif时序的中转单元,同步后的emif时序下地址,数据和读写信号被发送到接口模块,用于对nand flash的控制,写入数据过程中,接口模块将写入的数据存储到写fifo中,然后向指令地址发送读指令,启动数据的写入;算法单元读fifo中的数据,进行编码,并将生成写入时序将数据和校验码写入到nand flash的页内地址;

7、在读出数据过程中,接口模块首先接收读的地址,然后指令地址收到读指令,算法模块生成指定页地址内数据的nand flash读时序,将读到的数据先进行译码,然后将译码后的校验数据与读取数据分别存储到校验fifo和读fifo中;当完成一个页的读取和译码后,ps/dsp端对数据地址执行4096个字节的读操作,接口模块将校验fifo和读fifo的数据异或后输出;

8、在执行过程,首先将数据通过编码器生成校验码,与原始数据一起放入nandflash的存储区。

9、其中,所述译码器中还配置有控制模块和fifo模块。

10、其中,错误位置多项式计算模块中,采用简化的无逆bm算法求解错误位置多项式;采用fpga对于每个处理模块求解错误位置多项式,pe单元完成迭代过程中数据的更新。

11、其中,m位并行伴随多项式的计算通过并行的循环乘加实现。

12、有益效果:

13、1.本发明中基于fpga的bch编解码模块,用于实现nand flash数据的纠检错,该模块具备完整的编码和解码框架,便于集成到对应的嵌入式平台和存储系统中,相比于传统的多重备份、ldpc/ecc编/解码等策略,具有存储占用小,并行化程度高,数据吞吐率高,逻辑资源占用少等特点,可以部署在fpga等可编程逻辑电路上,解决空间嵌入式环境中大容量数据的可靠存储问题。

14、2.本发明采用并行编码和解码器结构设计,对编码系统和解码系统的数据处理工程并行化,提高了系统吞吐率,实现了数据快速存取。

15、3.本发明实现了模块化的伴随多项式、sibm和关键方程求解架构,简化了实现途径和资源使用,并可以按照资源占用情况进行裁剪和复用。

- 还没有人留言评论。精彩留言会获得点赞!