移位寄存器、像素驱动电路及显示装置的制作方法

本公开属于显示,具体涉及一种移位寄存器、像素驱动电路和显示装置。

背景技术:

1、目前的阵列基板栅极驱动(gate driver on array)电路主要存在的问题包括:1、薄膜晶体管(thin film transistor,tft)的宽长比比较大,导致goa电路的面积比较大,不利于窄边框产品的设计开发;2、goa电路的输出信号的稳定性差,需要复杂的降噪电路,增加了产品的不良率。

2、基于上述问题,发明人提出了一种新型goa电路,其包括的tft数量少,且采用相同的宽长比设计,可以大幅降低tft的占用面积,从而减小goa面积,除此之外,本公开中的goa电路仅需上一行触发本行输出,不需要进行复位及复杂的降噪设计,简化了制作工艺,降低了不良率,增加了稳定性。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一,提供一种移位寄存器、像素驱动电路及显示装置。

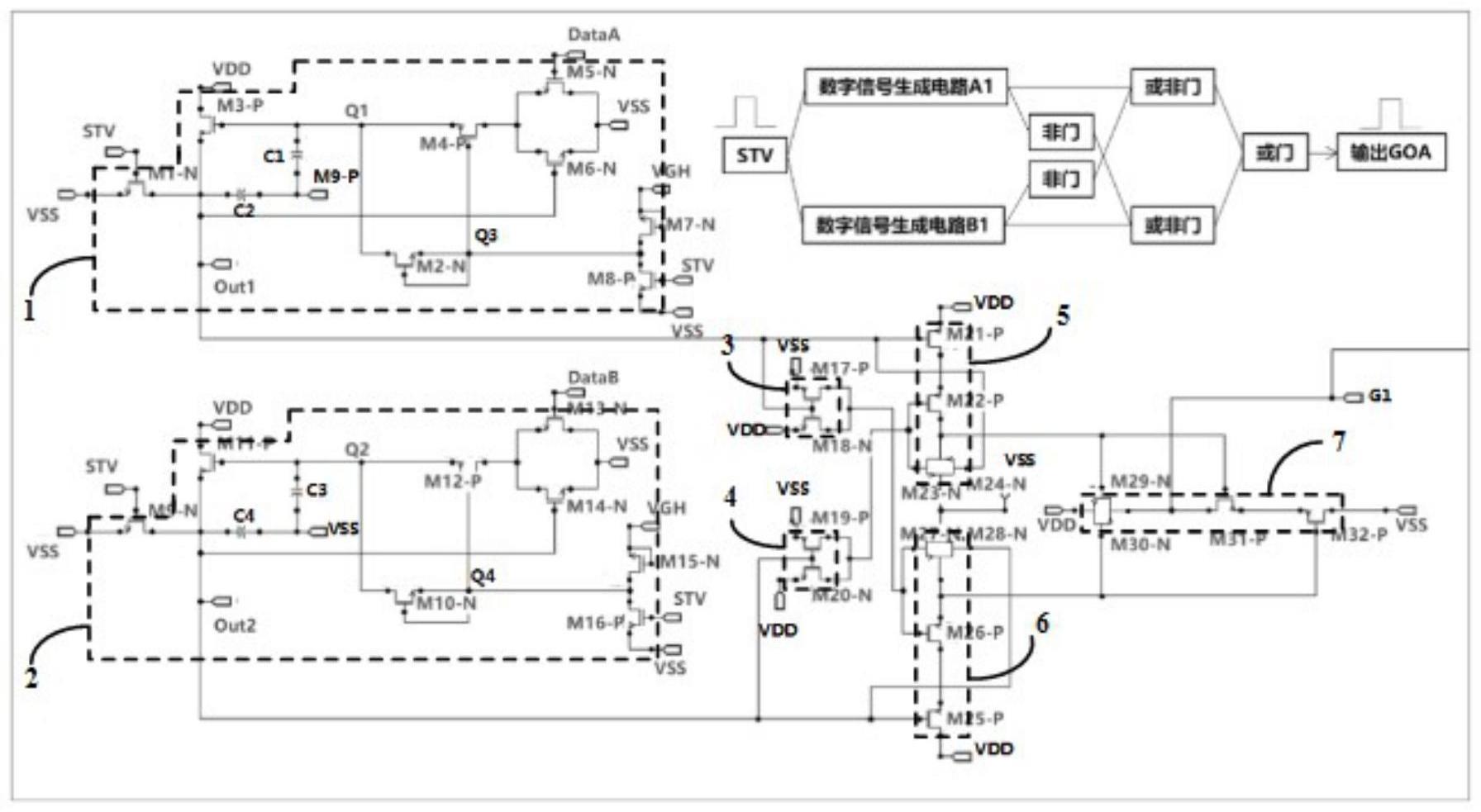

2、第一方面,本公开实施例提供了一种移位寄存器,其包括:

3、第一信号生成子电路,其具有输入端和输出端,所述第一信号生成子电路被配置为响应于所述第一输入信号,将第一电平信号或者第二电平信号传输至输出端;

4、第二信号生成子电路,其具有输入端和输出端,所述第二信号生成子电路被配置为响应于所述第一输入信号,将第一电平信号或者第二电平信号传输至输出端;所述第一信号生成子电路的输出信号和所述第二信号生成子电路的输出信号的有效电平相同,均为第一电平信号或者第二电平信号,且所述第二信号生成子电路的输出信号的有效电平的起始时刻与所述第一信号生成子电路的输出信号的有效电平的起始时刻相差预设时长;

5、第一非门,其具有输入端和输出端,所述第一非门的输入端连接所述第一信号生成子电路的输出端;

6、第二非门,其具有输入端和输出端,所述第二非门的输入端连接所述第二信号生成子电路的输出端;所述第二非门与所述第一非门的结构相同;

7、第一逻辑门,其具有第一输入端、第二输入端和输出端,所述第一输入端连接所述第一信号生成子电路的输出端,所述第二输入端连接所述第二非门的输出端;所述第一逻辑门为或非门或者与门;

8、第二逻辑门,其具有第一输入端、第二输入端和输出端,所述第一输入端连接所述第一非门的输出端,所述第二输入端连接所述第二信号生成子电路的输出端;所述第二逻辑门与所述第一逻辑门成镜像对称;

9、第三逻辑门,其具有第一输入端、第二输入端和输出端,所述第一输入端连接所述第一逻辑门的输出端,所述第二输入端连接所述第二逻辑门的输出端;所述第三逻辑门为或门或者或非门。

10、优选的是,所述第一信号生成子电路包括:

11、第一输出子电路,被配置为响应于所述第一输入信号,将第二电平信号传输至输出端输出;

12、第二输出子电路,被配置为响应于第一节点的电压,将第一电平信号传输至输出端输出;

13、第一存储子电路,被配置为根据所述第一节点电压和所述第二电平信号,控制所述第二输出子电路的工作时长;

14、第二存储子电路,被配置为根据所述输出端的电压和所述第二电平信号的电压,控制所述第一输出子电路的工作时长;

15、第一控制子电路,被配置为响应于第二节点电压和第二输入信号的电压,控制第一节点的充电或者放电的速度;或者,所述第一控制子电路,被配置为响应于第二节点电压、第二输入信号的电压和所述输出端的电压,控制第一节点充电或者放电的速度;

16、第二控制子电路,被配置为响应于第一输入信号的电压,控制第一节点电压的充电或者放电速度;

17、所述第一节点为所述第一存储子电路、第二输出子电路、第一控制子电路和第二控制子电路的连接节点;所述第二节点为所述第一控制子电路和所述第二控制子电路的连接节点。

18、优选的是,所述第一输出子电路包括第一晶体管,所述第一晶体管的控制极连接所述第一输入信号端,第一极连接所述第二电平信号端,第二极连接所述第一信号生成子电路的输出端。

19、优选的是,所述第二输出子电路包括第三晶体管,所述第三晶体管的控制极连接所述第一节点,第一极连接所述第一电平信号端,第二极连接所述第一信号生成子电路的输出端。

20、优选的是,所述第一存储子电路包括第一存储电容,所述第一存储电容的一极连接所述第一信号生成子电路的输出端,另一极连接所述第二电平信号端。

21、优选的是,所述第二存储子电路包括第二存储电容,所述第二存储电容的一极连接所述第一节点,另一极连接所述第二电平信号端。

22、优选的是,所述第一控制子电路包括第二晶体管、第四晶体管、第五晶体管、第七晶体管和第八晶体管,所述第二晶体管的控制极和第二极均连接所述第二节点,所述第二晶体管的第一极连接所述第一节点,所述第四晶体管的控制极连接所述第二节点,所述第四晶体管第一极连接所述第一节点,所述第四晶体管的第二极连接所述第五晶体管的第一极,所述第五晶体管的控制极连接所述第二输入信号,所述第五晶体管的第二极连接所述第二电平信号端,所述第七晶体管的控制极和第一极均连接第三电平信号,所述第七晶体管的第二极连接所述第八晶体管的第一极,所述第八晶体管的控制极连接所述第一输入信号端,所述第八晶体管的第二极连接所述第二电平信号端。

23、优选的是,所述第一控制子电路还包括:第六晶体管;

24、所述第六晶体管的控制极连接所述第一信号生成子电路的输出端,第一极连接所述第四晶体管的第二极和所述第五晶体管的第一极,第二极连接所述第二电平信号端。

25、优选的是,所述第二信号生成子电路包括:

26、第三输出子电路,被配置为响应于所述第一输入信号,将第二电平信号传输至输出端输出;

27、第四输出子电路,被配置为响应于第三节点的电压,将第一电平信号传输至所述第二信号生成子电路的输出端输出;

28、第三存储子电路,被配置为根据所述第三节点电压和所述第二电平信号,控制所述第四输出子电路的工作时长;

29、第四存储子电路,被配置为根据所述第二信号生成子电路的输出端的电压和所述第二电平信号的电压,控制所述第三输出子电路的工作时长;

30、第三控制子电路,被配置为响应于第四节点电压和第三输入信号的电压,控制第三节点的充电或者放电的速度;或者,所述第三控制子电路,被配置为响应于第四节点电压、第三输入信号的电压和所述第二信号生成子电路的输出端的电压,控制第三节点充电或者放电的速度;

31、第四控制子电路,被配置为响应于第一输入信号的电压,控制第三节点电压的充电或者放电速度;

32、所述第三节点为所述第三存储子电路、第四输出子电路、第三控制子电路和第四控制子电路的连接节点;所述第二节点为所述第三控制子电路和所述第四控制子电路的连接节点。

33、优选的是,所述第三输出子电路包括第九晶体管,所述第九晶体管的控制极连接所述第一输入信号端,第一极连接所述第二电平信号端,第二极连接所述的第二信号生成子电路的输出端。

34、优选的是,所述第四输出子电路包括第十一晶体管,所述第十一晶体管的控制极连接所述第一节点,第一极连接所述第一电平信号端,第二极连接所述的第二信号生成子电路的输出端。

35、优选的是,所述第三存储子电路包括第三存储电容,所述第三存储电容的一极连接所述的第二信号生成子电路的输出端,另一极连接所述第二电平信号端。

36、优选的是,所述第四存储子电路包括第四存储电容,所述第四存储电容的一极连接所述第一节点,另一极连接所述第二电平信号端。

37、优选的是,所述第二控制子电路包括第十晶体管、第十二晶体管、第十三晶体管、第十五晶体管和第十六晶体管,所述第十晶体管的控制极和第二极均连接所述第二节点,所述第十晶体管的第一极连接所述第一节点,所述第十二晶体管的控制极连接所述第二节点,所述第十二晶体管第一极连接所述第一节点,所述第十二晶体管的第二极连接所述第十三晶体管的第一极,所述第十三晶体管的控制极连接所述第三输入信号,所述第十三晶体管的第二极连接所述第二电平信号端,所述第十五晶体管的控制极和第一极均连接第三电平信号,所述第十五晶体管的第二极连接所述第十六晶体管的第一极,所述第十六晶体管的控制极连接所述第一输入信号端,所述第十六晶体管的第二极连接所述第二电平信号端。

38、优选的是,所述第三控制子电路还包括:第十四晶体管;

39、所述第十四晶体管的控制极连接所述的第二信号生成子电路的输出端,第一极连接所述第十二晶体管的第二极和所述第十三晶体管的第一极,第二极连接所述第二电平信号端。

40、优选的是,所述第一非门包括第十七晶体管和第十八晶体管;

41、所述第十七晶体管的控制极与所述第十八晶体管的控制极的连接节点为所述第一非门的输入端,所述第十七晶体管的第二极与所述第十八晶体管的第二极的连接节点为所述第一非门的输出端;

42、所述第十七晶体管的第一极连接所述第一电平信号端;

43、所述第十八晶体管的第一极连接所述第二电平信号端;

44、所述第十七晶体管和所述第十八晶体管的开关特性相反。

45、优选的是,所述第二非门包括第十九晶体管和第二十晶体管;

46、所述第十九晶体管的控制极与所述第二十晶体管的控制极的连接节点为所述第二非门的输入端,所述第十九晶体管的第二极与所述第二十晶体管的第二极的连接节点为所述第二非门的输出端;

47、所述第十九晶体管的第一极连接所述第一电平信号端;

48、所述第二十晶体管的第一极连接所述第二电平信号端;

49、所述第十九晶体管和所述第二十晶体管的开关特性相反。

50、优选的是,所述第一逻辑门包括第二十一晶体管、第二十二晶体管、第二十三晶体管和第二十四晶体管;

51、所述第二十一晶体管的控制极与所述第二十四晶体管的控制极的连接节点为所述第一逻辑门的第一输入端,所述第二十二晶体管的控制极与所述第二十三晶体管的控制极的连接节点为所述第一逻辑门的第二输入端,所述第二十二晶体管的第二极、所述第二十三晶体管的第一极与所述第二十四晶体管的第一极的连接节点为所述第一逻辑门的输出端;

52、所述第二十一晶体管的第一极连接所述第一电平信号端,第二极连接所述第二十二晶体管的第一极;

53、所述第二十二晶体管的第一极连接所述第二十一晶体管的第二极;

54、所述第二十三晶体管的第二极连接所述第二电平信号端;

55、所述第二十四晶体管的第二极连接所述第二电平信号端;

56、所述第二十一晶体管和所述第二十二晶体管的开关特性相同,所述第二十三晶体管和所述第二十四晶体管的开关特性相同,所述第二十一晶体管和所述第二十三晶体管的开关特性相反。

57、优选的是,所述第二逻辑门包括第二十五晶体管、第二十六晶体管、第二十七晶体管和第二十八晶体管;

58、所述第二十六晶体管的控制极与所述第二十七晶体管的控制极的连接节点为所述第二逻辑门的第一输入端,所述第二十五晶体管的控制极与所述第二十八晶体管的控制极的连接节点为所述第二逻辑门的第二输入端,所述第二十六晶体管的第一极、所述第二十七晶体管的第二极与所述第二十八晶体管的第二极的连接节点为所述第二逻辑门的输出端;

59、所述第二十五晶体管的第一极连接所述第二十六晶体管的第二极,第二极连接所述第一电平信号端;

60、所述第二十六晶体管的第二极连接所述第二十五晶体管的第一极;

61、所述第二十七晶体管的第一极连接所述第二电平信号端;

62、所述第二十八晶体管的第一极连接所述第二电平信号端;

63、所述第二十五晶体管和所述第二十六晶体管的开关特性与所述第二十一晶体管的开关特性相同,所述第二十七晶体管和所述第二十八晶体管的开关特性与所述第二十三晶体管的开关特性相同,所述第二十五晶体管和所述第二十七晶体管的开关特性相反。

64、优选的是,所述第三逻辑门包括第二十九晶体管、第三十晶体管、第三十一晶体管和第三十二晶体管;

65、所述第二十九晶体管的控制极与所述第三十一晶体管的控制极的连接节点为所述第三逻辑门的第一输入端,所述第三十晶体管的控制极与所述第三十二晶体管的控制极的连接节点为所述第三逻辑门的第二输入端,所述第二十九晶体管的第二极、所述第三十晶体管的第二极与所述第三十一晶体管的第一极的连接节点为所述第三逻辑门的输出端;

66、所述第二十九晶体管的第一极连接所述第一电平信号端;

67、所述第三十晶体管的第一极连接所述第一电平信号端;

68、所述第三十一晶体管的第二极连接所述第三十二晶体管的第一极;

69、所述第三十二晶体管的第一极连接所述第三十一晶体管的第二极,第二极连接所述第二电平信号端;

70、所述第二十九晶体管和所述第三十晶体管的开关特性相同,所述第三十一晶体管和所述第三十二晶体管开关特性相同,所述第二十九晶体管和所述第三十一晶体管的开关特性相反。

71、第二方面,本公开实施例提供了一种像素驱动电路,其中,所述像素驱动电路包括:级联的多个上述的移位寄存器;

72、本级所述移位寄存器的信号输入端连接上一级所述移位寄存器的信号输出端。

73、第三方面,本公开实施例提供了一种显示装置,其中,所述显示装置包括上述的像素驱动电路。

- 还没有人留言评论。精彩留言会获得点赞!