集成电路时序违例修正方法、装置、电子设备及存储介质与流程

本技术涉及电子设计技术,尤其涉及一种集成电路时序违例修正方法、装置、电子设备及存储介质。

背景技术:

1、在集成电路领域中,各逻辑单元的位置及信号路径应满足预设的时序规则,但是在设计电路过程中常出现时序违例问题。时序违例是指信号到达寄存器或触发器时的时序要求没有得到满足。例如,在时钟正确的采样上升沿之前或者之后到达,导致采样时钟没有准确地采样信号。典型的时序违例通常分为两种情况:setup违例和hold违例。setup违例是指数据信号在采样时钟上升沿到达之前已经发生变化,导致采样到的数据不正确。hold违例是指数据信号在时钟上升沿到达之后仍然在变化,导致采样到的数据不稳定,进而可能导致数据损坏。

2、针对于芯片集成规模越来越大,自然会导致芯片后端设计中单元密度很高,特别是局部区域已经摆满单元,几乎没有空余的位置空间,此时若有时序违例,则存在时序修复特别困难的情况。这是因为目前的时序修复工具在修复setup或者hold的时候通常是通过在数据路径上插入缓冲单元或者是更换单元尺寸来增加或者减小单元延时进而达到修复setup违例或者hold违例。但是随着现在芯片的集成度越来越高,有时在高密度的设计中,如果工程师对某一条路径插入缓冲单元或者是更换单元尺寸来改变单元时,工具在一定的搜索范围内找不到足够的位置空间,就会导致工具在该条路径上存在无法修复时序的情况,进而使芯片无法正常工作。综上,当前的集成电路时序违例修正方法,需涉及元件上的替换、删除或增加,由此在高密度集成芯片的应用场景下,物理实现上的可行性不高,且时序违例修正的效率不好。因此需要一种集成电路时序违例修正方法,以提升时序违例修正的效率和实用性。

技术实现思路

1、本技术提供一种集成电路时序违例修正方法、装置、电子设备及存储介质,用以解决集成电路时序违例修正效率不高、实用性不好的问题。

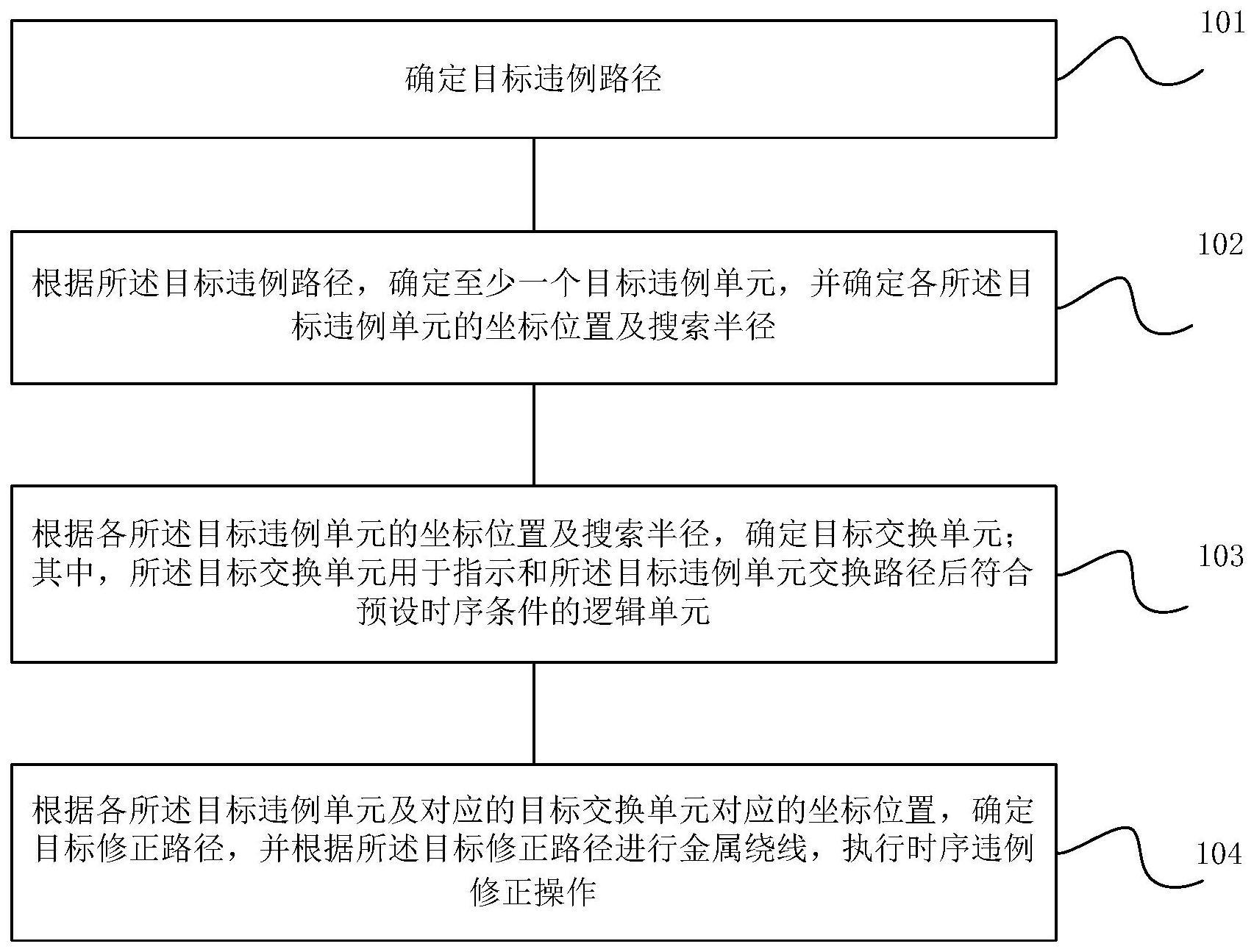

2、第一方面,本技术提供一种集成电路时序违例修正方法,方法包括:

3、确定目标违例路径;

4、根据目标违例路径,确定至少一个目标违例单元,并确定各目标违例单元的坐标位置及搜索半径;

5、根据各目标违例单元的坐标位置及搜索半径,确定目标交换单元;

6、其中,目标交换单元用于指示和目标违例单元交换路径后符合预设时序条件的逻辑单元;

7、根据各目标违例单元及对应的目标交换单元对应的坐标位置,确定目标修正路径,并根据目标修正路径进行金属绕线,执行时序违例修正操作。

8、作为一种可选的实施方式,根据目标违例路径,确定至少一个目标违例单元,包括:

9、根据目标违例路径,确定第一端点和第二端点,并根据第一端点和第二端点,确定搜索路径;

10、其中,第一端点用于指示遍历搜索目标违例单元的搜索路径起点,第二端点用于指示遍历搜索目标违例单元的搜索路径终点;

11、根据搜索路径,依次确定出各目标违例单元。

12、作为一种可选的实施方式,目标违例路径至少包括第一违例路径和第二违例路径,第一违例路径和第二违例路径存在至少一个交点;

13、根据目标违例路径,确定第一端点和第二端点,并根据第一端点和第二端点,确定搜索路径,包括:

14、确定第一违例路径和第二违例路径的时序违例参数,并根据时序违例参数,确定搜索顺序和/或搜索速度;

15、其中,时序违例参数用于指示对应的目标违例路径的时序违例程度;

16、将第一违例路径和第二违例路径靠近集成电路信号终点一侧的端点确定为对应的第一端点;

17、根据第一端点,以及搜索顺序和/或搜索速度,对第一违例路径和第二违例路径进行预搜索,确定出第一违例路径和第二违例路径的第二端点,并确定出搜索路径;

18、以及,根据搜索路径,依次确定出各目标违例单元之后,方法还包括:

19、若存在至少一个目标违例单元同时归属于第一违例路径和第二违例路径,则根据时序违例参数,确定出该目标违例单元实际归属的违例路径。

20、作为一种可选的实施方式,根据各目标违例单元的坐标位置及搜索半径,确定目标交换单元,包括:

21、根据各目标违例单元的坐标位置及搜索半径,确定与各目标违例单元距离不大于搜索半径的所有预处理交换单元;

22、其中,预处理交换单元与对应的目标违例单元具备相同的功能逻辑,且阈值电压或驱动条件不同;

23、计算对应于各目标违例单元的各预处理交换单元的时序违例参数,并根据时序违例参数,去除不符合预设时序条件的各预处理交换单元;

24、将剩余预处理交换单元确定为目标交换单元。

25、作为一种可选的实施方式,时序违例参数包括第一违例参数和第二违例参数,预设时序条件包括:第一违例参数和第二违例参数均大于第一数值;

26、其中,第一违例参数和第二违例参数用于指示各目标违例单元与对应的各预处理交换单元交换后的两条路径的时序违例值;

27、以及,将剩余预处理交换单元确定为目标交换单元,包括:

28、根据剩余预处理交换单元对应的时序违例值以及坐标位置,确定剩余预处理交换单元的权重值;

29、根据剩余预处理交换单元对应的权重值,将权重值高于预设权重阈值的剩余预处理交换单元确定为目标交换单元,并根据权重值确定交换顺序。

30、第二方面,本技术提供一种集成电路时序违例修正装置,装置包括:

31、获取模块,用于确定目标违例路径;

32、处理模块,用于根据目标违例路径,确定至少一个目标违例单元,并确定各目标违例单元的坐标位置及搜索半径;

33、处理模块,还用于根据各目标违例单元的坐标位置及搜索半径,确定目标交换单元;

34、其中,目标交换单元用于指示和目标违例单元交换路径后符合预设时序条件的逻辑单元;

35、处理模块,还用于根据各目标违例单元及对应的目标交换单元对应的坐标位置,确定目标修正路径,并根据目标修正路径进行金属绕线,执行时序违例修正操作。

36、作为一种可选的实施方式,处理模块根据目标违例路径,确定至少一个目标违例单元的具体方式,包括:

37、根据目标违例路径,确定第一端点和第二端点,并根据第一端点和第二端点,确定搜索路径;

38、其中,第一端点用于指示遍历搜索目标违例单元的搜索路径起点,第二端点用于指示遍历搜索目标违例单元的搜索路径终点;

39、根据搜索路径,依次确定出各目标违例单元。

40、作为一种可选的实施方式,目标违例路径至少包括第一违例路径和第二违例路径,第一违例路径和第二违例路径存在至少一个交点;

41、处理模块根据目标违例路径,确定第一端点和第二端点,并根据第一端点和第二端点,确定搜索路径的具体方式,包括:

42、确定第一违例路径和第二违例路径的时序违例参数,并根据时序违例参数,确定搜索顺序和/或搜索速度;

43、其中,时序违例参数用于指示对应的目标违例路径的时序违例程度;

44、将第一违例路径和第二违例路径靠近集成电路信号终点一侧的端点确定为对应的第一端点;

45、根据第一端点,以及搜索顺序和/或搜索速度,对第一违例路径和第二违例路径进行预搜索,确定出第一违例路径和第二违例路径的第二端点,并确定出搜索路径;

46、以及,处理模块还用于在根据搜索路径,依次确定出各目标违例单元之后,

47、若存在至少一个目标违例单元同时归属于第一违例路径和第二违例路径,则根据时序违例参数,确定出该目标违例单元实际归属的违例路径。

48、作为一种可选的实施方式,处理模块根据各目标违例单元的坐标位置及搜索半径,确定目标交换单元的具体方式,包括:

49、根据各目标违例单元的坐标位置及搜索半径,确定与各目标违例单元距离不大于搜索半径的所有预处理交换单元;

50、其中,预处理交换单元与对应的目标违例单元具备相同的功能逻辑,且阈值电压或驱动条件不同;

51、计算对应于各目标违例单元的各预处理交换单元的时序违例参数,并根据时序违例参数,去除不符合预设时序条件的各预处理交换单元;

52、将剩余预处理交换单元确定为目标交换单元。

53、作为一种可选的实施方式,时序违例参数包括第一违例参数和第二违例参数,预设时序条件包括:第一违例参数和第二违例参数均大于第一数值;

54、其中,第一违例参数和第二违例参数用于指示各目标违例单元与对应的各预处理交换单元交换后的两条路径的时序违例值;

55、以及,处理模块将剩余预处理交换单元确定为目标交换单元的具体方式,包括:

56、根据剩余预处理交换单元对应的时序违例值以及坐标位置,确定剩余预处理交换单元的权重值;

57、根据剩余预处理交换单元对应的权重值,将权重值高于预设权重阈值的剩余预处理交换单元确定为目标交换单元,并根据权重值确定交换顺序。

58、第三方面,本技术提供一种电子设备,包括:

59、至少一个处理器;以及

60、与至少一个处理器通信连接的存储器;其中,

61、存储器存储有可被至少一个处理器执行的指令,指令被至少一个处理器执行,以使至少一个处理器能够执行如第一方面的方法。

62、第四方面,本技术提供一种计算机可读存储介质,计算机可读存储介质中存储有计算机执行指令,计算机执行指令被处理器执行时用于实现如第一方面的方法。

63、本技术提供的集成电路时序违例修正方法、装置、电子设备及存储介质,通过确定目标违例路径,可确定出目标违例路径上的至少一个目标违例单元,由此可根据目标违例单元的坐标位置及搜索半径确定交换后符合预设时序条件的逻辑单元作为一个或多个目标交换单元,并进一步根据确定出的目标交换单元,与目标违例单元的路径进行交换并重新绕线,在不改变集成电路上各现有逻辑单元坐标位置,且不增添或删除逻辑单元的条件下,实现了时序违例修正操作,优化了信号路径,由此提升了集成电路时序违例修正的效率和实用性,该方法在高密度集成电路的时序违例修正过程中简化了修正流程,且提升了修正结果的准确性。

- 还没有人留言评论。精彩留言会获得点赞!