面向后量子加密Kyber方案的NTT多项式乘法器的硬件电路

本发明涉及加密硬件电路设计,具体的说是一种面向后量子加密kyber方案的ntt多项式乘法器的硬件电路。

背景技术:

1、随着量子计算机的建成和使用,公钥加密算法例如rsa和椭圆曲线(ellipticcurve cryptography,ecc)会被基于shor的量子算法破解。此外,对称密码算法和哈希算法也会被基于grover的量子算法破解。为了解决数据安全面临威胁的问题,nist正在进行后量子加密算法的筛选。在2022年7月确定了四个将被标准化的算法和另外的四个算法作为第四轮的候选算法。

2、密钥封装机制crystals-kyber也可简称为kyber,作为将要被标准化的公钥加密算法之一,其是基于理想格中模上错误学习问题(module learning with errors,mlwe)。mlwe的基本代数结构是b=a*s+e,其中,b、s和e都是k维多项式向量,a是k×k维的多项式矩阵,k是kyber算法中安全级别。通过对软件部分的分析,发现整个加密算法中最耗时和最关键的部分是多项式乘法,即是基本的代数结构部分,因此对其进行加速意义重大。

3、早期,只有少量研究者对kyber算法进行了粗略的硬件加速。而近两年,为了优化关键部分,现在有些许研究聚焦于对多项式乘法的加速。部分研究的访存采用乒乓操作来实现,虽然有效解决了访存冲突的问题和获得了双倍的带宽,但是该操作需要消耗大量的存储资源。因此,另一部分研究的访存是基于伪双口的寻址,但是在硬件实现中由于访存冲突的问题,仍然会消耗大量的硬件资源。当然,还有一部分不使用bram对中间数据进行存储,但是设计的架构会消耗大量的硬件资源来实现。因此,设计一个有效的访存机制是非常重要的。

4、除此之外,优化模加、模减、模乘以及整体架构也可以提高多项式乘法器的资源效率。目前,有的研究虽然在ntt过程取得了较好的资源效率,但是多项式乘法过程消耗了较多的周期,进而影响整体的资源效率。因此,设计一个资源高效的多项式乘法器也是非常重要的。

技术实现思路

1、本发明为克服现有技术的不足之处,提出了一种面向后量子加密kyber方案的ntt多项式乘法器的硬件电路,以期能提升多项式乘法器的性能,加快计算速度,尽量减少资源消耗,缩短时间周期。

2、为达到上述发明目的,本发明所采用的技术方案如下:

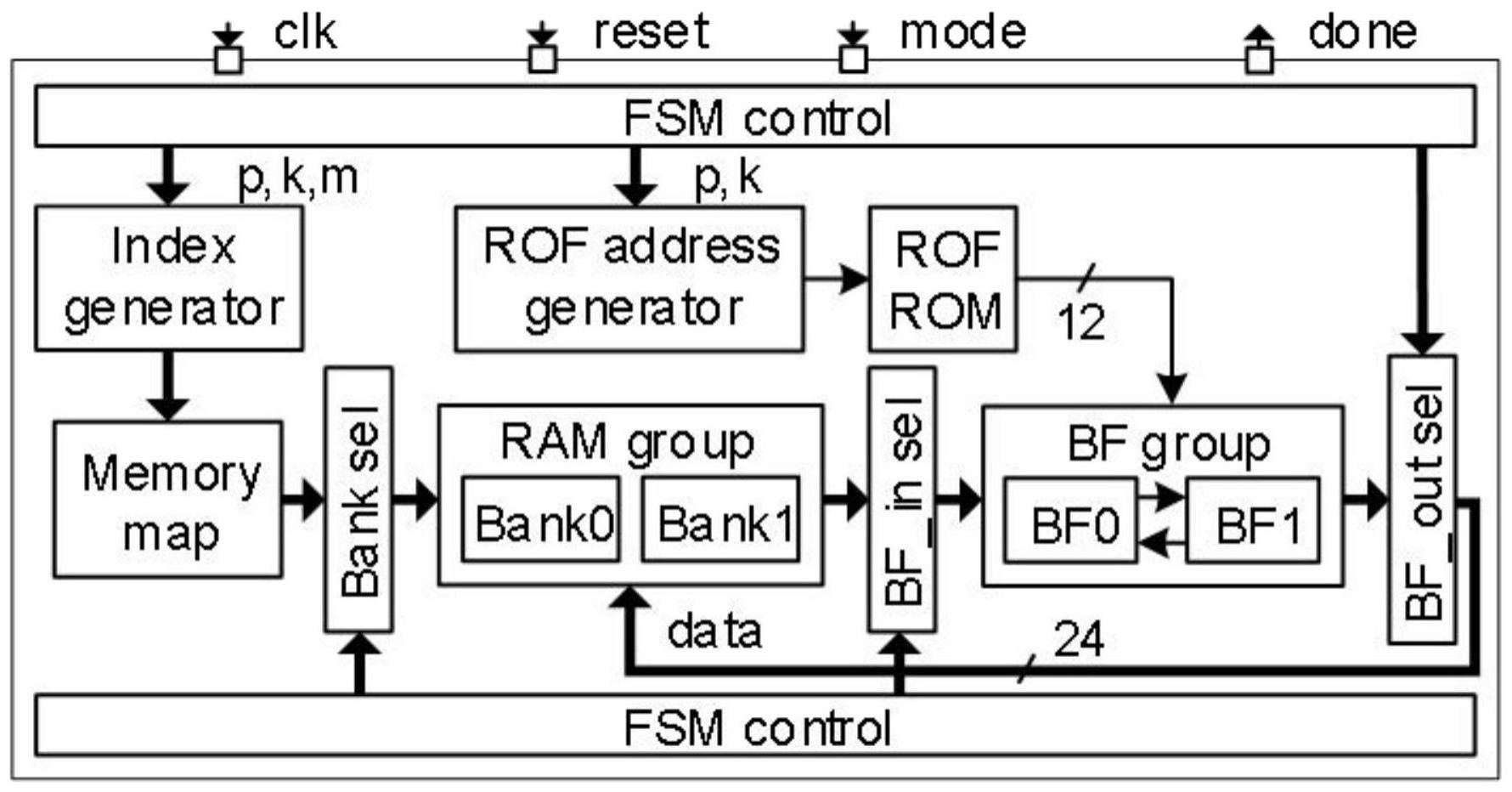

3、本发明一种面向后量子加密kyber方案的ntt多项式乘法器的硬件电路的特点在于,包括:状态机控制模块、索引生成模块、旋转因子地址生成模块、存储映射模块、bank选择模块、ram组、旋转因子rom、蝶形输入选择模块、蝶形输出选择模块、蝶形模块,其中,所述蝶形模块包括:第一蝶形单元、第二蝶形单元;每个蝶形单元包括:模加模块、模减模块、模乘模块;

4、所述状态机控制模块根据外部的信号对当前状态进行转移,并生成转移后的状态、sel选择信号、阶段p、组数k和轮数m;所述状态包括:ntt状态、pwm0状态、pwm1状态和intt状态;

5、所述索引生成模块根据转移后的状态以及sel选择信号、阶段p、组数k和轮数m生成一对索引i、j;

6、所述存储映射模块将一对索引i、j分别映射成一对地址a0、a1和一对bank号b0、b1;

7、所述bank选择模块根据一对bank号b0、b1和一对地址a0、a1进行处理后,得到选择后的地址a0’、a1’;

8、若转移后的状态为ntt状态,则所述ram组根据一对bank号b0、b1和地址a0’、a1’寻址出对应的2d位的数据s2k+1s2k和2d位的数据s2l+1s2l;其中,d表示位宽;

9、所述蝶形输入选择模块将数据s2k+1s2k和数据s2l+1s2l拆分成4个d位的数据s2k+1,数据s2k,数据s2l+1,数据s2l,再将数据s2k+1和数据s2l+1放入第一蝶形单元,将数据s2k和数据s2l放入第二蝶形单元;

10、所述旋转因子地址生成模块根据阶段p和组数k生成相应的旋转因子地址;

11、所述旋转因子rom根据旋转因子地址读出d位的旋转因子wi;

12、对于第一蝶形单元,第一模乘模块将d位的旋转因子wi与d位的数据s2l+1相乘,得到2d位的乘法结果x1=wi×s2l+1,通过查找表和巴雷特约减法对x1进行处理后获得模数为q以内的数据y0;第一模加模块将d位的数据s2k+1和d位的数据y0进行相加后,得到加法结果s2k+1+y0,判断s2k+1+y0是否超过q,若超过,则s2k+1+y0减去q,否则,s2k+1+y0保持不变,从而得到输出结果s’2k+1;第一模减模块将s2k+1与y0进行相减后,得到减法结果s2k+1-y0,并判断s2k+1-y0是否小于0,若小于,则s2k+1-y0加上q,否则,s2k+1-y0保持不变,从而获得模数为q以内的输出结果s’2l+1;

13、对于第二蝶形单元,第二模乘模块将d位的旋转因子wi与d位的数据s2l相乘,得到2d位的乘法结果x0=wi×s2l,通过查找表和巴雷特约减法对x0进行处理后,获得模数为q以内的数据y1;第二模加模块将d位的数据s2k和d位的乘法结果y1进行相加后,得到加法结果s2k+y1,判断s2k+y1是否超过q,若超过,则s2k+y1减去q,否则,s2k+y1保持不变,从而得到输出结果s’2k;第二模减模块将s2k与y1进行相减后,得到减法结果s2k-y1,判断s2k-y1是否小于0,若小于,则s2k-y1加上q,否则,s2k-y1保持不变,从而获得模数为q以内的输出结果s’2l;

14、所述蝶形输出选择模块将4个d位的输出结果s’2k+1,输出结果s’2k,输出结果s’2l+1,输出结果s’2l合并成2d位的数据s’2k+1s’2k和2d位的数据s’2l+1s’2l,并根据一对地址a0、a1和一对bank号b0、b1,将两个2d位的数据s’2k+1’s’2k和数据s’2l+1s’2l存回至ram组;

15、若转移后的状态为pwm0状态,则所述ram组根据一对bank号b0、b1和一对地址a0’、a1’寻址出对应的2d位的数据s2k+1s2k和2d位的数据a2k+1a2k;

16、所述蝶形输入选择模块将2d位的数据s2k+1s2k和2d位的数据a2k+1a2k拆分成4个d位的数据s2k+1,数据s2k,数据a2k+1,数据a2k,再将数据s2k+1,数据s2k,数据a2k+1放入第一蝶形单元,将数据a2k+1,数据a2k,数据s2k放入第二蝶形单元;

17、对于第一蝶形单元,第一模加模块将d位的数据s2k+1和d位的数据s2k进行相加后,得到加法结果s2k+1+s2k,判断s2k+1+s2k是否超过q,若超过,则s2k+1+s2k减去q,否则,s2k+1+s2k保持不变,从而得到模数为q以内的输出结果s’2k;第一模乘模块将d位的数据a2k+1与d位的数据s2k+1相乘,得到2d位的乘法结果x2=a2k+1×s2k+1,通过查找表和巴雷特约减法对x2进行处理,获得模数为q以内的输出结果m2k;

18、对于第二蝶形单元,第二模加模块将d位的数据a2k+1和d位的数据a2k进行相加后,得到加法结果a2k+1+a2k,判断a2k+1+a2k是否超过q,若超过,则a2k+1+a2k减去q,否则,a2k+1+a2k是保持不变,从而得到模数为q以内的输出结果s’2k+1;第二模乘模块将d位的数据a2k与d位的数据s2k相乘,得到2d位的乘法结果x3=a2k×s2k,通过查找表和巴雷特约减法对x3进行处理,获得模数为q以内的输出结果m2k+1;

19、所述蝶形输出选择模块将4个d位的输出结果s’2k+1,输出结果s’2k,输出结果m2k+1,输出结果m2k合并成2d位的数据s’2k+1s’2k和2d位的数据m2k+1m2k,并根据一对地址a0、a1和一对bank号b0、b1将两个2d位的数据s’2k+1s’2k和数据m2k+1m2k存回至ram组;

20、若转移后的状态为pwm1状态,则所述ram组根据一对bank号的b0、b1和地址a0’、a1’寻址出对应的2d位的数据s2k+1s2k和2d位的数据m2k+1m2k;

21、所述旋转因子地址生成模块根据阶段p和组数k生成相应的旋转因子地址;

22、所述旋转因子rom根据旋转因子地址生成的地址读出d位的旋转因子wi;

23、所述蝶形输入选择模块将2d位的数据s2k+1s2k和2d位的数据m2k+1m2k拆分成4个d位的数据s2k+1,数据s2k,数据m2k+1,数据m2k,再将m2k,s2k,s2k+1放入第一蝶形单元,将m2k,m2k+1,wi放入第二蝶形单元;

24、对于第一蝶形单元,第一模乘模块将d位的数据s2k+1与d位的数据s2k进行相乘后,得到2d位的相乘结果x4=s2k+1×s2k,通过查找表和巴雷特约减法x4进行处理,获得模数为q以内的输出结果p1,第一模加模块将m2k与p0进行相加后,得到加法结果m2k+p0,判断m2k+p0是否超过q,若超过,则m2k+p0减去q,否则,m2k+p0保持不变,从而得到模数为q以内的输出结果h2i+1;

25、对于第二蝶形单元,第二模加模块将d位的数据m2k+1与d位的数据m2k进行相加,得到加法结果m2k+1+m2k,判断m2k+1+m2k是否超过q,若超过,则m2k+1+m2减去q,否则,m2k+1+m2保持不变,从而模数为q以内的输出结果r;第二模乘模块将d位的旋转因子wi与d位的m2k+1进行相乘后,得到2d位的乘法结果x5=wi×m2k+1,通过查找表和巴雷特约减法x5进行处理,获得模数为q以内的输出结果p1;第二模减模块将r与p0进行相减后,得减法结果r-p0,判断r-p0是否小于0,若小于,则r-p0是加上q,否则,r-p0是保持不变,从而得到模数为q以内的输出结果h2i;

26、所述蝶形模块将p1与p0进行交互,得到第一蝶形单元输出结果h’2i+1=s2i×s2i+1-(m2i+m2i+1),第二蝶形单元输出结果h’2i=m2i+m2i+1×wi;

27、所述蝶形输出选择模块将蝶形模块的d位的h’2i+1和d位的h’2i合并成一个2d位的数据h’2i+1h’2i,并根据一对地址a0、a1和一对bank号b0、b1,将2d位的数据h’2i+1h’2i存回至ram组;

28、若转移后的状态为intt状态,则所述ram组根据一对bank号b0、b1和地址a0’、a1’寻址出对应的2d位的数据s2k+1s2k和2d位的数据s2l+1s2l;

29、所述蝶形输入选择模块将数据s2k+1s2k和数据s2l+1s2l拆分成4个d位的数据s2k+1,数据s2k,数据s2l+1,数据s2l,再将数据s2k+1,数据s2l+1放入第一蝶形单元,将数据s2k,数据s2l放入第二蝶形单元;

30、所述旋转因子地址生成模块根据阶段p和组数k生成相应的旋转因子地址;

31、所述旋转因子rom根据旋转因子地址读出d位的旋转因子wi;

32、对于第一蝶形单元,第一模加模块将d位的数据s2k+1和d位的数据s2l+1进行相加后,得到加法结果s2k+1+s2l+1,若s2k+1+s2l+1为偶数,则得到结果(s2k+1+s2l+1)/2;若s2k+1+s2l+1为奇数,则判断s2k+1+s2l+1是否超过q,若超过q,则得到结果(s2k+1+s2l+1)/2-f,否则,得到结果(s2k+1+s2l+1)/2+e,从而获得模数为q以内的输出结果s’2k+1;第一模减模块将s2k+1与s2l+1进行相减后,得到减法结果s2k+1-s2l+1,判断s2k+1-s2l+1是否小于0,若小于,则s2k+1-s2l+1加上q,否则,s2k+1-s2l+1保持不变,从而获得模数为q以内的输出结果c2;若c2为奇数,则将c2除以2再加上e,即c2/2+e;若为偶数,则将c2除2,即c2/2,从而获得模数为q以内的输出结果c3;第一模乘模块将d位的旋转因子wi与d位的c3相乘后,得到2d位的乘法结果x6=wi×c3,记为,通过查找表和巴雷特约减法对x6进行处理后,获得模数为q以内的输出结果s’2l+1;

33、对于第二蝶形单元,第二模加模块将d位的s2k和d位的s2l进行相加后,得到加法结果s2k+s2l,若s2k+s2l为偶数,则得到结果(s2k+s2l)/2;若s2k+s2l为奇数,则判断s2k+s2l是否超过q,若超过q,则得到结果(s2k+s2l)/2-f,否则,得到结果(s2k+s2l)/2+e,从而获得模数为q以内的输出结果s’2k+1;第二模减模块将d位的s2k与d位的s2l进行相减后,得到减法结果s2k-s2l,判断s2k-s2l是否小于0,若小于,则s2k-s2l加上q,否则,s2k-s2l保持不变,从而获得模数为q以内的输出结果c0;若为奇数,则将c0除以2再加上e,即c0/2+e;若为偶数,则将c0除以2,即c0/2,从而获得模数为q以内的输出结果c1;第二模乘模块将d位的旋转因子wi与d位的c1相乘,得到2d位的乘法结果x7=wi×c1,通过查找表和巴雷特约减法对x7进行处理后,获得模数为q以内的输出结果s’2l;

34、所述蝶形输出选择模块将4个d位的输出结果s’2k+1,s’2k,s’2l+1,s’2l合并成2d位的数据s’2k+1s’2k和2d位的数据s’2l+1s’2l,并根据一对地址a0、a1和一对bank号b0、b1,将两个2d位的数据s’2k+1s’2k和s’2l+1s’2l存回至ram组。

35、本发明所述的用于面向后量子加密kyber方案的ntt多项式乘法器的硬件电路的特点也在于,查找表和巴雷特约减法是按如下步骤获得模数为q以内的数据y0:

36、步骤1、利用式(1)计算固定值v,从而得到固定值2v,固定值3v,并一起储存在查找表中;

37、

38、步骤2、将2d位的数据x1拆成d个两位的数据xd-1,xd-2,…,x0;其中,xd-2表示第2个两位的数据;

39、步骤3、将xd-1,xd-2…x0分别与v相乘,并根据查找表的3个固定值v,2v,3v,从而得到d个不同的数据x’d-1,x’d-2…x’0;其中,x’d-2表示第d-2个固定值;

40、步骤4、将数据x’d-1,x’d-3…x’1左移d/6位后,与数据x’d-2,x’d-4…x’0对应相加,得到d/4个加法结果yd/2-1,yd/2-2…y0;其中yd/2-2表示第二个加法结果;

41、步骤5、将第1个加法结果yd/2-1,第3个加法结果yd/2-3,第d/4-1个加法结果y1左移d/3位,与第2个加法结果yd/2-2,第4个加法结果yd/2-4,第d/4个加法结果y0对应相加,得到新的第1个加法结果y’d/4-1,新的第2个加法结果y’d/4-2,新的第d/8个加法结果y’0;

42、步骤6、将新的第2个加法结果y’d/4-2左移2d/3位后,与新的第d/8个加法结果y’0相加,得到数据z0;

43、步骤7、将新的第1个加法结果y’d/4-1左移4d/3位后,与数据z0相加,得到结果z1;并完成2d位的x1与v的乘法运算;

44、步骤8、将结果z1右移2d位,得到数据z2;

45、步骤9、根据模q的特性,将数据z2分别左移a,b,c位,得到数据z3,数据z4,数据z5,然后,将数据z2,数据z3,数据z4,数据z5相加,得到结果t;从而利用式(2)完成z2与q的乘法运算;

46、q=2a+2b+2c+1 (2)

47、式(2)中,a,b,c表示左移的位数;

48、步骤10、将数据x1与结果t进行相减,从而得到减法结果u=x1-t;

49、步骤11、将减法结果u与模q进行相减,从而得到减法结果v=u-q;

50、步骤12、判断减法结果v是否大于等于0,若是,则令v赋值给y0,否则,令u赋值给y0。

51、与现有技术相比,本发明的有益技术效果体现在:

52、1、本发明设计了一个资源高效的基于查找表方式的巴雷特约简电路。该方式相比经典的巴雷特约简电路可以节省两个dsp资源,从而减少了整体电路的资源消耗。

53、2、本发明针对intt过程中除n操作需要消耗额外的运算周期,设计了一个融合除2操作的模加和模减电路。这保证在牺牲较少资源的前提下,可以从理论上减少运算周期。

54、3、本发明设计了一个可配置、具有交互端口的紧凑型蝶形单元。在ntt和intt时,两个蝶形单元独立并行运算;在多项式乘法时,两个蝶形单元通过交互端口完成数据交互,比其他两个蝶形单元而言,多项式乘法可以减少运算周期,从而提高了整体电路的运算速度。

- 还没有人留言评论。精彩留言会获得点赞!