一种集成电路设计优化布线方法、电子设备及存储介质与流程

本发明涉及集成电路设计,特别涉及一种集成电路设计优化布线方法、电子设备及存储介质。

背景技术:

1、引脚是一种电气端子,用于将给定元件与其外部环境连接起来,在超大规模集成电路芯片设计中,引脚有供电、输入和输出等多种类别,其主要功能是实现各个元件的信息输入和输出,在超大规模集成电路芯片设计的过程中,布线起着关键作用,它的任务是通过线和过孔将每个网络的各个引脚连接起来,从而连接各个元件。

2、与此同时,布线的结果必须满足设计规则的约束,设计规则是由集成电路芯片的制造厂商在不同先进工艺技术节点下,对光刻过程中大概率会失败的图形规则的总结。因此,集成电路芯片的设计方需要遵守设计规则,在设计过程中避免设计规则违例,在设计交付时解决设计规则违例,以保证设计的可制造性。

3、而在超大规模集成电路芯片设计过程中,布线时容易因为接入引脚的方式不合理,造成布线结果不佳甚至剩余设计规则违例无法处理。

技术实现思路

1、为解决超大规模集成电路设计中的布线容易因为接入引脚的方式不合理,造成布线结果不佳甚至剩余设计规则违例无法处理的技术问题,本发明提供了一种集成电路设计优化布线方法、电子设备及存储介质。

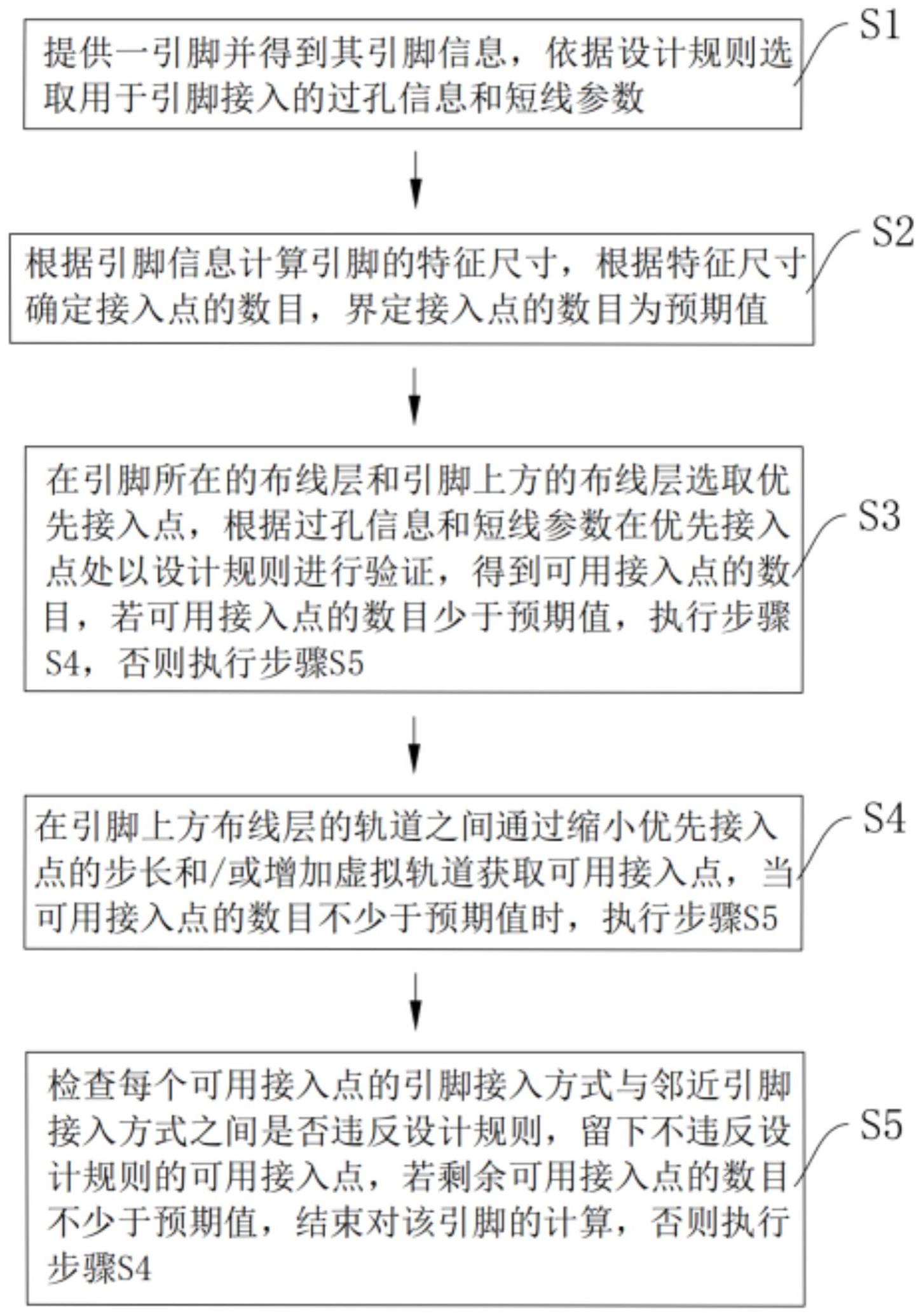

2、本发明解决技术问题的方案是提供一种集成电路设计优化布线方法,应用于超大规模集成电路设计,包括以下步骤:

3、s1:提供一引脚并得到其引脚信息,依据设计规则选取用于引脚接入的过孔信息和短线参数;

4、s2:根据引脚信息计算引脚的特征尺寸,根据特征尺寸确定接入点的数目,界定接入点的数目为预期值;

5、s3:在引脚所在的布线层和引脚上方的布线层选取优先接入点,根据过孔信息和短线参数在所述优先接入点处以设计规则进行验证,得到可用接入点的数目,若所述可用接入点的数目少于所述预期值,执行步骤s4,否则执行步骤s5;

6、s4:在引脚上方布线层的轨道之间通过缩小优先接入点的步长和/或增加虚拟轨道获取所述可用接入点,当所述可用接入点的数目不少于所述预期值时,执行步骤s5;

7、s5:检查每个所述可用接入点的引脚接入方式与邻近引脚接入方式之间是否违反设计规则,留下不违反设计规则的可用接入点,若剩余所述可用接入点的数目不少于所述预期值,结束对该引脚的计算,否则执行步骤s4。

8、优选地,在步骤s5中结束对引脚的计算后,执行以下步骤:

9、s6:若剩余所述可用接入点的数目不少于所述预期值,继续返回步骤s1执行下一引脚的计算,直至完成对所有引脚的计算后,输出符合设计规则的接入点和引脚接入方式。

10、优选地,步骤s3中选取优先接入点具体包括以下步骤:

11、s31a:获取引脚及引脚上方的布线层,界定引脚所在的布线层为mx、引脚上方的布线层依次为mx+1,mx+2;

12、s31b:在引脚与mx+1的轨道交线上,以交线的中点为起始点、mx+2的轨道间距为步长选取优先接入点。

13、优选地,步骤s4中,交替执行缩小步长及增加虚拟轨道两个动作,在执行缩小步长或增加虚拟轨道后,计算所述可用接入点的数目。

14、优选地,通过增加虚拟轨道获取可用接入点,需要经过以下步骤:

15、第一次增加虚拟轨道时,取与mx+1的实际轨道平行、与相邻实际轨道距离为mx+1层轨道间距的的平行线为虚拟轨道;

16、第n次(n>1)增加的虚拟轨道,其与实际轨道之间的间距缩小为第n-1次增加的虚拟轨道和实际轨道之间的间距的。

17、优选地,步骤s5中,将不违反设计规则的可用接入点所对应的引脚接入方式加入一备选集,所述备选集内包括每个引脚接入方式的接入成本。

18、优选地,步骤s2中,所述特征尺寸包括所述引脚的宽度和/或面积。

19、优选地,每个引脚需要的接入点数目至少为2个。

20、本发明还提供一种电子设备,包括处理器、存储介质和总线,所述存储介质存储有所述处理器可执行的程序指令;

21、当所述电子设备运行时,所述处理器与所述存储介质之间通过所述总线通信,所述处理器执行所述程序指令实现上述的集成电路设计优化布线方法。

22、本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序在被处理器运行时实现上述的集成电路设计优化布线方法。

23、与现有技术相比,本发明提供的一种集成电路设计优化布线方法、电子设备及存储介质,具有以下优点:

24、1、本发明实施例提供的集成电路设计优化布线方法,应用于超大规模集成电路设计,包括以下步骤:s1:提供一引脚并得到其引脚信息,依据设计规则选取用于引脚接入的过孔信息和短线参数;s2:根据引脚信息计算引脚的特征尺寸,根据特征尺寸确定接入点的数目,界定接入点的数目为预期值;s3:在引脚所在的布线层和引脚上方的布线层选取优先接入点,根据过孔信息和短线参数在优先接入点处以设计规则进行验证,得到可用接入点的数目,若可用接入点的数目少于预期值,执行步骤s4,否则执行步骤s5;s4:在引脚上方布线层的轨道之间通过缩小优先接入点的步长和/或增加虚拟轨道获取可用接入点,当可用接入点的数目不少于预期值时,执行步骤s5;s5:检查每个可用接入点的引脚接入方式与邻近引脚接入方式之间是否违反设计规则,留下不违反设计规则的可用接入点,若剩余可用接入点的数目不少于预期值,结束对该引脚的计算,否则执行步骤s4。

25、需要说明的是,在超大规模集成电路芯片设计过程中,布线的结果必须满足设计规则的约束,对此,本发明提供了一种对于无论是否在网格上的引脚都适用的、符合设计规则要求的引脚接入方案,并通过这种引脚接入方案优化了布线结果。

26、可以理解,本发明通过在布线之前,计算引脚符合设计规则的接入点和接入方式,来给详细布线时接入引脚提供指导,解决了超大规模集成电路设计中的布线容易因为接入引脚的方式不合理,造成布线结果不佳甚至剩余设计规则违例无法处理的技术问题。

27、进一步可以理解,通过此设计,在遵循设计规则的前提下,对于不论是否在网格上的引脚,都提供了合适的接入方案,加快了详细布线中设计规则违例的收敛速度、优化了布线结果。

28、2、本发明实施例提供的集成电路设计优化布线方法,在步骤s5中结束对引脚的计算后,执行以下步骤:s6:若剩余可用接入点的数目不少于预期值,继续返回步骤s1执行下一引脚的计算,直至完成对所有引脚的计算后,输出符合设计规则的接入点和引脚接入方式。可以理解地,当可用接入点的数目足够多时,结束对该引脚的计算,转而执行对下一引脚的计算,直至完成所有引脚的计算再输出接入点和引脚接入方式。

29、3、本发明实施例提供的集成电路设计优化布线方法,步骤s3中选取优先接入点具体包括以下步骤:s31a:获取引脚及引脚上方的布线层,界定引脚所在的布线层为mx、引脚上方的布线层依次为mx+1,mx+2;s31b:在引脚与mx+1的轨道交线上,以交线的中点为起始点、mx+2的轨道间距为步长选取优先接入点。

30、需要说明的是,在超大规模集成电路芯片设计中,布线层mx和上一层布线层mx+1的轨道是相互垂直的,所以布线层mx+1的轨道和布线层mx的轨道,在从上向下投影到同一个平面内时会有多个交点,这些交点称为布线层mx的网格点。

31、可以理解地,优先接入点的选取只与mx+1的轨道和引脚的交线有关,与mx的轨道无关,所以不受引脚是否在网格上的影响。

32、4、本发明实施例提供的集成电路设计优化布线方法,步骤s4中,交替执行缩小步长及增加虚拟轨道两个动作,在执行缩小步长或增加虚拟轨道后,计算可用接入点的数目。

33、可以理解地,在每执行完缩小步长和增加虚拟轨道中的任意一个操作后,就计算可用接入点的数目,当可用接入点的数目大于等于预期值时执行步骤s5,否则继续交替执行缩小步长及增加虚拟轨道两个动作。

34、需要说明的是,缩小步长是将步长缩小为原先的一半,这样的操作最多执行到步长为最开始的优先接入点步长(即mx+2层的轨道间距)的,若所得到的可用接入点还不够多,则会尝试直接将步长缩小为最开始的以进行最后一次尝试。

35、5、本发明实施例提供的集成电路设计优化布线方法,通过增加虚拟轨道获取可用接入点,需要经过以下步骤:第一次增加虚拟轨道时,取与mx+1的实际轨道平行、与相邻实际轨道距离为mx+1层轨道间距的的平行线为虚拟轨道;第n次(n>1)增加的虚拟轨道,其与实际轨道之间的间距缩小为第n-1次增加的虚拟轨道和实际轨道之间的间距的。

36、需要说明的是,这样的操作最多执行到虚拟轨道的间距为mx+1层轨道间距的,若所得到的可用接入点还不够多,则会尝试直接将虚拟轨道的间距缩小为最开始的以进行最后一次尝试。

37、6、本发明实施例提供的集成电路设计优化布线方法,步骤s5中,将不违反设计规则的可用接入点所对应的引脚接入方式加入一备选集,备选集内包括每个引脚接入方式的接入成本。

38、可以理解地,对可用接入点的检查主要是接入引脚的过孔或短线与标准单元里本身存在的结构之间是否存在设计规则违例,通过此设计,可以减少选出的接入方式违反设计规则的可能性。

39、需要说明的是,接入成本是通过人为计算的、为引脚的各种接入方式所加的一个属性,用以在后续布线中接入这个引脚时,确定尝试各种接入方式的顺序,在布线时会优先选择接入成本较低的接入方式。

40、7、本发明实施例提供的集成电路设计优化布线方法,步骤s2中,特征尺寸包括引脚的宽度和/或面积;每个引脚需要的接入点数目至少为2个。需要说明的是,通过引脚的宽度或面积,或者引脚的宽度和面积综合考虑,可以确定每个引脚至少需要的接入点数目,一般来说,每个引脚至少需要两个接入点,面积较大的引脚所需要的接入点数目相对会更多。

41、8、本发明实施例还提供一种电子设备,包括处理器、存储介质和总线,存储介质存储有处理器可执行的程序指令;当电子设备运行时,处理器与存储介质之间通过总线通信,处理器执行程序指令实现上述的集成电路设计优化布线方法。

42、该电子设备具有与上述的集成电路设计优化布线方法相同的有益效果,在此不再赘述。

43、9、本发明实施例还提供一种计算机可读存储介质,其上存储有计算机程序,计算机程序在被处理器运行时实现上述的集成电路设计优化布线方法。

44、该计算机可读存储介质具有与上述的集成电路设计优化布线方法相同的有益效果,在此不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!