一种高兼容性并行ADC数据采集与传输系统

本发明属于高速数据采集领域,涉及一种高兼容性并行adc数据采集与传输系统。

背景技术:

1、随着社会的发展以及科技的进步,传统的数据采集、数据传输设备已经不能满足企业的生产要求。传统的并行总线采集系统已无法满足当前高速数据采集系统的传输需求。特别是工业控制领域,高速度、高效率、高稳定的数据采集传输系统成为了不可或缺的部分。

2、为了满足高速度、高效率、高稳定性的数据传输的要求,串行总线技术被运用到数据采集系统中,pcie总线技术与工业控制设备相结合,突破了工业控制设备总线接口的传输速度瓶颈。在采集系统研发过程中,研发人员需要根据系统需求进行芯片选型,使用最低的成本完成系统功能设计;采集系统从数据采集到将数据上传至上位机的过程也较为复杂,开发难度较大,因此开发一种高兼容性并行adc数据采集与传输系统,能够大大降低采集系统的开发难度并缩短研发周期。

3、目前常见的数据采集相关可直接移植的系统多为ddr存储与pcie总线结合,用户接口较为复杂,开发人员还需编写逻辑程序将其与adc芯片接口对接;常见的采集系统包含了采集、存储、传输的过程,但只能用于固定的采集平台;普通的多通道采集系统,内部常用的掩码方式会产生无用位,影响传输总线传输效率;本发明提供了一种用户接口简单、移植性强、兼容性好的并行adc数据采集与传输系统,系统可根据具体的adc采集型号设置多路单通道采集或时间交织采集,内部数据处理模块提出了一种240/256位编码方式,与传统掩码方式不同,240/256编码在兼容各类型并行adc的同时不会产生无用数据位,提高了总线传输效率。

技术实现思路

1、本发明的目的在于提供一种高兼容性并行adc数据采集与传输系统,旨在解决高速数据采集系统开发难度大,系统更换不同位数的adc芯片后逻辑程序同步更新过程繁琐,多路数据交织采集系统中传输总线带宽利用率低的问题。

2、为了实现上述目的,本发明提供了一种高兼容性并行adc数据采集与传输系统,包括数据处理模块、时钟控制器、ddr控制器、pcie控制器、报文解析模块。

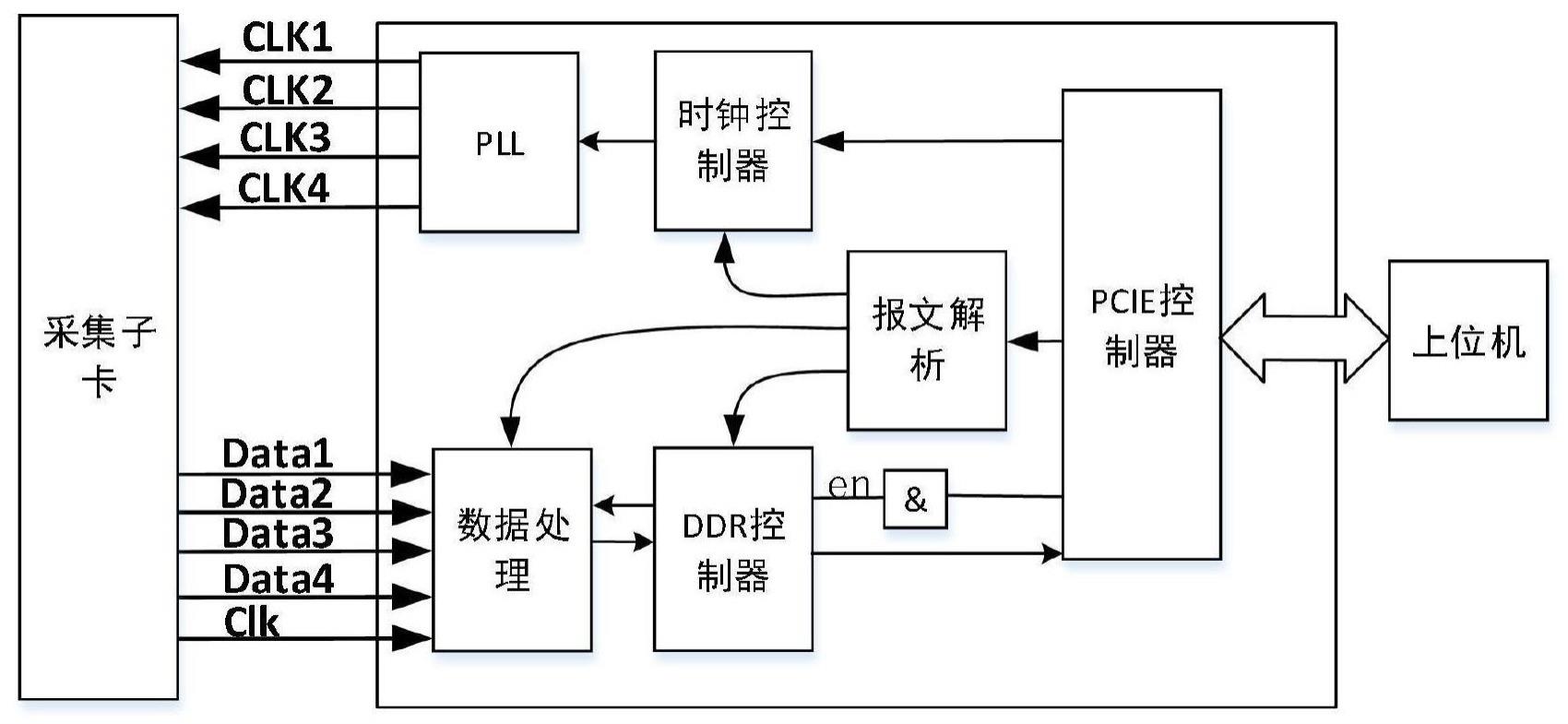

3、所述时钟控制器、数据处理模块、ddr控制器、pcie控制器、报文解析模块之间的连接方式如图1所示。

4、所述时钟控制器结构如图2所示,根据系统外部adc芯片数量、采样率、采样模式得到系统输出时钟所需的的相位与速率,使用动态锁相环技术完成系统输出时钟的动态控制,以满足系统时钟需求。

5、进一步的,如图3所示,所述动态锁相环技术通过drp接口对mcmm锁相环的寄存器组写命令字完成锁相环输出时钟的控制。

6、所述寄存器组包括:divider与phase,改变divider寄存器组中的high time与lowtime参数,可改变锁相环的分频系数实现对输出时钟的速率控制;改变phase寄存器组中的phase mux与delay time参数,可改变输出时钟的初始相位、输出延时,实现输出时钟的相位粗调与细调。

7、所述数据处理模块如图4所示,包括数据接收单元、数据编码单元;所述数据接收单元用于获取外部adc的采集数据,并把所述数据传输给所述数据编码单元;所述数据编码单元接收数据后,采用所述240/256位编码方式对所述数据包编码得到数据包,编码完成后将所述数据包传输至ddr控制器。

8、具体的,所述240/256位编码的数据帧格式如图5所示,前240位为数据位,后16位为数据帧校验位,所述校验位用于数据帧误码检验。

9、所述240/256位编码方式,利用了240为常见adc位数8、10、12、16、24的最小公倍数,因此在数据拼接过程中不会产生无用位,提高了系统传输总线带宽的利用率。

10、优选的,误码检验的实现算法选用crc校验算法。

11、优选的,选择crc-16/usb模型作为校验模型。

12、所述ddr控制器如图6所示,当ddr控制器接收到所述数据处理模块的编码数据后,将所述数据先后顺序存储。

13、所述pcie控制器如图8所示pcie控制器接收到上位机下发的数据发送命令后,发送上传命令至所述ddr控制器,获取编码数据,再从ddr存储器获取所述数据并上传至上位机。

14、本发明的发明点在于:提供了一种针对并行adc的高兼容性数据采集与传输系统,解决高速数据采集系统开发难度大、系统更换不同位数的adc芯片后逻辑程序同步更新过程繁琐的问题;在数据处理模块中提出了一种240/256位编码方式,与传统掩码方式相比,在保留了系统兼容性的同时,解决了会产生无用数据位,占用总线带宽的问题。

15、所述报文解析模块从pcie控制器获取报文数据,与上位机约定好报文协议后,根据报文协议分析报文数据,控制对应模块执行报文指令。

16、所述系统通过上述步骤,实现了能够兼容各类型号的并行adc芯片的功能,仅需设置所述芯片的位数、数量即可完成数据的采集与传输过程的功能。

技术特征:

1.一种高兼容性并行adc数据采集与传输系统,其特征在于,系统包括,时钟控制器、数据处理模块、ddr控制器、pcie控制器、报文解析模块;

2.如权利要求1所述的一种高兼容性并行adc数据采集与传输系统,其特征在于,所述时钟控制器根据系统外部adc芯片数量、采样率、采样模式得到系统输出时钟所需的的相位与速率,使用动态锁相环技术完成系统输出时钟的动态控制,以满足系统时钟需求。

3.如权利要求2所述的一种高兼容性并行adc数据采集与传输系统,其特征在于,所述动态锁相环技术通过drp接口对mcmm锁相环的寄存器写命令字完成锁相环输出时钟的控制,所述寄存器包括:divider与phase两个寄存器组,改变divider寄存器组中的high time与low time参数,实现对输出时钟的速率控制;改变phase寄存器组中的phase mux与delaytime参数,实现输出时钟的相位粗调与细调。

4.如权利要求1所述的一种高兼容性并行adc数据采集与传输系统,其特征在于,所述数据处理模块包括数据接收单元、数据编码单元。所述数据接收单元获取外部adc的采集数据传输给所述数据编码单元;所述数据编码单元采用240/256位编码方式对数据进行编码得到数据包。

5.如权利要求4所述的一种高兼容性并行adc数据采集与传输系统,其特征在于,所述240/256编码的数据帧位宽为256位,前240位为数据位,后16位为校验位。

技术总结

本发明提供的是一种高兼容性并行ADC数据采集与传输系统,系统包括:时钟控制器、数据处理模块、DDR控制器、PCIe控制器、报文解析模块;所述时钟控制器根据ADC挂载数量、采样率、采集模式等信息输出不同频率与相位的时钟;所述数据处理模块负责接收数据,并通过240/256位编码方式提高了传输总线带宽利用率;所述DDR控制器负责缓存处理后的数据;所述PCIe控制器负责接收报文并上传采集数据;所述报文解析模块负责解析报文。本发明内部采用240/256位编码方式避免了数据拼接过程中产生无效位的问题,提高了总线传输效率;同时本发明可应用于各型号并行ADC采集系统且无需更改内部逻辑,减小了采集系统开发难度,缩短了系统开发周期。

技术研发人员:许川佩,杨洪,施秀丽,邓运辉,张玉成

受保护的技术使用者:桂林电子科技大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!